28. Programmierung des Speichers

28.1 Sperrbits für Programm- und Datenspeicher

Der ATmega48 hat zwei, der ATmega88/168/328 sechs Sperrbits, die unprogrammiert, also 1, bleiben können

oder mit einer 0 programmiert werden können, um die gewünschten zusätzlichen Funktionen zu nutzen,

siehe Tabelle 28-2.

Die Sperrbits können nur mit dem Chip-Lösch-Befehl gelöscht werden.

Der ATmega48 hat keinen separaten Urlader-Bereich,

und der SPM-Befehl kann den gesamten Flash-Speicher verändern,

wenn die SELFPRGEN-Fuse programmiert (= 0) ist.

Andernfalls ist der SPM-Befehl wirkungslos.

Tabelle 28-1: Sperrbit-Byte(1)

| Sperrbit-Name | Bitnummer | Beschreibung | Vorgabe

|

|---|

| 7 | – | 1 (unprogrammiert)

|

| 6 | – | 1 (unprogrammiert)

|

BLB12(2)| 5 | Urlader-Sperrbit | 1 (unprogrammiert)

| BLB11(2)| 4 | Urlader-Sperrbit | 1 (unprogrammiert)

| BLB02(2)| 3 | Urlader-Sperrbit | 1 (unprogrammiert)

| BLB01(2)| 2 | Urlader-Sperrbit | 1 (unprogrammiert)

| | LB2 | 1 | Sperrbit | 1 (unprogrammiert)

| | LB1 | 0 | Sperrbit | 1 (unprogrammiert)

| | | | |

- Hinweise:

- „1“ bedeutet unprogrammiert, „0“ bedeutet programmiert

- Nur bei ATmega88/168/328

Tabelle 28-2: Sperrbit-Schutzmodi(1)(2)

- Hinweise:

- Die Fuse-Bits und Urlader-Sperrbits müssen vor dem Programmieren der Sperrbits LB1 und LB2 programmiert werden.

- „1“ bedeutet unprogrammiert, „0“ bedeutet programmiert

Urlader-Sperrbits regeln den Speicherschutz beim kreuzweisen Zugriff zwischen Anwender- und Urlader-Bereich.

Beachte, dass die Größe des Urlader-Bereichs festliegt, während die Größe des Urladers —

manifestiert durch die Lage des Reset- und der Interruptvektoren —

kleiner ausfallen darf und mittels Fuse-Bits programmiert werden kann.

Tabelle 28-3: Urlader-Sperrbit-Schutzmodi(1)(2) — Nur ATmega88/168/328

| BLB0-Modus | BLB02 | BLB01 |

|

|---|

| 1 | 1 | 1 | Keine Einschränkungen für SPM und LPM beim Zugriff auf den Anwenderbereich

|

| 2 | 1 | 0 | Schreibschutz: SPM ist nicht erlaubt, in den Anwenderbereich zu schreiben

|

| 3 | 0 | 0 | Vollschutz: SPM ist nicht erlaubt, in den Anwenderbereich zu schreiben

und LPM ist nicht erlaubt aus dem Applikationssktor zu lesen,

wenn LPM aus dem Urlader-Bereich ausgeführt wird.

Wenn die Interruptvektoren in den Urlader-Bereich gelegt wurden, sind die Interrupts gesperrt,

wenn sie aus dem Anwenderbereich ausgeführt werden.

|

| 4 | 0 | 1 | Kopierschutz: LPM ist nicht erlaubt aus dem Applikationssktor zu lesen,

wenn LPM aus dem Urlader-Bereich ausgeführt wird.

Wenn die Interruptvektoren in den Urlader-Bereich gelegt wurden, sind die Interrupts gesperrt,

wenn sie aus dem Anwenderbereich ausgeführt werden.

|

| BLB1-Modus | BLB12 | BLB11 |

|

|---|

| 1 | 1 | 1 | Keine Einschränkungen für SPM und LPM beim Zugriff auf den Urlader-Bereich.

|

| 2 | 1 | 0 | Schreibschutz: SPM ist nicht erlaubt, in den Urlader-Bereich zu schreiben

|

| 3 | 0 | 0 | Vollschutz: SPM ist nicht erlaubt, in den Urlader-Bereich zu schreiben

und LPM ist nicht erlaubt aus dem Urlader-Bereich zu lesen,

wenn LPM aus dem Anwenderbereich ausgeführt wird.

Wenn die Interruptvektoren in den Anwenderbereich gelegt wurden, sind die Interrupts gesperrt,

wenn sie aus dem Urlader-Bereich ausgeführt werden.

|

| 4 | 0 | 1 | Kopierschutz: LPM ist nicht erlaubt aus dem Urlader-Bereich zu lesen,

wenn LPM aus dem Anwenderbereich ausgeführt wird.

Wenn die Interruptvektoren in den Anwenderbereich gelegt wurden, sind die Interrupts gesperrt,

wenn sie aus dem Urlader-Bereich ausgeführt werden.

|

- Hinweise:

- Die Fuse-Bits und Urlader-Sperrbits müssen vor dem Programmieren der Sperrbits LB1 und LB2 programmiert werden.

- „1“ bedeutet unprogrammiert, „0“ bedeutet programmiert

28.2 Fuse-Bits

Fuse bedeutet Schmelzsicherung.

In der Anfangszeit der programmierbaren Schaltkreisentwicklung

wurden die Daten tatsächlich durch Durchbrennen von Metallisierungen eingebracht.

Heutzutage erledigt dies eine elektrisch löschbare Floating-Gate-Speicherzelle.

Eine Fuse im AVR-Kontext ist ein Steuerbit, welches außerhalb des Programmspeichers liegt

und bestimmte Eigenschaften bereits vor dem Ausführen von Programmkode festlegt.

Der Schaltkreis hat drei Fuse-Bytes.

Die nachfolgenden Tabellen geben einen kurzen Überblick

über die Funktion der Fuse Bits und deren Lage innerhalb der Fuse-Bytes.

Man beachte, dass Fuse Bits, die programmiert sind als logisch 0 gelesen werden.

Tabelle 28-4: Erweitertes Fuse-Byte — ATmega48

| Erweitertes Fuse-Bit | Bitnummer | Beschreibung | Vorgabe

|

|---|

| – | 7 | – | 1

|

| – | 6 | – | 1

|

| – | 5 | – | 1

|

| – | 4 | – | 1

|

| – | 3 | – | 1

|

| – | 2 | – | 1

|

| – | 1 | – | 1

|

| SELFPRGEN | 0 | Freigabe der Selbstprogrammierung | 1 (unprogrammiert)

|

Tabelle 28-5: Erweitertes Fuse-Byte — ATmega88/168

- Hinweis:

- Die Vorgabe für BOOTSZ[1:0] führt zur maximalen Größe des Urladers.

Tabelle 28-6: Erweitertes Fuse-Byte — ATmega328

| Erweitertes Fuse-Bit | Bitnummer | Beschreibung | Vorgabe

|

|---|

| – | 7 | – | 1

|

| – | 6 | – | 1

|

| – | 5 | – | 1

|

| – | 4 | – | 1

|

| – | 3 | – | 1

|

BODLEVEL2(1)| 2

| Auslöseschwelle des Unterspannungsdetektors

| 1 (unprogrammiert)

| BODLEVEL1(1)| 1

| 1 (unprogrammiert)

| BODLEVEL0(1)| 0 | 1 (unprogrammiert)

| | | |

- Hinweis:

- Siehe Tabelle 29-12 für die Wertzuweisung an BODLEVEL

Tabelle 28-7: High-Fuse-Byte — ATmega48/88/168

| High-Fuse-Bit | Bitnummer | Beschreibung | Vorgabe

|

|---|

RSTDISBL(1)| 7 | Deaktivierung externes Reset | 1 (unprogrammiert)

| | DWEN | 6 | Freigabe von debugWIRE | 1 (unprogrammiert)

| SPIEN(2)| 5 | Freigabe der seriellen Programmierung | 0 (programmiert, SPI-Programmierung möglich)

| WDTON(3)| 4 | Watchdog immer ein | 1 (unprogrammiert)

| | EESAVE | 3 | EEPROM-Speicher beim Chip-Löschen erhalten | 1 (unprogrammiert), EEPROM wird gelöscht

| BODLEVEL2(41)| 2

| Auslöseschwelle des Unterspannungsdetektors

| 1 (unprogrammiert)

| BODLEVEL1(4)| 1

| 1 (unprogrammiert)

| BODLEVEL0(4)| 0 | 1 (unprogrammiert)

| | | | | | |

- Hinweise:

- Siehe Alternative Funktionen von Port C zur Beschreibung der RSTDISBL-Fuse

- Die SPIEN-Fuse ist bei serieller Programmierung nicht erreichbar.

- Siehe WDTCR — Watchdog-Zeitgeber-Kontrolle für Details

- Siehe Tabelle 29-12 für die Wertzuweisung an BODLEVEL

Tabelle 28-9: Low-Fuse-Byte

- Hinweise:

- Die Vorgabe von SUT[1:0] führt zur maximalen Hochlaufzeit der vorgegebenen Taktquelle (RC-Oszillator).

Siehe Tabelle 9-12

- Die Vorgabe von CKSEL[3:0] führt zum internen RC-Oszillator mit 8 MHz.

Siehe Tabelle 9-11

- Die CKOUT-Fuse legt den Systemtakt auf PORTB0.

Siehe Taktausgabepuffer

- Siehe Systemtakt-Vorteiler

Der Zustand der Fuse-Bits wird durch einen Chip-Lösch-Befehl nicht verändert.

Man beachte, dass alle Fuse-Bits blockiert sind, wenn das Sperrbit 1 (LB1) programmiert ist.

Daher müssen die Fuse-Bits programmiert werden, bevor die Sperrbits programmiert werden.

28.2.1 Zwischenspeichern der Fuses

Der Wert der Fuses wird beim Eintreten in einen Programmiermodus zwischengespeichert.

Änderungen an den Fuses wirken sich erst dann aus, wenn der Programmiermodus wieder verlassen wird.

Dies gilt allerdings nicht für die EESAVE-Fuse, die sich auswirkt, sobald sie programmiert wird.

Die Fuses werden auch beim Hochfahren im normalen Modus zwischengespeichert.

28.3 Signatur-Bytes

Alle Atmel-Mikrocontroller haben einen drei Byte langen Signatur-Code,

der die Schaltkreis identifiziert.

Dieser Code kann sowohl im seriellen als auch im parallelen Modus

ausgelesen werden, selbst dann, wenn der Schaltkreis insgesamt gesperrt ist.

Diese drei Bytes sind in einem separaten Adressraum untergebracht.

Siehe folgende Tabelle.

Tabelle 28-10: Schaltkreis-ID

| Schaltkreis | Adresse des Signatur-Bytes

|

|---|

0x000

(Hersteller) | 0x001

(Flash-Größe) | 0x002

(lfd. Nummer)

| ATmega48A | 0x1E | 0x92 | 0x05

| | ATmega48PA | 0x1E | 0x92 | 0x0A

| | ATmega88A | 0x1E | 0x93 | 0x0A

| | ATmega88PA | 0x1E | 0x93 | 0x0F

| | ATmega168A | 0x1E | 0x94 | 0x06

| | ATmega168PA | 0x1E | 0x94 | 0x0B

| | ATmega328 | 0x1E | 0x95 | 0x14

| | ATmega328P | 0x1E | 0x95 | 0x0F

| |

|---|

28.4 Kalibrier-Byte

Der Schaltkreis beinhaltet einen Kalibrierwert für den internen RC-Oszillator.

Dieses Byte ist im oberen Byte der ersten Signatur-Bytes an der Adresse 0x000 abgelegt.

Bei Reset wird der Wert automatisch in das OSCCAL-Register geschrieben.

28.5 Seitengröße

Tabelle 28-11: Anzahl 16-Bit-Worte pro Seite und Anzahl Seiten im Flash-Speicher

| Schaltkreis | Flash-Größe | Seitengröße | PCWORD | Anzahl Seiten | PCPAGE | PCMSB

|

|---|

| ATmega48A | 2 KWord

(4 KByte) | 32 Word | PC[4:0] | 64 | PC[10:5] | 10

|

| ATmega48PA

|

| ATmega88A | 4 KWord

(8 KByte) | 128 | PC[11:5] | 11

|

| ATmega88PA

|

| ATmega168A | 8 KWord

(16 KByte) | 64 Word | PC[5:0] | PC[12:6] | 12

|

| ATmega168PA

|

| ATmega328 | 16 KWord

(32 KByte) | 256 | PC[13:6] | 13

|

| ATmega328P

|

Tabelle 28-12: Anzahl 16-Bit-Worte pro Seite und Anzahl Seiten im EEPROM-Speicher

| Schaltkreis | EEPROM-Größe | Seitengröße | PCWORD | Anzahl Seiten | PCPAGE | EEAMSB

|

|---|

| ATmega48A | 256 Byte | 4 Byte | EEA[1:0] | 64 | EEA[7:2] | 7

|

| ATmega48PA

|

| ATmega88A | 512 Byte | 128 | EEA[8:2] | 8

|

| ATmega88PA

|

| ATmega168A

|

| ATmega168PA

|

| ATmega328 | 1 KByte | 256 | EEA[9:2] | 9

|

| ATmega328P

|

28.6 Parallele Programmierung

Nachfolgend wird beschrieben, wie der Flash, der EEPROM, die Sperr- und Fuse-Bits programmiert werden.

Dabei wird vorausgesetzt, dass sämtliche Pulse mindestens 250 ns lang sind, wenn nichts anderes angegeben ist.

28.6.1 Signalnamen

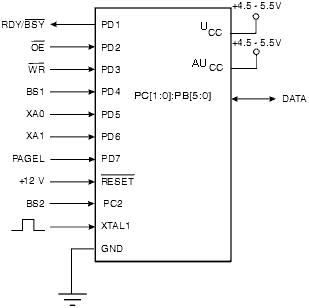

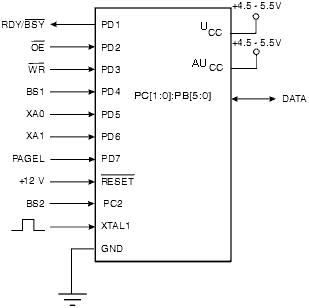

In this section, some pins of the ATmegaX8 are referenced by signal names

describing their functionality during parallel programming, see Figure 28-1 and Table 28-13.

Pins not described in the following table are referenced by pin names.

The XA1/XA0 pins determine the action executed when the XTAL1 pin is given a positive pulse. The bit coding

is shown in Table 28-15.

When pulsing WR or OE, the command loaded determines the action executed.

The different Commands are shown in Table 28-16.

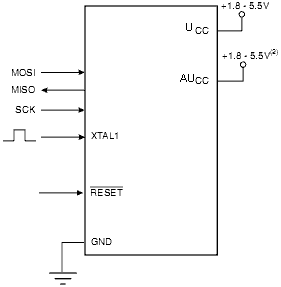

Bild 28-1: Parallele Programmierung

- Hinweis:

- UCC - 0,3 V < AUCC < UCC + 0,3 V,

allerdings sollte AUCC im Bereich 4,5 - 5,5 V liegen

Tabelle 28-13: Pinzuordnung

| Signalname im Programmiermodus | Pin-Name | I/O | Funktion

|

|---|

| RDY/BSY | PD1 | O | 0: Schaltkreis beschäftigt mit Programmierung,

1: Schaltkreis bereit für neues Kommando

|

| OE | PD2 | I | Ausgangs-Freigabe (low-aktiv)

|

| WR | PD3 | I | Schreibimpuls (low-aktiv)

|

| BS1 | PD4 | I | Byte-Auswahl 1 (0 = Low-Byte, 1 = High-Byte)

|

| XA0 | PD5 | I | Quarz-Aktionsbit 0

|

| XA1 | PD6 | I | Quarz-Aktionsbit 1

|

| PAGEL | PD7 | I | Programmspeicher- und EEPROM-Speicher laden

|

| BS2 | PC2 | I | Byte-Auswahl 2 (0 = Low-Byte, 1 = zweites High-Byte)

|

| DATA | {PC[1:0]:PB[5:0]} | I/O | Bidirektionaler Datenbus (Ausgang wenn OE low)

|

Tabelle 28-14: Pin-Werte beim Einstieg in den Programmiermodus

| Pin | Symbol | Wert

|

|---|

| PAGEL | Prog_enable[3] | 0

|

| XA1 | Prog_enable[2] | 0

|

| XA0 | Prog_enable[1] | 0

|

| BS1 | Prog_enable[0] | 0

|

Tabelle 28-15: Kodierung von XA1 und XA0

| XA1 | XA0 | Aktion bei Puls an XTAL1

|

|---|

| 0 | 0 | Lade Flash- oder EEPROM-Adresse (High- oder Low-Teil je nach BS1).

|

| 0 | 1 | Lade Daten (High- oder Low-Byte für Flash je nach BS1).

|

| 1 | 0 | Lade Kommando

|

| 1 | 1 | Keine Aktion, Ruhezustand

|

Tabelle 28-16: Kommandobyte-Kodierung

| Kommandobyte | Ausgeführtes Kommando

|

|---|

| 1000 0000 | Chip löschen

|

| 0100 0000 | Fuse-Bits schreiben

|

| 0010 0000 | Sperrbits schreiben

|

| 0001 0000 | Flash schreiben

|

| 0001 0001 | EEPROM schreiben

|

| 0000 1000 | Signatur-Bytes und Kalibrierbyte lesen

|

| 0000 0100 | Fuse- und Sperrbits lesen

|

| 0000 0010 | Flash lesen

|

| 0000 0011 | EEPROM lesen

|

28.7 Parallel programmieren

28.7.1 Programmiermodus aktivieren

The following algorithm puts the device in Parallel (High-voltage) Programming mode:

- Set Prog_enable pins listed in Tabelle 28-14 to “0000”, RESET pin to 0 V and UCC to 0 V.

- Apply 4,5 - 5,5 V between UCC and GND.

Ensure that UCC reaches at least 1,8 V within the next 20 µs.

- Wait 20 - 60 µs, and apply 11,5 - 12,5 V to RESET.

- Keep the Prog_enable pins unchanged for at least 10 µs after the High-voltage has been applied

to ensure the Prog_enable Signature has been latched.

- Wait at least 300 µs before giving any parallel programming commands.

- Exit Programming mode by power the device down or by bringing RESET pin to 0 V.

If the rise time of the UCC is unable to fulfill the requirements listed above,

the following alternative algorithm can be used.

- Set Prog_enable pins listed in Tabelle 28-14 to “0000”, RESET pin to 0V and UCC to 0V.

- Apply 4,5 - 5,5 V between UCC and GND.

- Monitor UCC, and as soon as UCC reaches 0,9 - 1,1 V, apply 11,5 - 12,5 V to RESET.

- Keep the Prog_enable pins unchanged for at least 10µs after the High-voltage has been applied

to ensure the Prog_enable Signature has been latched.

- Wait until UCC actually reaches 4,5 - 5,5 V before giving any parallel programming commands.

- Exit Programming mode by power the device down or by bringing RESET pin to 0 V.

28.7.2 Überlegungen für effizientes Programmieren

The loaded command and address are retained in the device during programming. For efficient programming,

the following should be considered.

- The command needs only be loaded once when writing or reading multiple memory locations.

- Skip writing the data value 0xFF, that is the contents of the entire EEPROM (unless the EESAVE Fuse is

programmed) and Flash after a Chip Erase.

- Address high byte needs only be loaded before programming or reading a new 256 word window in Flash

or 256 byte EEPROM. This consideration also applies to Signature bytes reading.

28.7.3 Chip löschen

The Chip Erase will erase the Flash and EEPROM(1) memories plus Lock bits.

The Lock bits are not reset until the program memory has been completely erased.

The Fuse bits are not changed.

A Chip Erase must be performed before the Flash and/or EEPROM are reprogrammed.

- Hinweis:

- The EEPRPOM memory is preserved during Chip Erase if the EESAVE Fuse is programmed.

Load Command “Chip Erase”

- Set XA1, XA0 to “10”. This enables command loading.

- Set BS1 to “0”.

- Set DATA to “1000 0000”. This is the command for Chip Erase.

- Give XTAL1 a positive pulse. This loads the command.

- Give WR a negative pulse. This starts the Chip Erase. RDY/BSY goes low.

- Wait until RDY/BSY goes high before loading a new command.

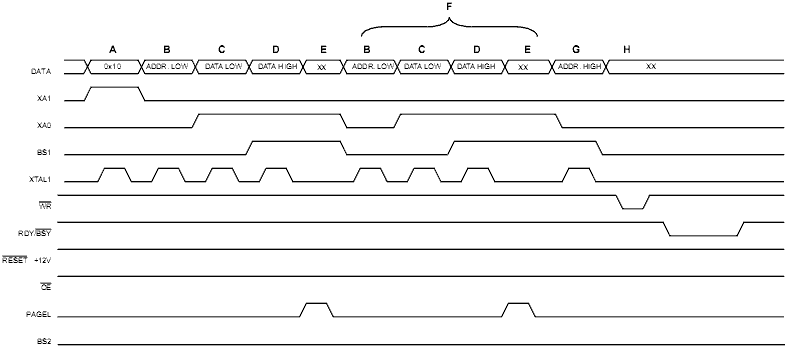

28.7.4 Flash-Speicher programmieren

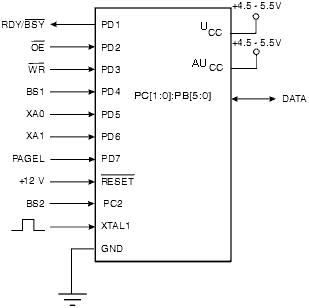

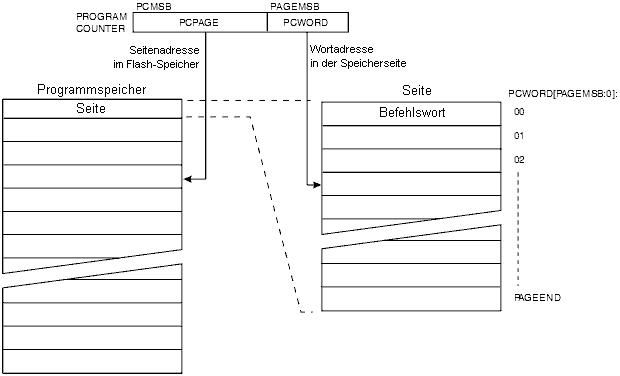

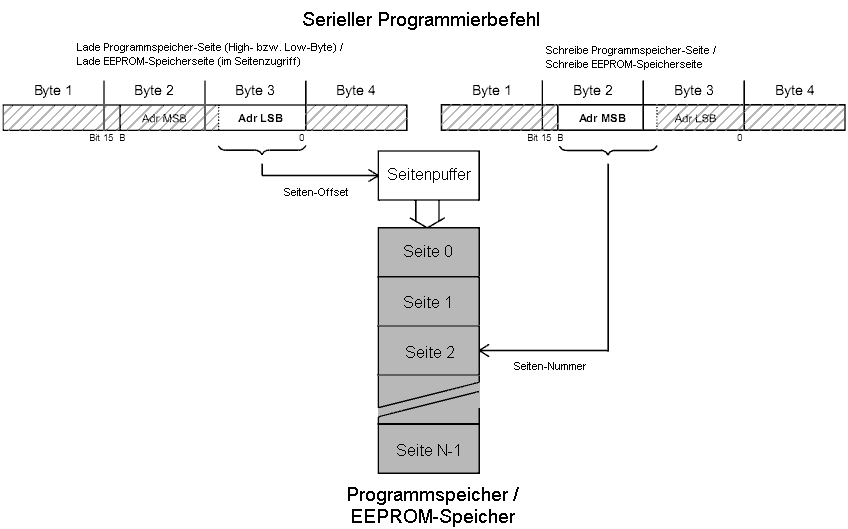

The Flash is organized in pages, see Table 28-11.

When programming the Flash, the program data is latched into a page buffer.

This allows one page of program data to be programmed simultaneously.

The following procedure describes how to program the entire Flash memory:

- Load Command “Write Flash”

- Set XA1, XA0 to “10”. This enables command loading.

- Set BS1 to “0”.

- Set DATA to “0001 0000”. This is the command for Write Flash.

- Give XTAL1 a positive pulse. This loads the command.

- Load Address Low byte

- Set XA1, XA0 to “00”. This enables address loading.

- Set BS1 to “0”. This selects low address.

- Set DATA = Address low byte (0x00 - 0xFF).

- Give XTAL1 a positive pulse. This loads the address low byte.

- Load Data Low Byte

- Set XA1, XA0 to “01”. This enables data loading.

- Set DATA = Data low byte (0x00 - 0xFF).

- Give XTAL1 a positive pulse. This loads the data byte.

- Load Data High Byte

- Set BS1 to “1”. This selects high data byte.

- Set XA1, XA0 to “01”. This enables data loading.

- Set DATA = Data high byte (0x00 - 0xFF).

- Give XTAL1 a positive pulse. This loads the data byte.

- Latch Data

- Set BS1 to “1”. This selects high data byte.

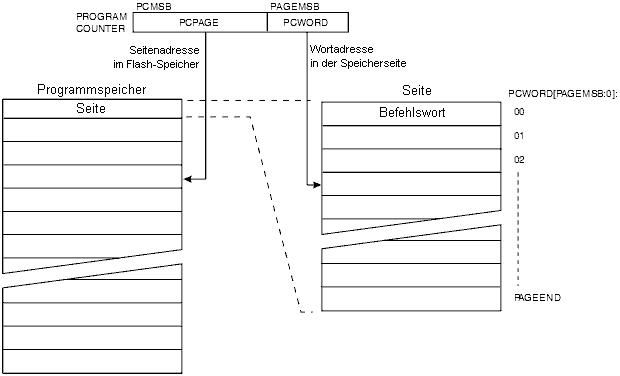

- Give PAGEL a positive pulse. This latches the data bytes. (See Figure 28-3 for signal waveforms)

- Repeat B through E until the entire buffer is filled or until all data within the page is loaded.

While the lower bits in the address are mapped to words within the page, the higher bits address the pages

within the FLASH. This is illustrated in Figure 28-2. Note that if less than eight bits are required to

address words in the page (pagesize < 256), the most significant bit(s) in the address low byte are used to

address the page when performing a Page Write.

- Load Address High byte

- Set XA1, XA0 to “00”. This enables address loading.

- Set BS1 to “1”. This selects high address.

- Set DATA = Address high byte (0x00 - 0xFF).

- Give XTAL1 a positive pulse. This loads the address high byte.

- Program Page

- Give WR a negative pulse. This starts programming of the entire page of data. RDY/BSY goes low.

- Wait until RDY/BSY goes high (See Figure 28-3 for signal waveforms).

- Repeat B through H until the entire Flash is programmed or until all data has been programmed.

- End Page Programming

- Set XA1, XA0 to “10”. This enables command loading.

- Set DATA to “0000 0000”. This is the command for No Operation.

- Give XTAL1 a positive pulse. This loads the command, and the internal write signals are reset.

Bild 28-2: Addressing the Flash Which is Organized in Pages(1)

- Hinweis:

- PCPAGE und PCWORD siehe Tabelle 28-11

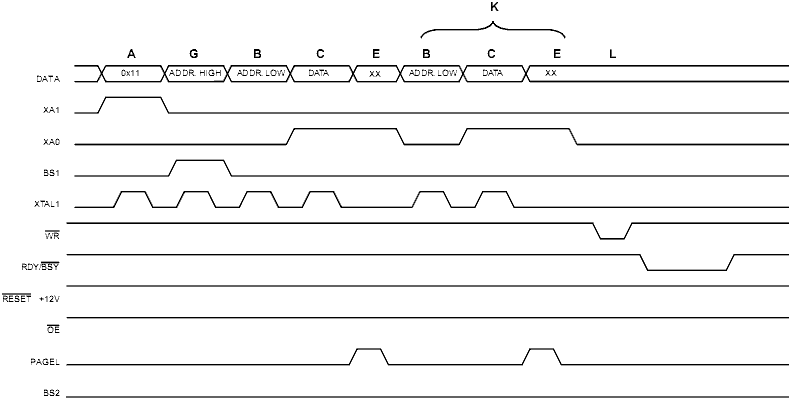

Bild 28-3: Programming the Flash Waveforms(1)

- Hinweis:

- “XX” is don’t care. The letters refer to the programming description above.

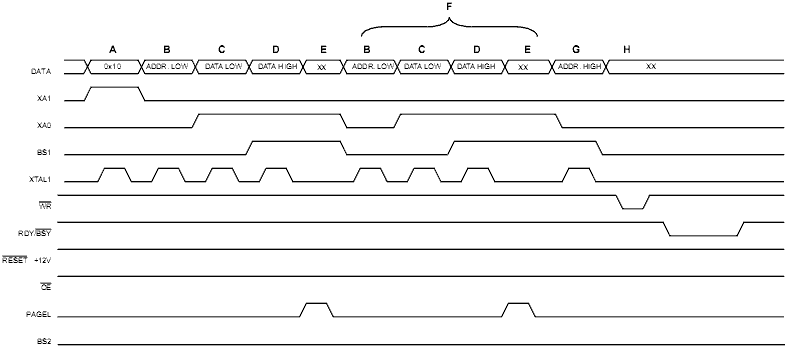

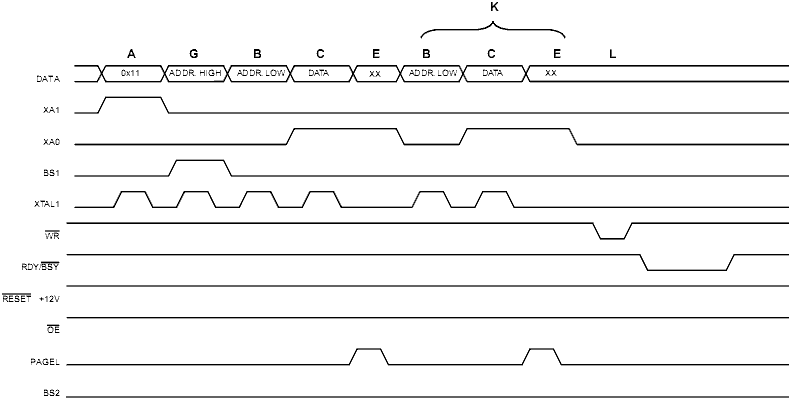

28.7.5 EEPROM programmieren

The EEPROM is organized in pages, see Table 28-12.

When programming the EEPROM, the program data is latched into a page buffer.

This allows one page of data to be programmed simultaneously.

The programming algorithm for the EEPROM data memory is as follows

(refer to ”Programming the Flash” for details on Command, Address and Data loading):

- A Load Command “0001 0001”.

- G Load Address High Byte (0x00 - 0xFF).

- B Load Address Low Byte (0x00 - 0xFF).

- C Load Data (0x00 - 0xFF).

- E Latch data (give PAGEL a positive pulse).

- K Repeat 3 through 5 until the entire buffer is filled.

- L Program EEPROM page

- Set BS1 to “0”.

- Give WR a negative pulse. This starts programming of the EEPROM page. RDY/BSY goes low.

- Wait until to RDY/BSY goes high before programming the next page

(See Figure 28-4 for signal waveforms).

Bild 28-4: Programming the EEPROM Waveforms

28.7.6 Flash-Speicher lesen

The algorithm for reading the Flash memory is as follows

(refer to ”Programming the Flash” for details on Command and Address loading):

- A Load Command “0000 0010”.

- G Load Address High Byte (0x00 - 0xFF).

- B Load Address Low Byte (0x00 - 0xFF).

- Set OE to “0”, and BS1 to “0”. The Flash word low byte can now be read at DATA.

- Set BS1 to “1”. The Flash word high byte can now be read at DATA.

- Set OE to “1”.

28.7.7 EEPROM lesen

The algorithm for reading the EEPROM memory is as follows

(refer to ”Programming the Flash” for details on Command and Address loading):

- A Load Command “0000 0011”.

- G Load Address High Byte (0x00 - 0xFF).

- B Load Address Low Byte (0x00 - 0xFF).

- Set OE to “0”, and BS1 to “0”. The EEPROM Data byte can now be read at DATA.

- Set OE to “1”.

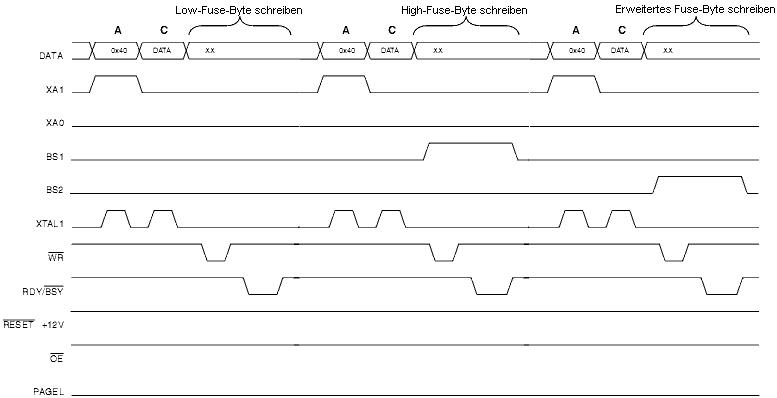

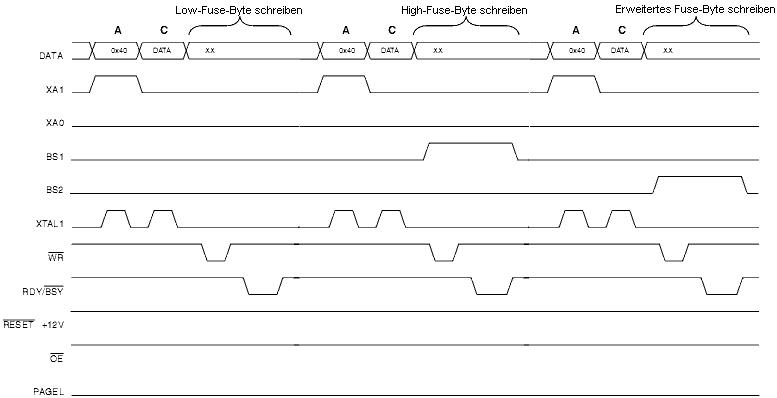

28.7.8 Low-Fuse-Bits setzen

The algorithm for programming the Fuse Low bits is as follows

(refer to ”Programming the Flash” for details on Command and Data loading):

- A Load Command “0100 0000”.

- C Load Data Low Byte. Bit n = “0” programs and bit n = “1” erases the Fuse bit.

- Give WR a negative pulse and wait for RDY/BSY to go high.

28.7.9 High-Fuse-Bits setzen

The algorithm for programming the Fuse High bits is as follows

(refer to ”Programming the Flash” for details on Command and Data loading):

- A Load Command “0100 0000”.

- C Load Data Low Byte. Bit n = “0” programs and bit n = “1” erases the Fuse bit.

- Set BS1 to “1” and BS2 to “0”. This selects high data byte.

- Give WR a negative pulse and wait for RDY/BSY to go high.

- Set BS1 to “0”. This selects low data byte.

28.7.10 Erweiterte Fuse-Bits setzen

The algorithm for programming the Extended Fuse bits is as follows

(refer to ”Programming the Flash” for details on Command and Data loading):

- A Load Command “0100 0000”.

- C Load Data Low Byte. Bit n = “0” programs and bit n = “1” erases the Fuse bit.

- Set BS1 to “0” and BS2 to “1”. This selects extended data byte.

- Give WR a negative pulse and wait for RDY/BSY to go high.

- Set BS2 to “0”. This selects low data byte.

Bild 28-5: Programming the Fuses Waveforms

28.7.11 Sperrbits setzen

The algorithm for programming the Lock bits is as follows

(refer to ”Programming the Flash” for details on Command and Data loading):

- A Load Command “0010 0000”.

- C Load Data Low Byte. Bit n = “0” programs the Lock bit. If LB mode 3 is programmed (LB1 and LB2 is

programmed), it is not possible to program the Boot Lock bits by any External Programming mode.

- Give WR a negative pulse and wait for RDY/BSY to go high.

The Lock bits can only be cleared by executing Chip Erase.

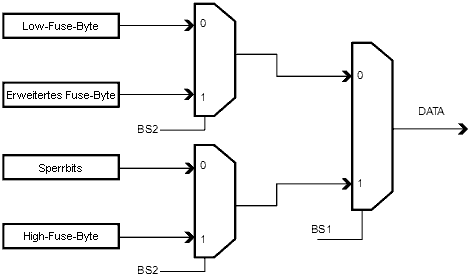

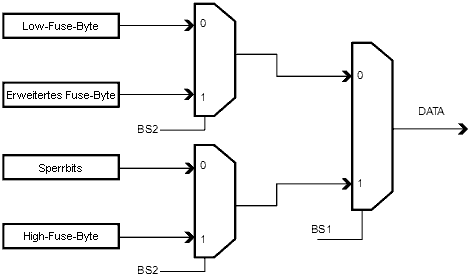

28.7.12 Fuse- und Sperrbits lesen

The algorithm for reading the Fuse and Lock bits is as follows

(refer to ”Programming the Flash” for details on Command and Data loading):

- A Load Command “0000 0100”.

- Set OE to “0”, BS2 to “0” and BS1 to “0”. The status of the Fuse Low bits can now be read at DATA (“0” means programmed).

- Set OE to “0”, BS2 to “1” and BS1 to “1”. The status of the Fuse High bits can now be read at DATA (“0” means programmed).

- Set OE to “0”, BS2 to “1”, and BS1 to “0”. The status of the Extended Fuse bits can now be read at DATA (“0” means programmed).

- Set OE to “0”, BS2 to “0” and BS1 to “1”. The status of the Lock bits can now be read at DATA (“0” means programmed).

- Set OE to “1”.

Bild 28-6: Mapping Between BS1, BS2 and the Fuse and Lock Bits During Read

28.7.13 Signatur-Bytes lesen

The algorithm for reading the Signature bytes is as follows

(refer to ”Programming the Flash” for details on Command and Address loading):

- A Load Command “0000 1000”.

- B Load Address Low Byte (0x00 - 0x02).

- Set OE to “0”, and BS1 to “0”. The selected Signature byte can now be read at DATA.

- Set OE to “1”.

28.7.14 Kalibrier-Byte lesen

The algorithm for reading the Calibration byte is as follows

(refer to ”Programming the Flash” for details on Command and Address loading):

- A Load Command “0000 1000”.

- B Load Address Low Byte, 0x00.

- Set OE to “0”, and BS1 to “1”. The Calibration byte can now be read at DATA.

- Set OE to “1”.

28.7.15 Kennwerte

For characteristics of the Parallel Programming, see ”Parallel Programming Characteristics”.

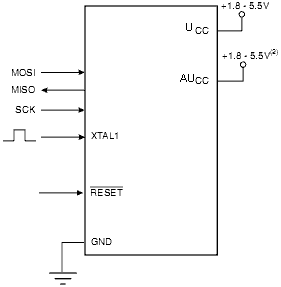

28.8 Seriell programmieren

Sowohl der Flash als auch das EEPROM können über das SPI programmiert werden, während RESET auf GND gehalten wird.

Das serielle Interface besteht aus den Pins SCK, MOSI (Input) und MISO (Output).

Nachdem RESET auf Low gesetzt ist, muss erst ein Programmierfreigabe-Befehl ausgeführt werden,

bevor eine Programmier- oder Löschoperation durchgeführt werden kann.

Die Pinbelegung, die nachfolgend abgebildet ist, gilt nicht für alle AVR-Controller.

Bild 28-7: Serielle Programmierung und Überprüfung

- Hinweise:

- Wenn der Schaltkreis vom internen Oszillator getaktet wird,

ist keine Taktquelle an XTAL1 erforderlich

- UCC – 0,3 V < AUCC < UCC + 0,3 V,

allerdings sollte AUCC stets im Bereich 1,8 … 5,5 V sein

Für das EEPROM ist ein automatischer Löschzyklus in den Schreibbefehl implementiert (nur im seriellen Programmiermodus),

so dass der Chip vorher nicht extra gelöscht werden muss.

Das Chip-Löschen setzt die Speicherzellen von Programm- und EEPROM-Speicher auf den Wert 0xFF.

Anhängig von den CKSEL-Fuses muss ein gültiger Takt vorhanden sein.

Die minimale Low- und High-Zeit für den seriellen Takt Eingang (SCK) ist wie folgt definiert:

Low: > 2 CPU-Takte bei fck < 12 MHz und 3 CPU Takte bei fck ≥ 12 MHz.

High: > 2 CPU-Takte bei fck < 12 MHz und 3 CPU Takte bei fck ≥ 12 MHz.

28.8.1 Pinbelegung zur Programmierung

Tabelle 28-17: Pinzuordnung

| Symbol | Pin | I/O | Beschreibung

|

|---|

| MOSI | PB3 | I | Serieller Dateneingang

|

| MISO | PB4 | O | Serieller Datenausgang

|

| SCK | PB5 | I | Serieller Takt (Eingang)

|

28.8.2 Programmier-Algorithmus

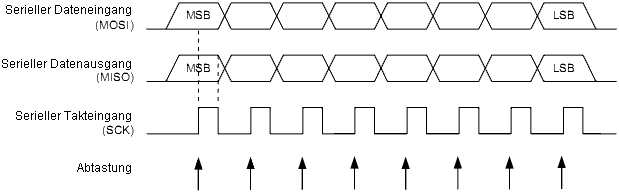

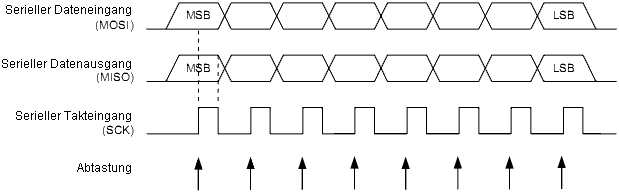

Wenn Daten seriell geschrieben werden, werden diese mit der steigenden Flanke des SCK getaktet.

Wenn Daten aus dem Baustein ausgelesen werden, so werden diese mit der fallenden Flanke des SCK-Signals getaktet.

Siehe Bild 28-9 zum Timing.

Für die Programmierung und Überprüfung im seriellen Programmiermodus wird folgender Ablauf empfolen

(Siehe Tabelle 28-19):

- Spannung einschalten:

- Anlegen der Spannung zwischen UCC und GND während Reset und SCK auf 0 liegen

- Wenn das Programmiergerät nicht sicherstellen kann,

dass SCK während des Einschaltens der Spannungsversorgung auf Low gehalten werden kann,

dann muss auf Reset ein positiver Impuls von mindestens 2 MCU-Takten Dauer gegeben werden,

nachdem SCK auf 0 gesetzt wurde.

- Warten für mindestens 20 ms und Freigeben des Programmiermodus durch Senden

des Programmierfreigabe Befehls an den MOSI Pin.

- Die Programmierbefehle werden nicht ausgeführt, wenn die Kommunikation zwischen Baustein

und Programmiergerät nicht sauber synchronisiert ist.

Wenn beide synchron sind, wird das zweite Byte des Programmierfreigabe-Befehls (53h) zurückgegeben, während das dritte Byte des Befehls gesendet wird.

Egal ob dieses Byte zurückgegeben wird, die vier Byte des Befehls müssen auf jeden Fall an den Baustein gesendet werden.

Wenn das Byte (53h) nicht zurückgegeben wird, dann gibt man RESET einen positiven Impuls und versucht erneut den Programmierfreigabe-Befehl zu senden.

- Der Flash wird seitenweise programmiert.

Die Seitengröße ist in Tabelle 93 angegeben.

Die Speicherseite wird byteweise geladen, indem die 5 LSB der Adresse

zusammen mit den Daten in einem Load Programm Memory Page Befehl übergeben werden.

Um sicherzustellen, dass die Seite korrekt geladen wird,

muss erst das Daten Low Byte geladen werden,

bevor das Daten High Byte der Adresse übergeben wird.

Die Seite wird gespeichert, indem ein Write Program Memory Page Befehl

zusammen mit den 7 MSB der Adresse geladen wird.

Wenn kein Polling genutzt wird, muss der Anwender mindestens die Zeit tWD_FLASH warten,

bis die nächste Seite programmiert werden kann.

- Der EEPROM wird byteweise programmiert, wobei sowohl die Adresse und die Daten

zusammen in dem entsprechenden Schreibbefehl erwartet werden.

Eine EEPROM-Speicherzelle wird zuerst automatisch gelöscht, bevor sie neu beschrieben wird.

Man kann durch Pollen ermitteln, wann das nächste Byte in den Flash oder EEPROM geschrieben werden kann.

Das Pollen ist unnötig, wenn man die Zeit tWD_EEPROM wartet, bevor der nächste Befehl übermittel wird.

In einem gelöschten Baustein brauchen die Werte FFh im Datenspeicher nicht extra programmiert zu werden.

- Der EEPROM wird seitenweise programmiert.

- Jede Speicherzelle kann überprüft werden, indem mit dem Lesebefehl

der Inhalt der Speicherzelle der aktuellen Adresse über den MISO-Pin ausgegeben wird.

- Am Ende der Programmierung kann RESET auf High gelegt werden,

um die normale Schaltkreisfunktion zu starten.

- Abschalten der Spannung (wenn benötigt):

- RESET auf „1“ legen

- Spannung abschalten

Tabelle 28-18: Typische Wartezeiten, bevor die nächste Flash- oder EEPROM-Schreiboperation starten darf

| Symbol | Minimale Wartezeit

|

|---|

tWD_FLASH| 4,5 ms

| tWD_EEPROM| 3,6 ms

| tWD_ERASE| 9,0 ms

| tWD_FUSE| 4,5 ms

| | | | |

28.8.3 Befehlssatz zur seriellen Programmierung

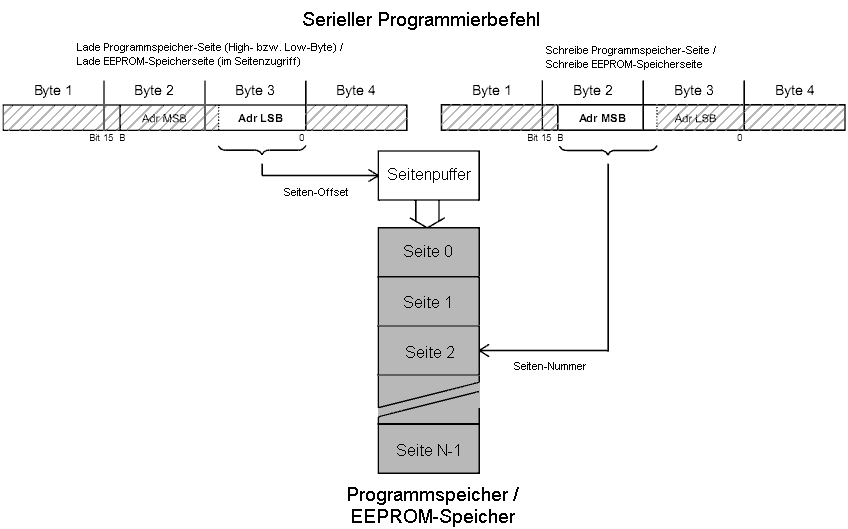

Die Tabelle 28-19 und das Bild 28-8 beschreiben den Befehlssatz.

Tabelle 28-19: Befehlssatz bei serieller Programmierung

- Hinweise:

- Nicht alle Befehle sind für alle AVR-Typen gültig; nicht für diese ATmegaX8

- a = Adressbit

- „1“ bedeutet unprogrammiert, „0“ bedeutet programmiert

- Für künftige Kompatibilität sollten ungenztzte Fuses unprogrammiert („1“) belassen werden

- Siehe entsprechenden Abschnitt zu Fuse- und Sperrbits, Kalibrier- und Signaturbytes sowie Seitengrößen

- Befehle zum Zugriff auf den Programmspeicher benutzen eine Wortadresse. Diese Adresse darf wahlfrei innerhalb der aktuellen Seite sein.

- Siehe Atmel-Website für Anwender-Hinweise zum Programmieren und zu Programmiergeräten

- 16-Bit-Worte

Solange das Bit 0 im RDY/BSY-Datenbyte = 1 ist,

ist eine Programmieroperation in Gange.

Warte bis dieses Bit = 0 wird vor dem nächsten Befehl.

Innerhalb derselben Speicherseite muss das Low-Byte vor dem High-Byte geladen werden.

Nachdem die Daten in den Seitenpuffer geladen wurden, kann die EEPROM-Seite wie im folgenden Bild programmiert werden.

Bild 28-8: Beispiel zu seriellen Programmierung

28.8.4 SPI-Kennwerte zur Programmierung

Bild 28-9: Zeitlicher Ablauf der SPI-Programmierung

Für Zeiten siehe Kennwerte der SPI-Schnittstelle