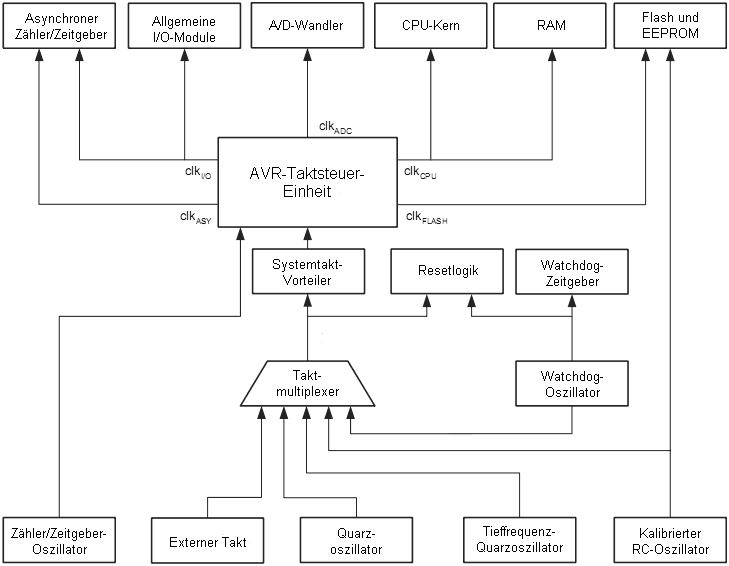

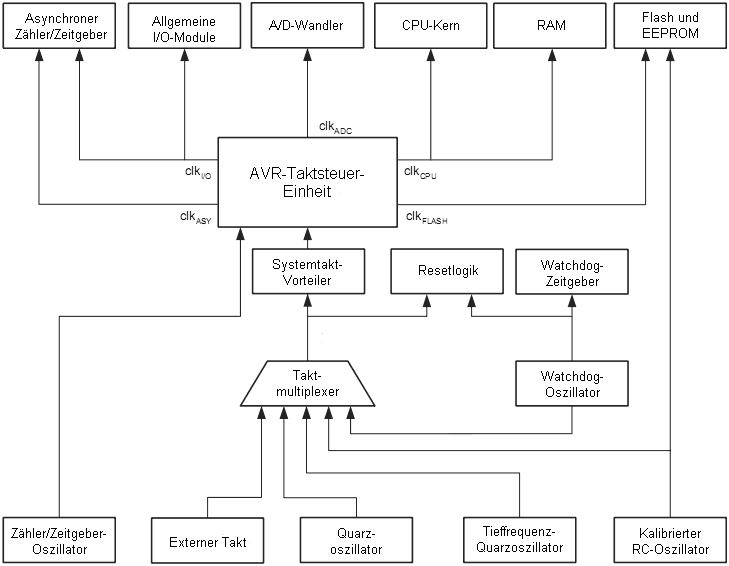

Der Chip kann aus verschiedenen Quellen getaktet werden, die mit den Fuse-Bits ausgewählt werden. Der Takt der ausgewählten Quelle bildet den Input für den Taktgenerator des Bausteins und ist mit den entsprechenden Modulen verbunden.

| Taktung des Bausteins | CKSEL3:0 |

|---|---|

| Externer Quarz/Keramik-Resonator | 1111 - 1010 |

| Externer Quarz niedrige Frequenz | 1001 |

| Externer RC Oszillator | 1000 — 0101 |

| Kalibirierter interner RC Oszillator | 0100 — 0001 |

| Externer Takt | 0000 |

Der Baustein wird ausgeliefert mit CKSEL = „0010“ und SUT = „10“ (interner RC-Oszillator mit 8 MHz, langsam ansteigende Versorgungsspannung). Dazu ist die CLKDIV-Fuse gesetzt, d.h. der Systemtakt beträgt 1 MHz.

Jede Taktquelle benötigt eine ausreichende Speisespannung UCC sowie eine minimale Anzahl von Schwingungen, bevor sie ausreichend stabil läuft.

Wenn die CPU aus dem Leistung-weg- oder Leistung-spar-Modus aufwacht, bestimmt die ausgewählte Taktquelle die Aufwachzeit und stellt einen stabilen Takt sicher, bevor der erste Befehl ausgeführt wird. Wenn die CPU nach einem Reset startet, verlängert sich die Verzögerung, damit ein stabiler Pegel der Versorgungsspannung erreicht wird, bevor mit der Abarbeitung des Programms begonnen wird.

Der Watchdog-Oszillator wird verwendet, um den Echtzeit-Anteil der Aufwachzeit zu bestimmen. Die Anzahl der Zyklen des Watchdog-Zeitgebers wird für jede Verzögerung benutzt. Die Frequenz des Watchdog-Oszillators ist von der Betriebsspannung abhängig (siehe Typische Charakteristik des ATmega8).

| Typische Zeitüberschreitung (UCC = 5,0 V) | Typische Zeitüberschreitung (UCC = 3,0 V) | Anzahl der Zyklen |

|---|---|---|

| 0 ms | 0 ms | 0 |

| 4,1 ms | 4,3 ms | 512 |

| 65 ms | 69 ms | 8 K (8.192) |

| Frequenzbereich | Empfohlener Bereich für Kondensatoren C1 and C2 | CKSEL[3:1] (1)

| 0.4 - 0.9 MHz | – | 100 (2)

| 0.9 - 3.0 MHz | 12 - 22 pF | 101

| 3.0 - 8.0 MHz | 12 - 22 pF | 110

| 8.0 - 16.0 MHz | 12 - 22 pF | 111

| |

|---|

| Oszillator-Typ, Spannungsbedingung | Hochlufzeit vom Leistung-weg und Leistung-spar-Modus | Zusätzliche Verzögerung von Reset (UCC = 5.0 V) | CKSEL0 | SUT[1:0] | |||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Keramikresonator, schneller Spannungsanstieg | 258 Takte | 14 Takte + 4,1 ms (1)

| 0

| 00

| Keramikresonator | langsamer Spannungsanstieg 258 Takte

| 14 Takte + 65 ms (1)

| 0

| 01

| Keramikresonator, | Unterspannungsdetektor aktiv 1K Takte

| 14 Takte (2)

| 0

| 10

| Keramikresonator, | schneller Spannungsanstieg 1K Takte

| 14 Takte + 4.1 ms (2)

| 0

| 11

| Keramikresonator, | langsamer Spannungsanstieg 1K Takte

| 14 Takte + 65 ms (2)

| 1

| 00

| Quarzoszillator, | Unterspannungsdetektor aktiv 16K Takte

| 14 Takte

| 1

| 01

| Quarzoszillator, | schneller Spannungsanstieg 16K Takte

| 14 Takte + 4.1 ms

| 1

| 10

| Quarzoszillator, | langsamer Spannungsanstieg 16K Takte

| 14 Takte + 65 ms

| 1

| 11

| |

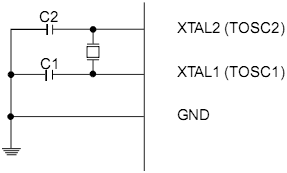

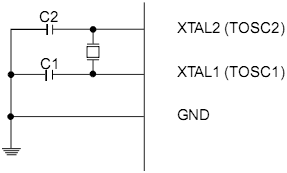

Die Pins XTAL1 und XTAL2 sind der Eingang und Ausgang eines invertierenden Verstärkers, der als Oszillator verwendet werden kann. Es können Quarz- oder Keramik- Resonatoren verwendet werden. Mit der CKOPT-Fuse kann zwischen zwei verschiedenen Betriebsarten des Oszillator Verstärkers ausgewählt werden. Wenn die CKOPT-Fuse programmiert ist, dann arbeitet der Oszillator mit einer voll getriebenen Ausgangsschwingung. Dieser Modus ist zu empfehlen, wenn in einer störanfälligen Umgebung gearbeitet wird oder der Ausgang XTAL2 einen weiteren externen Baustein taktet. In diesem Modus ist ein weiter Frequenzbereich möglich.

Wenn die CKOPT-Fuse nicht programmiert ist, dann arbeitet der Oszillator mit einer kleineren Ausgangsschwingung.

Dadurch ist auch der Stromverbrauch geringer.

Dieser Modus hat einen eingeschränkten Frequenzbereich, außerdem können keine weiteren externen Bausteine getaktet werden.

Für alle Resonatoren gilt als maximale Frequenz 8 MHz bei unprogrammierter CKOPT-Fuse und 16 MHz bei programmierter CKOPT-Fuse. Die Kondensatoren C1 und C2 sollten immer gleich groß sein, unabhängig davon, welcher Typ von Resonator verwendet wird. Der optimale Wert für die Kondensatoren hängt von dem verwendeten Resonator, den Streukapazitäten und den elektromagnetischen Einflüssen der Umgebung ab. Einige Richtwerte für die Größe der Kondensatoren bei der Verwendung von Quarzen sind in nachfolgender Tabelle angegeben. Bei keramischen Resonatoren können die empfohlenen Kapazitätswerte der jeweiligen Hersteller herangezogen werden. Bei dreipoligen Resonatoren sind diese häufig bereits eingebaut.

Der Oszillator kann in drei verschiedenen Modi betrieben werden, die jeweils für bestimmte Frequenzbereiche optimiert sind. Der Arbeitsmodus wird mit den Fuses CKSEL3 bis CKSEL1 eingestellt.

| CKOPT | CKSEL3 .. 1 | Frequenzbereich (MHz) | Empfohlene Werte für C1 und C2 bei Quarzen |

|---|---|---|---|

| 1 | 101(1) | 0,4 — 0,9 | - |

| 1 | 110 | 0,9 — 3,0 | 12 pF — 22 pF |

| 1 | 111 | 3,0 — 8,0 | 12 pF — 22 pF |

| 0 | 101, 110, 111 | 1,0 ≤ | 12 pF — 22 pF |

Die CKSEL0-Fuse bestimmt zusammen mit den SUT1- und SUT0-Fuses die Start-Up Zeit wie in nachfolgender Tabelle angegeben.

| CKSEL0 | SUT1 .. 0 | Start-up Zeit von Power-down und Power-save | Zusätzliche Verzögerung von Reset (VCC=5,0V) | Empfohlene Verwendung | |||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 00 | 258 CK (1) | 4,1 ms | Keramikresonator, schneller Spannungsanstieg

| 0 | 01 | 258 CK (1) | 65 ms | Keramikresonator, langsamer Spannungsanstieg

| 0 | 10 | 1k CK (2) | - | Keramikresonator, BOD freigegeben

| 0 | 11 | 1k CK (2) | 4,1 ms | Keramikresonator, schneller Spannungsanstieg

| 1 | 00 | 1k CK (2) | 65 ms | Keramikresonator, langsamer Spannungsanstieg

| 1 | 01 | 16k CK | - | Quarz, BOD freigegeben

| 1 | 10 | 16k CK | 4,1 ms | Quarz, schneller Spannungsanstieg

| 1 | 11 | 16k CK | 65 ms | Quarz, langsamer Spannungsanstieg

| |

Wenn ein 32.768-kHz-Uhrenquarz als Taktquelle für den Baustein verwendet wird, dann muss der Quarzoszillator für kleine Frequenzen durch Setzen der CKSEL-Fuses auf „1001“ ausgewählt werden. Der Quarz kann wie in obigem Abbild angeschlossen werden. Durch Programmieren der CKOPT-Fuses können interne Kapazitäten mit einem Wert von 36pF an XTAL1 und XTAL2 geschaltet werden, wodurch das Anschalten der externen Kapazitäten entfällt.

Wenn dieser Oszillator verwendet wird, ergibt sich die Hochlaufzeit durch die Programmierung der SUT-Fuses wie in nachfolgender Tabelle aufgeführt.

| SUT1 .. 0 | Hochlaufzeit von Leistung-weg und Leistung-sparen | Zusätzliche Verzögerung von Reset (VCC=5,0V) | Empfohlene Verwendung | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 00 | 1k CK (1) | 4,1 ms | Schneller Spannungsanstieg oder BOD freigegeben

| 01 | 1k CK (1) | 65 ms | Langsamer Spannungsanstieg

| 10 | 32k CK | 65 ms | Stabile Frequenz beim Hochlauf

| 11 | Reserviert

| | ||

Der interne RC-Oszillator bietet eine feste Frequenz von 8 MHz. Alle nominellen Frequenzen beziehen sich auf 5 V und 25 °C. Die CKOPT-Fuse bleibt bei der Verwendung des internen RC-Oszillators immer unprogrammiert. Während eines Resets lädt die Hardware ein Werkskalibrierungs-Byte in das OSCCAL-Register, wodurch der Oszillator automatisch kalibriert wird. Bei 5 V und 25 °C kann durch das Kalibrieren eine Frequenz mit einer Abweichung von ±1 % erreicht werden. Auch wenn der interne RC-Oszillator als Taktquelle verwendet wird, wird der Watchdog-Oszillator weiterhin für den Watchdog-Timer und für den Reset-Time-out verwendet. Siehe auch Kalibrierungs-Byte.

Wird zudem der Zeitgeber2-Oszillator verwendet, kann mit diesem der RC-Oszillator mit einer PLL in Software auf die gewünschte Frequenz quarzgenau gezogen und gehalten werden.

| CKSEL 3 … 0 | Frequenzbereich in MHz |

0010 (1) | 7,3 .. 8,1

| |

Die Hochlaufzeit ergibt sich durch die Programmierung der SUT-Fuses wie in nachfolgender Tabelle aufgeführt. Die Anschlusspins PB6 (XTAL1/TOSC1) und PB7 (XTAL2/TOSC2) können dann als normale I/O-Pins oder als Zeitgeber-Oszillator-Pins verwendet werden.

| SUT1 .. 0 | Hochlaufzeit von Leistung-weg und Leistung-sparen | Zusätzliche Verzögerung von Reset (UCC = 5,0 V) | Empfohlene Verwendung | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 00 | 6 CK | 14 CK (1) | BOD freigegeben

| 01 | 6 CK | 14 CK + 4,1 ms | Schneller Spannungsanstieg

| 10 (2) | 6 CK | 14 CK + 65 ms | Langsamer Spannungsanstieg

| 11 | Reserviert

| | ||

Dieser Oszillator liefert einen 128-kHz-Takt bei minimalem Energiebedarf. Die nominelle Frequenz gilt für 3 V und 25 °C. Die Auswahl dieses Oszillators erfolgt durch Setzen der CKSEL-Fuses auf „0011“.

| CKSEL3 … 0 | Nominelle Frequenz (1) |

|---|---|

| 0011 | 128 kHz |

Wenn dieser Oszillator verwendet wird, ergibt sich die Hochlaufzeit durch die Programmierung der SUT-Fuses wie in nachfolgender Tabelle aufgeführt.

| SUT1 .. 0 | Start-up Zeit von Power-down und Power-save | Zusätzliche Verzögerung von Reset (VCC=5,0V) | Empfohlene Verwendung | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 00 | 6 CK | 14 CK 1 | BOD freigegeben

| 01 | 6 CK | 14 CK + 4,1 ms | Schneller Spannungsanstieg

| 10 | 6 CK | 14 CK + 64 ms | Langsamer Spannungsanstieg

| 11 | reserviert

| | ||

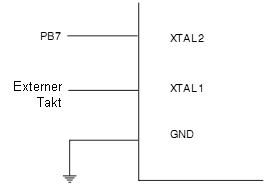

Wenn der Chip von einer externen Quelle getaktet werden soll, so ist diese wie nachfolgend abgebildet an das Pin XTAL1 anzuschließen, die CKSEL-Fuses sind mit „0000“ zu programmieren.

| CKSEL3..0 | Frequenz |

|---|---|

| 0000 | 0 - 20 MHz |

Wenn dieser Oszillator verwendet wird, ergibt sich die Hochlaufzeit durch die Programmierung der SUT-Fuses wie in nachfolgender Tabelle aufgeführt.

| SUT1 .. 0 | Start-up Zeit von Power-down und Power-save | Zusätzliche Verzögerung von Reset (VCC=5,0V) | Empfohlene Verwendung |

|---|---|---|---|

| 00 | 6 CK | 14 CK | BOD freigegeben |

| 01 | 6 CK | 14 CK + 4,1 ms | Schneller Spannungsanstieg |

| 10 | 6 CK | 14 CK + 65 ms | Langsamer Spannungsanstieg |

| 11 | Reserviert | ||

Wenn eine externe Taktquelle verwendet wird, so müssen plötzliche Frequenzänderungen unterbunden werden, um ein stabiles Arbeiten der CPU sicherzustellen. Eine Abweichung der Frequenz von mehr als 2% von einem Takt zum nächsten kann zu unvorhersehbaren Verhalten des Bausteins führen. Wenn eine Veränderung der Taktfrequenz vorgenommen werden soll, so muss die CPU währenddessen auf Reset gehalten werden.

Der Chip kann den Systemtakt am Pin CLKO ausgeben. Um den Ausgang zu aktivieren muss die CKOUT-Fuse programmiert werden. Dies ist vorteilhaft um andere Chips synchron mit Takt zu versorgen, zur Kalibrierung mittels Frequenzmesser oder zur Fehlersuche. Sogar während RESET wird der Takt an diesem Pin ausgegeben, weil die normale Portfunktion durch eine Fuse (und nicht durch Programmkode) überschrieben wird. Jede Taktquelle inklusive interne RC-Oszillatoren können als Takt für den Ausgang CLKO genutzt werden. Bei Verwendung des Systemtaktteilers wird der geteilte Takt am Ausgang wirksam.

Bei diesem Mikrocontroller kann ein Quarz direkt zwischen TOSC1 und TOSC2 angeschlossen werden. Durch Programmieren der CKOPT-Fuse können interne Kondensatoren an die Anschlüsse XTAL1 und XTAL2 geschaltet werden, so dass diese nicht extern angeschlossen werden müssen. Der Oszillator ist für die Verwendung eines 32,768-kHz-Uhrenquarzes optimiert. Das Anlegen einer externen Taktquelle an den Anschluss TOSC1 ist möglich, wenn das Bit EXTCLK in ASSR gesetzt wird.

Dieser Oszillator kann nicht als Systemtaktgenerator dienen! Sondern nur für den Zeitgeber 2 im asynchronen Betrieb. Da die Pins TOSC und XTAL zusammenfallen, kommen für den Systemtakt nur interne RC-Oszillatoren in Frage, entweder 8 MHz oder 128 kHz. Da der Systemtakt mindestens das Vierfache dieser Oszillatorfrequenz sein muss, kommt der 128-kHz-Oszillator nur bei Quarzen mit deutlich weniger als 32 kHz in Frage.

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x66) | CAL7 | CAL6 | CAL5 | CAL4 | CAL3 | CAL2 | CAL1 | CAL0 | OSCCAL |

|---|---|---|---|---|---|---|---|---|---|

| Zugriff | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| Startwert | Einzelchip-spezifischer Kalibrierwert | ||||||||

Indem das Kalibrierungs-Byte in das Register geschrieben wird, wird die Frequenz des internen Oszillators justiert, um dadurch die durch die Herstellung bedingt Ungenauigkeiten auszugleichen. Während eines Resets wird der Kalibrierungswert für die Frequenz von 1MHz, der im High-Byte der Signatur-Reihe (Adresse 00) hinterlegt ist, automatisch geladen und in das OSCCAL-Register geschrieben. Auch die Kalibrierungswerte für die Frequenzen von 2, 4, und 8 MHz sind in der Signaturreihe abgelegt. Soll der interne RC-Oszillator mit einer dieser Frequenz betrieben werden, so muss das Kalibrierungsbyte manuell geladen werden. Dies kann dadurch geschehen, indem man zunächst das Kalibrierungsbyte mit dem AVR-Studio ausliest und den Wert im Programm- oder EEPROM-Speicher hinterlegt. Die Software muss dann diesen Wert abholen und in das OSCCAL-Register schreiben.

Wenn das OSCCAL auf 00h steht, ist die niedrigste Frequenz ausgewählt. Werte größer als Null erhöhen die Frequenz des internen Oszillators, bei FFh ist die maximale Frequenz erreicht. Wenn die Applikationssoftware das EEPROM oder den Flash-Speicher beschreibt, sollte die eingestellte Frequenz nicht mehr als 10% über ihrem nominalen Wert liegen. Andernfalls können Fehler beim Schreiben des EEPROM oder Flash auftreten. Man sollte beachten, dass der Oszillator nur für das Kalibrieren auf 1, 2, 4 oder 8 MHz vorgesehen ist. Das Justieren anderer Werte ist nicht garantiert, so wie in nachfolgender Tabelle angegeben.

| OSCCAL Wert | Min Frequenz in Prozent der nominalen Frequenz (%) | Max Frequenz in Prozent der nominalen Frequenz (%) |

| 00h | 50 | 100 |

| 7Fh | 75 | 150 |

| FFh | 100 | 200 |

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x61) | CLKPCE | - | - | - | CLKPS3 | CLKPS2 | CLKPS1 | CLKPS0 | GLKPR |

|---|---|---|---|---|---|---|---|---|---|

| Zugriff | R/W! | R | R | R | R/W | R/W | R/W | R/W | |

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | CKDIV8 | CKDIV8 |

| CLKPS3..0 | Teilerfaktor |

|---|---|

| 0000 (0x00) | 1 |

| 0001 (0x01) | 2 |

| 0010 (0x02) | 4 |

| 0011 (0x03) | 8 |

| 0100 (0x04) | 16 |

| 0101 (0x05) | 32 |

| 0110 (0x06) | 64 |

| 0111 (0x07) | 128 |

| 1000 (0x08) | 256 |

| 1001 (0x09) | reserviert |

| 1010 (0x0A) | |

| 1011 (0x0B) | |

| 1100 (0x0C) | |

| 1101 (0x0D) | |

| 1110 (0x0E) | |

| 1111 (0x0F) |