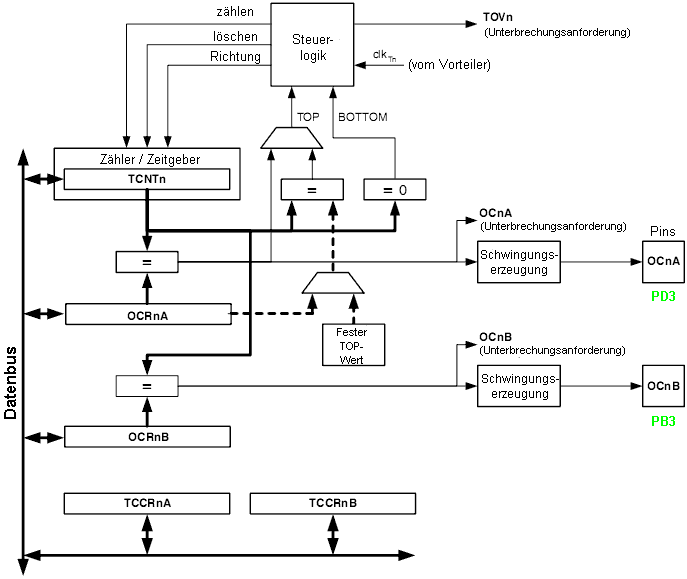

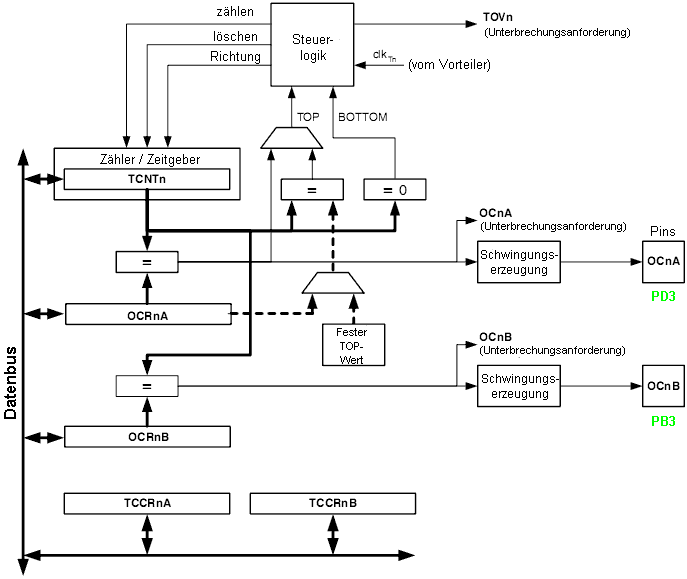

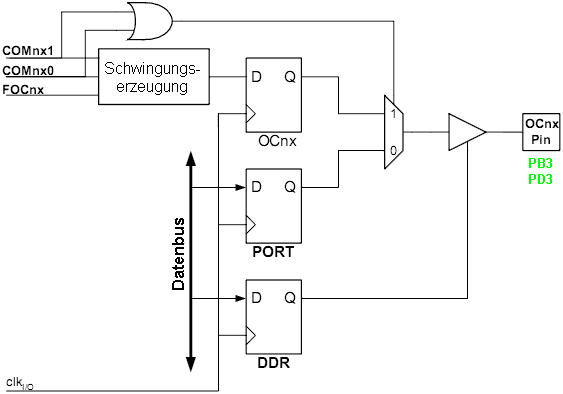

Ein einfaches Blockschaltbild des 8-bit Zähler/Zeitgeber ist nachfolgend dargestellt.

Die Nummern der Pins sind von der Gehäuseform des Bausteins abhängig (siehe Anschlussbelegung).

Die I/O-Register, die dazugehörigen I/O-Bits und die I/O-Pins,

auf die die CPU direkt zugreifen kann, sind fett dargestellt.

Das Zähler/Zeitgeber Register (TCNT2) und die Output Compare Register OCR2A und OCR2B sind 8-bit Register. Die Signale der Interruptanforderungen sind im Timer Interrupt Flag Register (TIFR) sichtbar. Alle Interrupts können individuell im Timer Interrupt Mask Register (TIMSK) maskiert werden. Die beiden letztgenannten Register sind im Blockschaltbild nicht abgebildet, da sie auch die Bits für andere Timer-Einheiten enthalten.

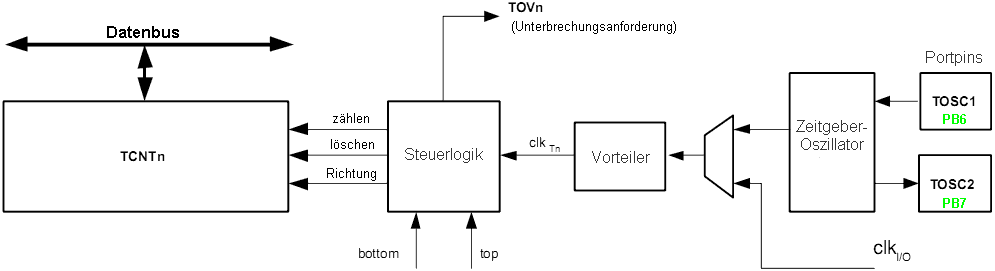

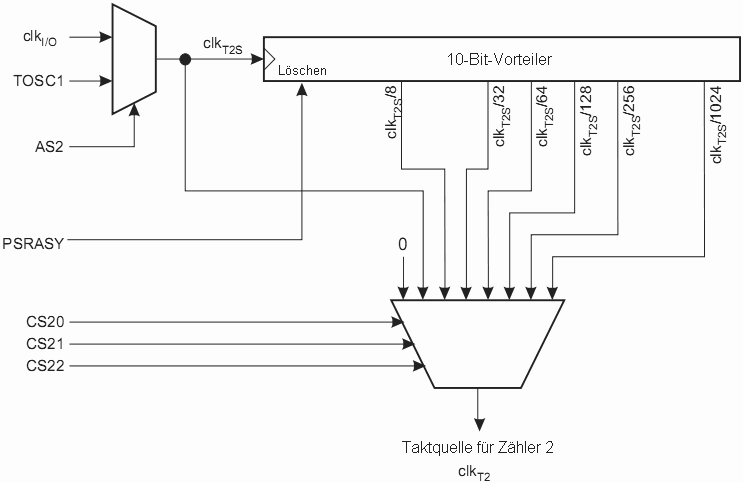

Der Zähler/Zeitgeber kann intern, über einen Vorteiler oder durch eine asynchrone externe Taktquelle an den TOSC1/2 Pins getaktet werden. Die asynchronen Operationen werden durch das Asynchronous Status Register kontrolliert. Die Taktauswahl-Logik gibt vor, durch welchen Takt der Timer seinen Wert inkrementiert oder dekrementiert. Der Zähler/Zeitgeber ist inaktiv, wenn keine Taktquelle ausgewählt wurde. Der Ausgang der Taktauswahl-Logik wird als Timer-Takt clkT2 bezeichnet.

Das zweifach gebufferte Output Compare Register (OCR2) wird ständig mit dem Wert des Timers verglichen. Das Ergebnis dieses Vergleiches kann vom Wellenformerzeuger genutzt werden, um eine PWM oder eine variable Frequenz am Ausgang des Output Compare Pins (OC2) zu erzeugen. Das Ereignis der Vergleichsübereinstimmung setzt außerdem das Compare Match Flag (OCF2), das genutzt werden kann, um einen Output Compare Interrupt auszulösen.

| BOTTOM | Der Zähler erreicht BOTTOM, wenn er 0x00 wird. |

| MAX | Der Zähler erreicht sein MAXimum, wenn er 0xFF (255 dezimal) wird |

| TOP | Der Zähler erreicht TOP, wenn die Zählung einen oberen Grenzwert erreicht. Als oberer Wert kann 0xFF oder der Wert im OCR2A-Register festgelegt werden. Diese Festlegung ist vom Betriebsmodus abhängig. |

| count | Inkrementiert oder dekrementiert TCNT2 um 1 |

| direction | Auswahl zwischen Inkrement und Dekrement |

| clear | Löscht TCNT2 (alle Bits Null) |

| clkT2 | Zähler/Zeitgeber Takt |

| TOP | Signalisiert, dass TCNT2 den Maximalwert erreicht hat |

| BOTTOM | Signalisiert, dass TCNT2 den Minimalwert (Null) erreicht hat |

Abhängig vom gewählten Arbeitsmodus wird der Zähler mit Takt des Timer Clock clkT2 gelöscht, inkrementiert oder dekrementiert. Der Takt clkT2 kann durch eine externe oder interne Quelle erzeugt werden, die Einstellung erfolgt mit den Clock Select Bits CS22 bis CS20. Wenn keine Taktquelle ausgewählt ist (CS22 bis CS20 =000), dann wird der Zähler gestoppt. Auf den Wert von TCNT2 kann aber jederzeit zugegriffen werden, unabhängig davon, ob der Takt clkT2 vorhanden ist oder nicht. Das Beschreiben des Zählers durch die CPU hat Vorrang vor allen Lösch- und Zähl-Operationen des Zählers.

Eine Zählsequenz wird durch die Einstellungen des Waveform Generation Mode Bits (WGM21 bis WGM20) in dem TCCR2 Register bestimmt. Es besteht ein fester Zusammenhang zwischen der Arbeitsweise des Zählers und der erzeugten Wellenform am Output Compare Ausgang OC2.

Das Timer Counter Overflow Flag (TOV2) wird den Einstellungen der WGM2x Bits entsprechend gesetzt. Es kann genutzt werden, um einen Interrupt auszulösen.

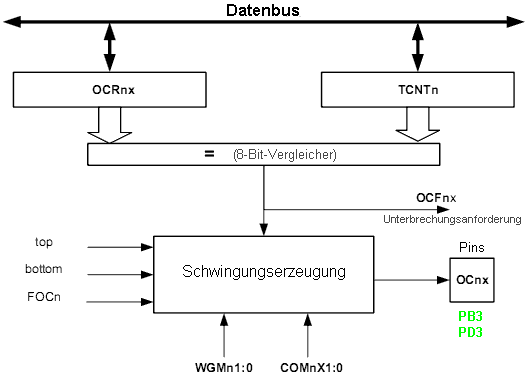

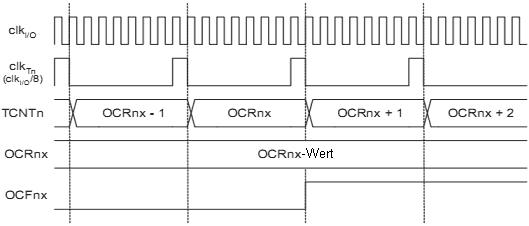

Die 8-bit-Vergleicher vergleichen kontinuierlich den Wert

des TCNT2-Registers mit den Output Compare Registern OCR2A und OCR2B.

Wenn die Werte von TCNT2 und OCR2x gleich sind,

signalisiert der Vergleicher die Übereinstimmung.

Durch die Übereinstimmung wird das Output Compare Flag (OCF2x)

mit dem nächsten Timer-Takt gesetzt.

Wenn freigegeben (OCIE2x = 1), erzeugt das Output Compare Flag einen Interrupt.

Das Flag wird automatisch gelöscht, wenn die Interruptroutine ausgeführt wird.

Es kann aber auch per Software gelöscht werden, indem eine 1

in das Bit geschrieben wird.

Der Waveform Generator verwendet das Übereinstimmungssginal,

um ein Ausgangssignal entsprechend der Einstellungen

der Waveform Generation Mode Bits (WGM21 bis WGM20)

und der Compate Output Mode Bits (COM21 und COM20) zu erzeugen.

Das TOP- und BOTTOM-Signal wird vom Waveform-Generator verwendet

um die besonderen Fälle von extremen Werten in einigen Betriebsmodi zu handhaben.

Die Register OCR2A und OCR2B sind zweifach gepuffert, wenn einer der PWM-Modi verwendet wird. Im normalen Clear Timer on Compare (CTC) Modus ist die zweifache Pufferung ausgeschaltet. Die zweifache Pufferung dient zur Synchronisation der laufenden Zählung mit sich verändernden TOP- und BOTTOM-Werten in den OCR2x-Registern. Die Synchronisation verhindert das Auftreten von unsymmetrischen PWM-Pulsen und macht den Ausgang glitchfrei.

Der Zugriff auf die OCR2x-Register sieht kompliziert aus, ist es aber nicht. Wenn die Pufferung freigegeben ist, dann greift die CPU auf das ORC2x-Pufferregister zu, wenn die Pufferung ausgeschaltet ist, dann greift die CPU direkt auf das OCR2-Register zu.

In Nicht-PWM-Modi kann der Übereinstimmungsausgang des Vergleiches auch erzwungen werden, indem man eine 1 in das Force Output Compare (FOC2) Bit schreibt. Bei der erzwungenen Vergleichsübereinstimmung wird weder ein OCF2x-Flag gesetzt noch der Timer gelöscht oder neu geladen. Allerdings wird der OC2x-Pin aktualisiert so als sei eine echte Vergleichsübereinstimmung aufgetreten. Ob das OC2x-Pin gelöscht, gesetzt oder gewechselt wird, wird durch die Einstellungen der Bits COM2x1 und COM2x0 festgelegt.

Alle Schreibversuche der CPU in das TCNT2-Register blockieren eine Vergleichsübereinstimmung die im nächsten Taktzyklus auftritt, auch wenn der Timer gestoppt ist. Dadurch ist des möglich, die OCR2-Register mit den gleichen Werten wie das TCNT2-Register zu beschreiben, ohne dass dadurch ein Interrupt ausgelöst wird.

Since writing TCNT2 in any mode of operation will block all compare matches for one timer clock cycle, there are risks involved when changing TCNT2 when using the Output Compare channel, independently of whether the Timer/Counter is running or not. If the value written to TCNT2 equals the OCR2x value, the compare match will be missed, resulting in incorrect waveform generation. Similarly, do not write the TCNT2 value equal to BOTTOM when the counter is downcounting. The setup of the OC2x should be performed before setting the Data Direction Register for the port pin to output. The easiest way of setting the OC2x value is to use the Force Output Compare (FOC2x) strobe bit in Normal mode. The OC2x Register keeps its value even when changing between Waveform Generation modes. Be aware that the COM2x1:0 bits are not double buffered together with the compare value. Changing the COM2x1:0 bits will take effect immediately.

Das Design der Output Compare Pin Logik erlaubt das Initialisieren des OC2 Zustandes bevor der Ausgang freigegeben wird. Einige COM21 / COM20 Kombinationen sind für spätere Funktionen reserviert (siehe Beschreibung der Register).

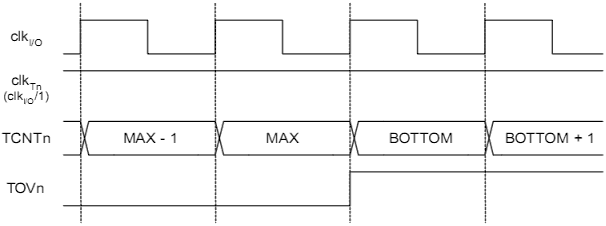

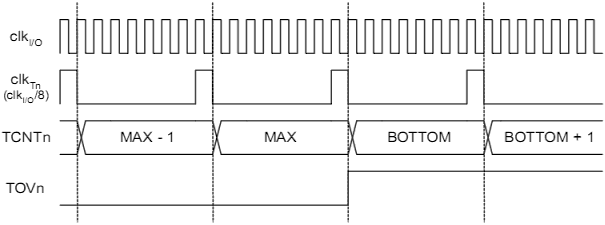

Der einfachste Betriebsmodus ist der normale Modus (WGM21 und WGM20 = 00). In diesem Modus zählt der Zähler immer vorwärts (inkrementieren) und wird nicht gelöscht. Wenn der Zähler seinen maximalen Wert erreicht (FFh) läuft er über und beginnt erneut bei seinem BOTTOM Wert 00h. Im normalen Modus wird das Timer Overflow Flag (TOV2) in dem Augenblick gesetzt, in dem das TCNT2 Register wieder 00 h wird. Das TOV2 Flag kann in diesem Fall wie ein 9 Bit betrachtet werden, dass aber nur gesetzt und nicht automatisch gelöscht wird. In Kombination mit dem Timer Overflow Interrupt, der das TOV2 Flag automatisch löscht, kann also die Auflösung des Timers durch die Software erheblich erweitert werden. Im normalen Modus sind keine Besonderheiten zu beachten, der Wert des TCNT2 Registers kann jederzeit überschrieben werden.

Die Output Compare Einheit kann verwendet werden, um Interrupts beim jeweiligen Zählerstand zu erzeugen. Das Erzeugen von Ausgangsfrequenzen im normal Modus wird nicht empfohlen, da dafür zu viel Prozessorkapazität verbraucht wird.

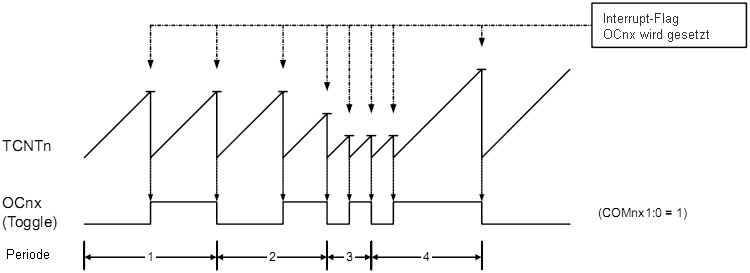

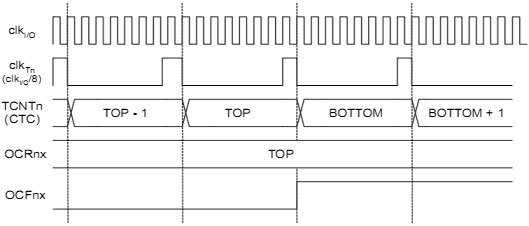

Im Clear Timer on Compare Modus (CTC) (WGM21 und WGM20 = 2) wird das Register OCR2 dazu verwendet, die Auflösung des Timers zu manipulieren. Im CTC Modus wird der Zähler gelöscht, wenn der Wert des Zählers (TNCT2) mit dem des OCR2 Registers übereinstimmt. Das Register OCR2 bestimmen also den Maximalwert des Zählers und somit seine Auflösung. Dieser Modus erlaubt eine größere Kontrolle der Compare Match Ausgangsfrequenz. Er vereinfacht auch das Zählen externer Ereignisse.

Das Zeitdiagramm des CTC Modus ist nachfolgend abgebildet.

Der Wert des Zählers (TCNT2) wächst so lange bis eine Vergleichsgleichheit mit dem OCR2 auftritt,

dann wird der Zähler (TCNT2) gelöscht.

Durch das OCF2 Flag kann ein Interrupt generiert werden, zu jedem Zeitpunkt, wenn der Wert des Zählers den TOP Wert erreicht, der durch das OCR2 Register vorgegeben ist. Wenn der Interrupt freigegeben ist, kann die Interruptroutine dazu verwendet werden, um den TOP Wert zu verändern. Das Einstellen des TOP Wertes in die Nähe des BOTTOM Wertes muss mit Vorsicht geschehen, wenn der Zähler ohne oder mit einem geringen Vorteiler betrieben wird, da der CTC Modus keine Zweifachbuffer Eigenschaft hat. Wenn ein neuer Wert in das OCR2 Register geschrieben wird, der kleiner als der aktuelle Wert des TCNT2 ist, so wird zunächst keine Vergleichsübereinstimmung erkannt. Der Zähler wird dann zunächst bis zu seinem maximalen Wert (FFh) laufen und von 00h erneut starten, erst dann kann eine Vergleichsübereinstimmung erkannt werden.

Beim Generieren einer Ausgangsfrequenz im CTC Modus kann der OC2 Ausgang so eingestellt werden, dass er seinen Zustand bei jeder Vergleichsübereinstimmung wechselt, indem die COM21 und COM20 Bits auf 1 gesetzt werden. Der OC2 Wert wird nicht am Port Pin erscheinen, wenn die Datenrichtung nicht auf Ausgang (DDR_OC2 = 1) eingestellt ist. Die erzeugte Ausgangswelle kann eine maximale Frequenz von fOC2 = fclk_I/O/2 haben, wenn OCR2 auf 00 gesetzt wird. Allgemein wird die Ausgangsfrequenz mit folgender Gleichung bestimmt:

| fOCn = | fclk_IO |

| 2 * N * (1 + OCR2A) |

Die Variable N steht für den Faktor des Vorteilers (1, 8, 32, 64, 128, 256 oder 1024).

Im normalen Modus wird das TOV2 Flag in dem selben Taktzyklus gesetzt, in dem der Zähler von seinem MAX Wert auf 0x00 wechselt.

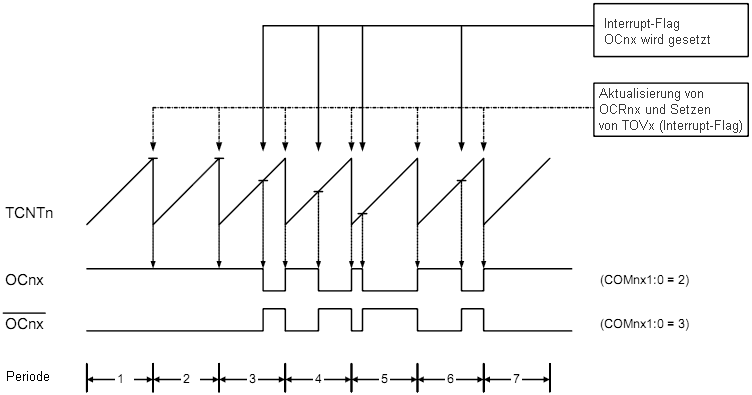

Der Fast PWM Modus (WGM21 bis WGM20 = 3) bietet eine hochfrequente Ausgangswelle. Der Fast PWM Modus unterscheidet sich von den anderen PWM Modi durch seine einfache Impulsflanke. Der Zähler zählt vom BOTTOM Wert bis zum TOP Wert und beginnt danach wieder mit dem BOTTOM Wert. Im nicht invertierenden Compare Output Mode wird der Output Compare (OC2) gelöscht, wenn eine Vergleichsübereinstimmung zwischen dem TCNT2 und OCR2 auftritt und wird gesetzt, wenn der BOTTOM Wert erreicht ist. Im invertierenden Output Compare Modus ist es genau umgekehrt. Durch die einfache Impulsflanke kann die Frequenz im Fast PWM Modus doppelt so hoch sein wie in den anderen PWM Modi, die mit einer doppelten Impulsflanke arbeiten. Die hohe Frequenz des PWM Signals ist günstig bei der Verwendung als Spannungsregulierung, Gleichrichtung und ähnlichen Digital-Analogwandler Anwendungen. Hohe Frequenzen erlauben kleine externe Komponenten (Spulen, Kondensatoren) wodurch die Systemkosten reduziert werden können.

Im Fast PWM Modus wird der Zähler so lange inkrementiert, bis der Zähler den MAX Wert erreicht.

Der Zähler wird dann mit dem folgenden Zyklus des Timertaktes gelöscht.

Das Zeitdiagramm des Fast PWM Modus ist im nachfolgenden Bild zu sehen.

Der Wert des TCNT2 ist als Histogramm um die einfache Impulsflanke darzustellen.

Auch der invertierende und der nicht invertierende Ausgang sind dargestellt.

Die kleinen horizontalen Linien an der TCNT2 Flanke kennzeichnen die Vergleichsübereinstimmung zwischen OCR2 und TCNT2.

Das Timer/Counter Overflow Flag (TOV2) wird jedes Mal gesetzt, wenn der Zähler seinen MAX Wert erreicht. Wenn der Interrupt freigegeben ist, kann die Interruptroutine dazu verwendet werden, um den Vergleichswerte zu aktualisieren.

Im Fast PWM Modus erlauben die Vergleichseinheiten das Erzeugen von PWM Signalen an dem OC2 Pins. Durch Setzen der COM21 und COM20 Bits auf 2 wird ein nicht invertiertes PWM-Signal erzeugt. Ein invertiertes PWM-Signal kann erzeugt werden, indem COM21 und COM20 auf 3 gesetzt werden. Um das PWM Signal am Port Pin sichtbar zu machen muss dieser als Ausgang konfiguriert werden (DDR_OC2 = 1). Das PWM Signal wird erzeugt indem das OC2 Register gesetzt (gelöscht) wird, wenn eine Vergleichsübereinstimmung zwischen OCR2 und TCNT2 besteht und das OC2 Register in dem Taktzyklus gelöscht (gesetzt) wird, in dem der Zähler durch den Wechsel von MAX zu BOTTOM gelöscht wird.

Die Frequenz des Ausgangssignals kann mit folgender Formel berechnet werden:

| fOCnPWM = | fclk_IO |

| N * 256 |

Die Variable N steht für den Faktor des Vorteilers (1, 8, 32, 64,128, 256 oder 1024).

Extreme Werte des OCR2 Register stellen spezielle Fälle bei der Erzeugung des PWM Signals im Fast PWM Modus dar. Wenn das OCR2 Register auf den gleichen Wert wie BOTTOM (also 00h) eingestellt wird, wird eine schmale Spitze am Ausgang erzeugt, die mit jedem MAX+1 Takt auftritt. Das Setzen des OCR2 Registers auf den MAX Wert wird zu einem konstanten High- oder Low-Pegel am Ausgang führen (abhängig ob invertierender oder nicht invertierender Ausgang eingestellt).

Eine Frequenz mit einem Tastverhältnis von 50% kann im Fast PWM Modus dadurch erreicht werden, indem man OC2 so einstellt, dass es seinen Pegel bei jeder Vergleichsübereinstimmung wechselt (COM21 und COM20 Bits auf 1). Die erzeugte Ausgangswelle kann eine maximale Frequenz von fOC2 = fclk_I/O/2 haben, wenn OCR2 auf 00 gesetzt wird. Diese Eigenschaft ist gleich dem OC2 Toggel im CTC Modus, mit der Ausnahme, dass die zweifach gebufferte Output Compare Einheit im Fast PWM Modus zur Verfügung steht.

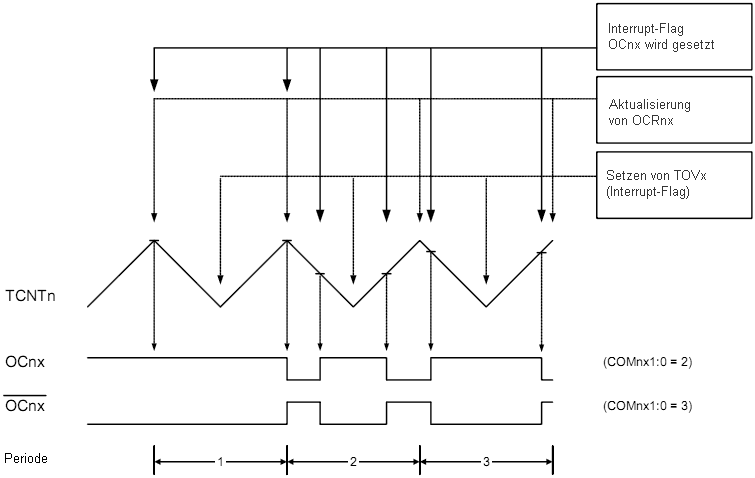

Der Phase Correct PWM Modus (WGM21 bis WGM20 = 1) bietet eine phasenkorrekte Ausgangswelle mit hoher Auflösung. Der Phase correct PWM Modus basiert auf einer zweifachen Impulsflanke. Der Zähler zählt vom BOTTOM Wert bis zum MAX Wert und wieder zurück vom MAX zum BOTTOM Wert. Im nicht invertierenden Compare Output Mode wird der Output Compare (OC2) gelöscht, wenn beim Hochzählen eine Vergleichsübereinstimmung zwischen dem TCNT2 und OCR2 auftritt und wird gesetzt wenn beim Runterzählen eine Vergleichsübereinstimmung auftritt. Im invertierenden Output Compare Modus ist es genau umgekehrt. Durch die zweifache Impulsflanke ist die Frequenz im phase correct PWM Modus niedriger als in den PWM Modi, die mit einer einfachen Impulsflanke arbeiten. Wegen der symmetrischen Eigenschaften der PWM Modi mit zweifacher Impulsflanke eigenen sich diese besonders für die Steuerung von Motoren.

Die PWM Auflösung im Phase Correct PWM Modus liegt fest bei 8 Bit.

Im Phase Correct PWM Modus wird der Zähler so lange inkrementiert,

bis der Zähler den festen Wert MAX erreicht.

Wenn der Zähler den MAX Wert erreicht hat, ändert er daraufhin seine Zählrichtung.

Der Wert von TCNT2 wird für einen Takt lang gleich dem MAX Wert sein.

Das Zeitdiagramm des Phase Correct PWM Modus ist im nachfolgenden Bild zu sehen.

Der Wert des TCNT2 ist als Histogramm abgebildet, um die zweifache Impulsflanke darzustellen.

Auch der invertierende und der nicht invertierende Ausgang sind dargestellt.

Die kleinen horizontalen Linien an der TCNT2 Flanke kennzeichnen

die Vergleichsübereinstimmung zwischen OCR2 und TCNT2.

as Timer/Counter Overflow Flag (TOV2) wird jedes Mal gesetzt, wenn der Zähler seinen BOTTOM Wert erreicht. Das Interrupt Flag kann genutzt werden, um einen Interrupt bei jedem Erreichen des BOTTOM Wertes durch den Zähler auszulösen.

Im Phase correct PWM Modus erlauben die Vergleichseinheiten das Erzeugen von PWM Signalen an den OC2 Pins. Durch Setzen der COM21 und COM20 Bits auf 2 wird ein nicht invertiertes PWM-Signal erzeugt. Ein invertiertes PWM-Signal kann erzeugt werden, indem COM21 und COM20 auf 3 gesetzt werden. Um das PWM Signal am Port Pin sichtbar zu machen muss dieser als Ausgang konfiguriert werden (DDR_OC2 = 1). Das PWM Signal wird erzeugt indem das OC2 Register gelöscht (gesetzt) wird, wenn beim Hochzählen eine Vergleichsübereinstimmung zwischen OCR2 und TCNT2 besteht und das OC2 Register wird gesetzt (gelöscht) wird, wenn beim Runterzählen eine Vergleichsübereinstimmung zwischen OCR2 und TCNT2 besteht.

Die Frequenz des Ausgangssignals kann mit folgender Formel berechnet werden:

| fOCnPWM = | fclk_IO |

| N * 510 |

Die Variable N steht für den Faktor des Vorteilers (1, 8, 32, 64, 128, 256 oder 1024).

Extreme Werte des OCR2 Register stellen spezielle Fälle bei der Erzeugung des PWM Signals im Phase correct PWM Modus dar. Wenn ein OCR2 Register auf den gleichen Wert wie BOTTOM eingestellt wird, bleibt der Ausgang permanant auf Low-Pegel Das Setzen des OCR2 Registers auf den MAX Wert wird zu einem konstanten High-Pegel am Ausgang führen (beim invertierenden Modus ist es dann genau anders herum).

Am Beginn der Periode 2 in obigen Abbild hat OC2 einen Wechsel von High nach Low, obwohl kein Compare Match auftritt. Der Grund für diesen Wechsel ist die erforderliche Symmetrie um den BOTTOM Punkt. Es kann zwei Fälle geben, in denen ein Wechsel ohne Compare Match auftritt:

Die nachfolgende Abbildung zeigt die grundsätzliche Arbeitsweise des Zähler/Zeitgeber.

Sie zeigt die Zählsequenz bis zum MAX Wert,

der in allen Modi außer dem Phase correct PWM Modus stattfindet.

Die Taktquelle für Zähler/Zeitgeber2 wird mit clkT2S bezeichnet. Der Takt clkT2S ist standardmäßig mit dem I/O Takt clkI/O verbunden. Durch Setzen des AS2 Bits im ASSR Register wird der Zähler/Zeitgeber2 asynchron durch den Takt am TOSC1 Pin getaktet. Dadurch kann Zähler/Zeitgeber2 als Echtzeitzähler verwendet werden. Wenn das AS2 Bit gesetzt ist, sind die Pins TOSC1 und TOSC2 vom Port B getrennt. Ein Quarz kann dann zwischen diesen beiden Pins angeschlossen werden und als unabhängige Taktquelle für Zähler/Zeitgeber2 dienen. Der Oszillator ist für Quarze mit einer Frequenz von 32,768 kHz optimiert. Das Anlegen eines externen Signals an TOSC1 wird nicht empfohlen.

Für Zähler/Zeitgeber2 sind folgende Auswahlmöglichkeiten für den Vorteiler vorhanden: clkT2S/8, clkT2S/32, clkT2S/64, clkT2S/128, clkT2S/256, clkT2S/1024. Zusätzlich kann clkT2S als 0 (Stopp) ausgewählt werden. Das Setzen des PSR2 Bits im SFIOR Regsiter resetet den Vorteiler. Dadurch kann mit einem vorhersehbaren Vorteiler gearbeitet werden.

Der 8-bit Zähler/Zeitgeber2 verwendet mehrere Register, die nachfolgend beschrieben werden.

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0xB0) | COM2A1 | COM2A0 | COM2B1 | COM2B0 | - | - | WGM21 | WGM20 | TCCR2A |

|---|---|---|---|---|---|---|---|---|---|

| Zugriff | R/W | R/W | R/W | R/W | R | R | R/W | R/W | |

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Wenn OC2A als Ausgangsfunktion verwendet werden, ist die Funktion der COM-Bits von den Einstellungen der WGM-Bits abhängig. Nachfolgende Tabelle zeigt die Funktionen der COM2Ax Bits, wenn die WGM-Bits auf den normalen oder den CTC-Modus eingestellt sind.

| COM2A1 .. COM2A0 | Funktion |

|---|---|

| 00 | Normale Portfunktion, OC2A abgeschaltet |

| 01 | Wechsel an OC2A bei Compare Match |

| 10 | Löschen von OC2A bei Compare Match (Low-Pegel) |

| 11 | Setzen von OC2A bei Compare Match (High-Pegel) |

| COM2A1 .. COM20 | Funktion |

|---|---|

| 00 | Normale Portfunktion, OC2A abgeschaltet |

| 01 | WGM22 = 0: Normal Port Operation, OC0A Disconnected. WGM22 = 1: Toggle OC2A on Compare Match. |

| 10 | Löschen von OC2A bei Compare Match, Setzen von OC2A bei TOP |

| 11 | Setzen von OC2A bei Compare Match, Löschen von OC2A bei TOP |

| COM2A1 .. COM2A0 | Funktion |

|---|---|

| 00 | Normale Portfunktion, OC2A abgeschaltet |

| 01 | WGM22 = 0: Normal Port Operation, OC2A Disconnected. WGM22 = 1: Toggle OC2A on Compare Match. |

| 10 | Löschen von OC2A bei Compare Match beim Hochzählen, Setzen von OC2A bei Compare Match beim Runterzählen |

| 11 | Setzen von OC2A bei Compare Match beim Hochzählen, Löschen von OC2A bei Compare Match beim Runterzählen |

Wenn OC2B als Ausgangsfunktion verwendet werden, ist die Funktion der COM-Bits von den Einstellungen der WGM-Bits abhängig. Die vorhergehenden Tabellen gelten entsprechend für COM2Bx.

| WGM22 .. WGM20 | Betriebsart | TOP | Aktualisierung von OCRxn | Setzen von TOV |

|---|---|---|---|---|

| 000 (0x00) | normal | 0xFF | sofort | 0xFF |

| 001 (0x01) | Phasenrichtige PWM | 0xFF | 0xFF | 0x00 |

| 010 (0x02) | CTC | OCR2A | sofort | 0xFF |

| 011 (0x03) | Schnelle PWM | 0xFF | 0x00 | 0xFF |

| 100 (0x04) | reserviert | |||

| 101 (0x05) | Phasenrichtige PWM | OCR2A | 0xFF | 0x00 |

| 110 (0x06) | reserviert | |||

| 111 (0x07) | Schnelle PWM | OCR2A | 0x00 | 0xFF |

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0xB1) | FOC2A | FOC2B | - | - | WGM22 | CS22 | CS21 | CS20 | TCCR2B |

|---|---|---|---|---|---|---|---|---|---|

| Zugriff | W | W | R | R | R/W | R/W | R/W | R/W | |

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Ein erzwungener Compare Match generiert keine Interrupts und löscht den Timer nicht. Das FOC2A-Bit wird immer als 0 gelesen.

Ein erzwungener Compare Match generiert keine Interrupts und löscht den Timer nicht. Das FOC2B-Bit wird immer als 0 gelesen.

| CS22 .. CS20 | Beschreibung |

|---|---|

| 000 | Zägler ist angehalten |

| 001 | clkT2S (ohne Vorteiler) |

| 010 | clkT2S/8 |

| 011 | clkT2S/32 |

| 100 | clkT2S/64 |

| 101 | clkT2S/128 |

| 110 | clkT2S/256 |

| 111 | clkT2S/1024 |

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0xB2) | TCNT2[7:0] | TCNT2 | |||||||

|---|---|---|---|---|---|---|---|---|---|

| Zugriff | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

Das Timer/Counter Register gibt einen direkten Zugriff auf den 8-bit Zähler bei Lese- und Schreiboparationen. Ein Verändern des Zählers (TCNT2) während der Zähler läuft, führt zu dem Risiko, dass ein Compare Match zwischen dem TCNT2 und den OCR2 Registern ausgelassen wird. Beim Schreiben in das TCNT2 Register werden die Compare Match im Folgetakt bei allen Vergleichseinheiten blockiert.

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0xB3) | OCR2A[7:0] | OCR2A | |||||||

|---|---|---|---|---|---|---|---|---|---|

| Zugriff | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

Das Output Compare Register enthält einen 8-bit Wert, der permanent mit dem Wert des Zählers (TCNT2) verglichen wird. Eine Übereinstimmung kann dazu genutzt werden, einen Interrupt auszulösen und/oder ein Ausgangssignal am Pin OC2A zu erzeugen.

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0xB4) | OCR2B[7:0] | OCR2B | |||||||

|---|---|---|---|---|---|---|---|---|---|

| Zugriff | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

Das Output Compare Register enthält einen 8-bit Wert, der permanent mit dem Wert des Zählers (TCNT2) verglichen wird. Eine Übereinstimmung kann dazu genutzt werden, einen Interrupt auszulösen und/oder ein Ausgangssignal am Pin OC2B zu erzeugen.

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x70) | - | - | - | - | - | OCIE2B | OCIE2A | TOIE2 | TIMSK2 |

|---|---|---|---|---|---|---|---|---|---|

| Zugriff | R | R | R | R | R | R/W | R/W | R/W | |

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x37) | - | - | - | - | - | OCF2B | OCF2A | TOV2 | TIFR2 |

|---|---|---|---|---|---|---|---|---|---|

| Zugriff | R | R | R | R | R | R/W | R/W | R/W | |

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Im PWM Modus wird das Bit gesetzt, wenn Timer/Counter2 seine Zählrichtung bei 0x00 umdreht.

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0xB6) | - | EXCLK | AS2 | TCN2UB | OCR2AUB | OCR2BUB | TCR2AUB | TCR2BUB | ASSR |

|---|---|---|---|---|---|---|---|---|---|

| Zugriff | R | R/W | R/W | R | R | R | R | R | |

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Solange ein Schreibvorgang läuft und das Busy-Flag des Timers gesetzt ist, wird ein weiterer Schreibversuch den neuen Wert zerstören und einen ungewollten Interrupt auslösen.

Die Mechanismen zum Lesen der TCNT2, ORC2 und TCCR2 Register sind anders. Wenn das TCNT2 Register gelesen wird, wird immer der Zähler gelesen, wenn die anderen beiden Register gelesen werden wird immer der Wert aus dem temporären Register gelesen.

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x43) | TSM | - | - | - | - | - | PSRASY | PSRSYNC | GTCCR |

|---|---|---|---|---|---|---|---|---|---|

| Zugriff | R/W | R | R | R | R | R | R/W | R/W | |

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |