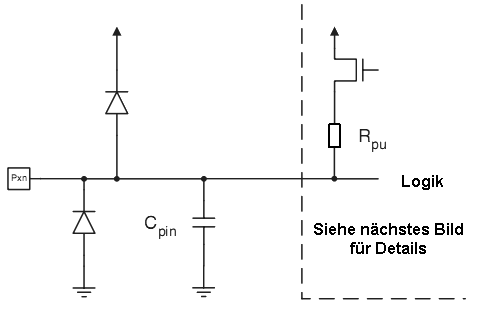

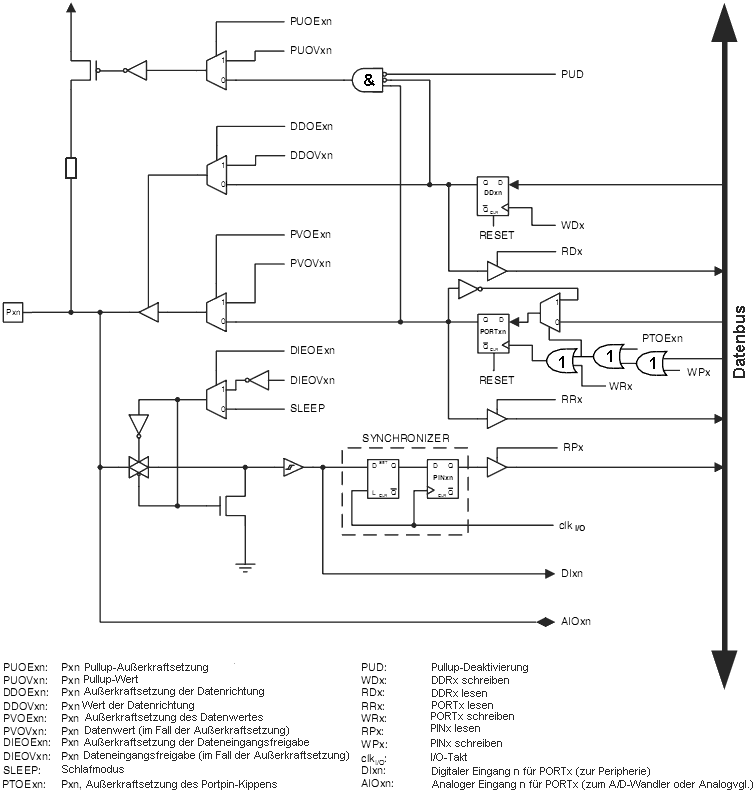

Bild 14-1: I/O-Pin-Beschaltung

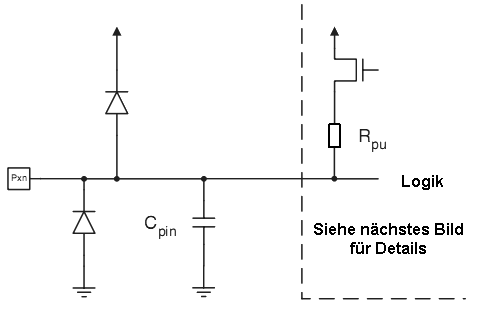

Für jeden Port stehen drei Register im I/O-Speicher zur Verfügung. Ein Daten-Register (PORTx), ein Richtungs-Register (DDRx) und eins für die Port Eingang-Pins (PINx). Die Port Eingang-Pin Register können nur gelesen werden, während die Daten- und die Richtungs-Register gelesen und beschrieben werden können. Zusätzlich können mit dem Pullup-Disable-Bit (PUD) im SFIOR-Register alle Pullup-Widerstände ausgeschaltet werden.

Die Verwendung der Portpins als digitale Ein- und Ausgänge wird nachfolgend beschrieben. Darüber hinaus haben viele Pins noch alternative Funktionen, die die periphere Funktionen des Bausteins unterstützen. Wie die alternativen Funktionen mit den Portpins zusammenhängen, wird im folgenden beschrieben, die detaillierten Funktionen sind dann in den Kapiteln zu den peripheren Modulen beschrieben. Das Verwenden eines Portpins mit seiner alternativen Funktion hat keinen Einfluss auf die anderen Pins eines Ports, die als digitale Ein- Ausgänge verwendet werden.

Das DDxn-Bit im DDRx-Register legt die Richtung des Pins fest. Wenn das DDxn-Bit mit einer logischen 1 beschrieben wird, dann ist der Pin als Ausgang konfiguriert. Ist das DDxn-Bit gelöscht, so arbeitet das Pin als Eingang.

Wenn das PORTxn-Bit mit einer logischen 1 beschrieben wird und das Pin als Eingang konfiguriert ist, dann sind die internen Pullup-Widerstände eingeschaltet. Um die Pullup-Widerstände auszuschalten, muss das PORTxn-Bit mit einer Null beschrieben werden oder das Pin als Ausgang konfiguriert werden. Die Portpins gehen in Tristate, wenn ein Reset auftritt, auch wenn keiner der Takte läuft.

Wenn das PORTxn-Bit mit einer logischen 1 beschrieben wird und der Pin als Ausgang konfiguriert ist, so wird der Port Pin auf High gesetzt. Umgekehrt wird der Port Pin auf Low gesetzt, wenn das PORTxn-Bit mit einer Null beschrieben wird während der Pin als Ausgang konfiguriert ist.

Der AVR muss dazu eine spezielle Befehlsabarbeitungslogik für SBI auf PINx-Register haben. Normalerweise würde man erwarten, dass SBI auf PINx zusätzlich alle PORTxn-Bits kippt, wo PINxn Eins ist.

Ein Umschalten zwischen Eingang mit Pullup-Widerstand und Ausgang mit Low-Pegel stellt das gleiche Problem dar. Hier muss der Anwender einen Zwischenschritt über Tristate (DDxn, PORTxn = 00) oder Ausgang mit High-Pegel (DDxn, PORTxn = 11) durchführen.

| DDxn | PORTxn | PUD(im MCUCR) | I/O | Pullup | Kommentar |

|---|---|---|---|---|---|

| 0 | 0 | X | Eingang | Nein | hochohmig (Tristate, Hi-Z) |

| 0 | 1 | 0 | Eingang | Ja | Pxn liefert Strom wenn von außen nach Low gezogen |

| 0 | 1 | 1 | Eingang | Nein | hochohmig (Tristate, Hi-Z) |

| 1 | 0 | X | Ausgang | Nein | Ausgang Low (Stromsenke) |

| 1 | 1 | X | Ausgang | Nein | Ausgang High (Stromquelle) |

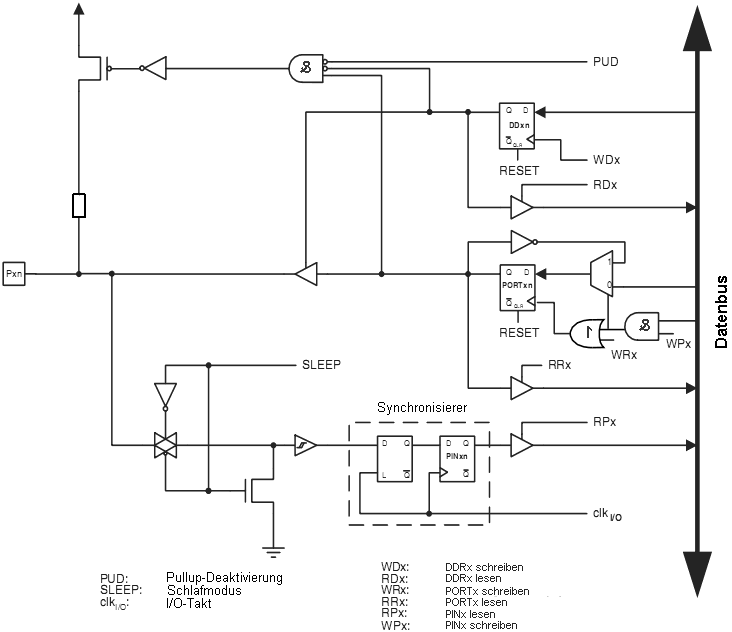

Wenn der durch die Software eingestellte Wert des Pins ausgelesen werden soll, muss ein NOP-Befehl wie nachfolgend dargestellt eingefügt werden, bevor der Wert wieder ausgelesen werden kann. Der OUT-Befehl setzt das SYNC LATCH Signal mit der positiven Flanke des Taktes, erst bei der darauf folgenden positiven Flanke wird der Wert dann in das PINxn Register übernommen und kann wieder ausgelesen werden. In diesem Fall beträgt die Verzögerung tpd durch den Synchronisierer 1 Taktzyklus.

| Beispiel in Assembler | ||

|---|---|---|

... ; Define pull-ups and set outputs high ; Define directions for port pins ldi r16,(1<<PB7)|(1<<PB6)|(1<<PB1)|(1<<PB0) ldi r17,(1<<DDB3)|(1<<DDB2)|(1<<DDB1)|(1<<DDB0) out PORTB,r16 out DDRB,r17 ; Insert nop for synchronization nop ; Read port pins in r16,PINB ... |

SLEEP wird bei Port Pins, die als externer Interrupt freigegeben sind, außer Kraft gesetzt. Wenn der externe Interrupt nicht freigegeben ist, beeinflusst das SLEEP Signal auch diese Pins. Das SLEEP Signal wird ebenfalls nicht wirksam, wenn die alternativen Funktionen des Port Pins verwendet werden.

Wenn ein logischer High-Pegel bei einem als asynchroner externer Interrupt konfigurierten Pin, mit Interrupt bei steigender oder fallender Flanke oder bei Wechsel der logischen Zustandes am Pin, während der externe Interrupt nicht freigegeben ist anliegt, wird das dazugehörige Interrupt Flag gesetzt, wenn aus den o.g. Sleep Modi zurückgekehrt wird und diese das Festhalten von Pegeländerungen beinhalten.

Die einfachste Möglichkeit, einen definierten Pegel an einem unbeschalteten Eingang zu erreichen, ist das Einschalten der internen Pullup-Widerstände. In diesem Fall werden die internen Pullup-Widerstände aber während eines Resets abgeschaltet. Wenn ein geringer Stromverbrauch während eines Resets notwendig ist, dann sollten also besser externe Pullup- oder Pulldown-Widerstände verwendet werden. Die ungenutzten Pins direkt mit UCC oder GND zu verbinden ist nicht empfehlenswert, da in den Fällen, in denen sie versehentlich als Ausgänge konfiguriert werden, sehr hohe Ströme fließen können.

| Signalname | Bedeutung | Beschreibung |

|---|---|---|

| PUOE | Pullup Override Freigabe | Wenn dieses Signal gesetzt ist, wird die Freigabe der Pull-up-Widerstände durch das Signal PUOV kontrolliert. Wenn dieses Signal gelöscht ist, sind die Pull-up Widerstände freigegeben, wenn DDxn, PORTxn, PUD = 010 sind. |

| PUOV | Pullup Override Wert | Wenn PUOE gesetzt ist, werden die Pull-up Widerstände freigegeben/gesperrt, wenn PUOV gesetzt/gelöscht ist, unabhängig vom Zustand der DDxn, PORTxn und PUD Register Bits. |

| DDOE | Datenrichtungs-Überschreib-Freigabe | Wenn dieses Signal gesetzt ist, wird die Freigabe des Ausgangstreibers mit dem DDOV-Signal kontrolliert. Wenn das DDOE Signal gelöscht ist, wird der Ausgangstreiber durch das DDxn Bit freigegeben. |

| DDOV | Datenrichtungs-Überschreib-Wert | Wenn DDOE gesetzt ist, werden die Ausgangstreiber freigegeben/gesperrt, wenn das DDOV-Signal gesetzt/gelöscht ist, unabhängig vom Zustand der DDxn Register Bits. |

| PVOE | Port-Ausgabe-Überschreib-Freigabe | Wenn dieses Signal gesetzt ist und der Ausgangstreiber freigegeben ist, wird der Zustand des Ports durch das PVOV Signal kontrolliert. Ist das PVOE Signal gelöscht und der Ausgangstreiber freigegeben, so wird der Zustand des Ports über die PORTxn Register Bits kontrolliert. |

| PVOV | Port-Ausgabe-Überschreib-Wert | Wenn PVOE gesetzt ist, dann wird der Zustand des Ports durch das PVOV Signal bestiummt, unabhängig von den Einstellungen des PORTxn Register Bits. |

| DIEOV | Digitale Eingangsfreigabe-Überschreib-Freigabe | Wenn dieses Bit gesetzt ist, wird die Freigabe der digitalen Eingänge durch das DIEOV Signal gesteuert. Wenn das Signal gelöscht ist, wird die Freigabe der digitalen Eingänge dadurch bestimmt, ob sich der Controller im normalen Modus befindet oder in einem Sleep Modus. |

| DIEOV | Digitale Eingangsfreigabe-Überschreib-Wert | Wenn das DIEOE Signal gesetzt ist, werden die digitalen Eingänge freigegeben/gesperrt, wenn das DIEOV Signal gesetzt/gelöscht ist, unabhängig davon, ob sich der Controller im normalen Modus befindet oder in einem Sleep Modus. |

| DI | Digitaler Eingang | Dies ist der digitale Eingang für die alternativen Funktionen. Die Schaltung zeigt, dass dieses Signal am Ausgang des Schmitt-Triggers aber vor dem Synchronisierer abgegriffen wird. Außer wenn der digitale Eingang als Taktquelle verwendet wird, benutzen die alternativen Funktionen einen eigenen Synchronisierer. |

| AIO | Analoger Ein-/Ausgang | Dies ist der analoge Eingang/Ausgang zu/von den alternativen Funktionen. Das Signal ist direkt mit dem Pin verbunden und kann bidirektional verwendet werden. |

| Portpin | Alternative Funktionen |

|---|---|

| PB7 | XTAL2 (Chip Clock Oszillator-Ausgang)

TOSC2 (Zähler/Zeitgeber2 Oszillator-Ausgang) PCINT7 (Pegelwechselinterrupt 7) |

| PB6 | XTAL1 (Chip Clock Oszillator-Eingang oder externer Takteingang)

TOSC1 (Zähler/Zeitgeber2 Oszillator-Eingang) PCINT6 (Pegelwechselinterrupt 6) |

| PB5 | SCK (SPI Bus Master Takteingang)

PCINT5 (Pegelwechselinterrupt 5) |

| PB4 | MISO (SPI Bus Master Eingang / Slave Ausgang)

PCINT4 (Pegelwechselinterrupt 4) |

| PB3 | MOSI (SPI Bus Master Ausgang / Slave Eingang)

OC2A (Zähler/Zeitgeber2 Ausgang Compare Match A) PCINT3 (Pegelwechselinterrupt 3) |

| PB2 | SS (SPI Bus Master Slave select)

OC1B (Zähler/Zeitgeber1 Ausgang Compare Match B) PCINT2 (Pegelwechselinterrupt 2) |

| PB1 | OC1A (Zähler/Zeitgeber1 Ausgang Compare Match A)

PCINT1 (Pegelwechselinterrupt 1) |

| PB0 | ICP1 (Zähler/Zeitgeber1 Capture-Eingang)

CLKO (Geteilter Systemtakt-Ausgang) PCINT0 (Pegelwechselinterrupt 0) |

TOSC2: Wird nur verwendet, wenn der interne RC-Oszillator als Taktquelle für den Baustein ausgewählt wurde und der asynchrone Zeitgeber durch die richtigen Einstellungen im ASSR Register freigegeben wurde. Wenn das AS2 Bit im ASSR Register gesetzt ist um die asynchrone Taktung von Zähler/Zeitgeber2 freizugeben, wird PB7 von dem Port getrennt und wird zum invertierenden Ausgang des Oszillatorverstärkers. In diesem Modus wird ein Quarzoszillator an den Pin angeschlossen, der Pin kann dann nicht als digitaler I/O verwendet werden.

Wenn PB7 als Taktpin verwendet wird, werden DDB7, PORTB7 und PINB7 immer als 0 gelesen.

PCINT7: Pegelwechsel-Interruptquelle Nummer 7. Das Pin kann als externe Interruptquelle dienen.

TOSC1: Wird nur verwendet, wenn der interne RC-Oszillator als Taktquelle für den Baustein ausgewählt wurde und der asynchrone Zeitgeber durch die richtigen Einstellungen im ASSR Register freigegeben wurde. Wenn das AS2 Bit im ASSR Register gesetzt ist um die asynchrone Taktung von Zähler/Zeitgeber2 freizugeben, wird PB6 von dem Port getrennt und wird zum Eingang des invertierenden Oszillatorverstärkers. In diesem Modus wird ein Quarzoszillator an den Pin angeschlossen, der Pin kann dann nicht als digitaler I/O verwendet werden.

Wenn PB6 als Takt Pin verwendet wird, werden DDB6, PORTB6 und PINB6 immer als 0 gelesen.

PCINT6: Pegelwechsel-Interruptquelle Nummer 6. Das Pin kann als externe Interruptquelle dienen.

PCINT5: Pegelwechsel-Interruptquelle Nummer 5. Das Pin kann als externe Interruptquelle dienen.

PCINT4: Pegelwechsel-Interruptquelle Nummer 4. Das Pin kann als externe Interruptquelle dienen.

OC2: (Output Compare 2) Das Pin kann als Ausgang für den Zähler/Zeitgeber2 Compare Match dienen. Damit kann dieses PWM-Signale ausgeben. Das Pin muss hierfür als Ausgang konfiguriert werden (DDB3 auf 1 setzen).

PCINT3: Pegelwechsel-Interruptquelle Nummer 3. Das Pin kann als externe Interruptquelle dienen.

OC1B: (Output Compare 1 B) Das Pin kann als Ausgang für den Zähler/Zeitgeber1 Compare Match B dienen. Damit kann dieses PWM-Signale ausgeben. Das Pin muss hierfür als Ausgang konfiguriert werden (DDB2 auf 1 setzen).

PCINT2: Pegelwechsel-Interruptquelle Nummer 2. Das Pin kann als externe Interruptquelle dienen.

PCINT1: Pegelwechsel-Interruptquelle Nummer 1. Das Pin kann als externe Interruptquelle dienen.

Die nachfolgenden Tabellen zeigen die alternativen Funktionen von Port B und deren übergeordneten Signale. SPI MSTR INPUT und SPI SLAVE OUTPUT bilden das MISO Signal, während das MOSI Signal in SPI-Master-Ausgang und SPI-Slave-Eingang aufgeteilt wird.

PCINT0: Pegelwechsel-Interruptquelle Nummer 0. Das Pin kann als externe Interruptquelle dienen.

Tabelle 14-4 und Tabelle 14-5 setzen die alternativen Functionen von Port B in Verhältnis zu den überschreibenden Signalen im Bild 14-5. SPI-Master-Eingang und SPI-Slave-Ausgang bilden das MISO-Signal, während MOSI entweder SPI-Master-Ausgang und SPI-Slave-Eingang ist.

| Signalname | PB7/XTAL2/ TOSC2/PCINT7(1)

| PB6/XTAL1/ TOSC1/PCINT6(1)

| PB5/SCK/ PCINT5 | PB4/MISO/ PCINT4

| PUOE | INTRC • EXTCK + AS2

| INTRC + AS2 | SPE • MSTR | SPE • MSTR

| PUOV | 0 | 0 | PORTB5 • PUD | PORTB4 • PUD

| DDOE | INTRC • EXTCK + AS2

| INTRC + AS2 | SPE • MSTR | SPE • MSTR

| DDOV | 0 | 0 | 0 | 0

| PVOE | 0 | 0 | SPE • MSTR | SPE • MSTR

| PVOV | 0 | 0 | SCK-Ausgang | SPI-Slave-Ausgang

| DIEOE | INTRC • EXTCK + AS2 + PCINT7 • PCIE0

| INTRC + AS2 + PCINT6 • PCIE0 | PCINT5 • PCIE0 | PCINT4 • PCIE0

| DIEOV | (INTRC + EXTCK) • AS2

| INTRC • AS2 | 1 | 1

| DI | PCINT7-Eingang | PCINT6-Eingang | PCINT5-Eingang | SCK-Eingang PCINT4-Eingang | SPI-Master-Eingang AIO | Oszillator-Ausgang | Oszillator/Takt-Eingang | – | –

| |

|---|

| Signalname | PB3/MOSI/ OC2/PCINT3 | PB2/SS/ OC1B/PCINT2 | PB1/OC1A/ PCINT1 | PB0/ICP1/ PCINT0 |

|---|---|---|---|---|

| PUOE | SPE • MSTR | SPE • MSTR | 0 | 0 |

| PUOV | PORTB3 • PUD | PORTB2 • PUD | 0 | 0 |

| DDOE | SPE • MSTR | SPE • MSTR | 0 | 0 |

| DDOV | 0 | 0 | 0 | 0 |

| PVOE | SPE • MSTR + OC2A-Freigabe | OC1B-Freigabe | OC1A-Freigabe | 0 |

| PVOV | SPI-Master-Ausgang + OC2A | OC1B | OC1A | 0 |

| DIEOE | PCINT3 • PCIE0 | PCINT2 • PCIE0 | PCINT1 • PCIE0 | PCINT0 • PCIE0 |

| DIEOV | 1 | 1 | 1 | 1 |

| DI | PCINT3-Eingang SPI-Slave-Eingang | PCINT2-Eingang SPI SS | PCINT1-Eingang | PCINT0-Eingang ICP1-Eingang |

| AIO | – | – | – | – |

| Portpin | Alternative Funktionen |

|---|---|

| PC6 | RESET (Reset-Pin)

PCINT14 (Pegelwechselinterrupt 14) |

| PC5 | ADC5 (ADU-Eingang Kanal 5)

SCL (Zweidraht-Bus-Taktleitung) PCINT13 (Pegelwechselinterrupt 13) |

| PC4 | ADC4 (ADU-Eingang Kanal 4)

SDA (Zweidraht-Bus-Datenleitung) PCINT12 (Pegelwechselinterrupt 12) |

| PC3 | ADC3 (ADU-Eingang Kanal 3)

PCINT11 (Pegelwechselinterrupt 11) |

| PC2 | ADC2 (ADU-Eingang Kanal 2)

PCINT10 (Pegelwechselinterrupt 10) |

| PC1 | ADC1 (ADU-Eingang Kanal 1)

PCINT9 (Pegelwechselinterrupt 9) |

| PC0 | ADC0 (ADU-Eingang Kanal 0)

PCINT8 (Pegelwechselinterrupt 8) |

Wenn PC6 als Reseteingang verwendet wird, werden die Bits DDC6, PORTC6 und PINC6 immer als 0 gelesen.

PCINT14: Pegelwechsel-Interruptquelle Nummer 14. Das Pin kann als externe Interruptquelle dienen.

PCINT13: Pegelwechsel-Interruptquelle Nummer 13. Das Pin kann als externe Interruptquelle dienen.

PCINT12: Pegelwechsel-Interruptquelle Nummer 12. Das Pin kann als externe Interruptquelle dienen.

PCINT11: Pegelwechsel-Interruptquelle Nummer 11. Das Pin kann als externe Interruptquelle dienen.

PCINT10: Pegelwechsel-Interruptquelle Nummer 10. Das Pin kann als externe Interruptquelle dienen.

PCINT9: Pegelwechsel-Interruptquelle Nummer 9. Das Pin kann als externe Interruptquelle dienen.

PCINT8: Pegelwechsel-Interruptquelle Nummer 8. Das Pin kann als externe Interruptquelle dienen.

Die nachfolgenden Tabellen zeigen die alternativen Funktionen von Port C und deren überschreibenden Signale.

| Signalname | PC6/RESET/ PCINT14 | PC5/SCL/ADC5/ PCINT13 | PC4/SDA/ADC4/PCINT12 | ||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| PUOE | RSTDISBL | TWEN | TWEN | ||||||||||||||||||||||||||||||||

| PUOV | 1 | PORTC5 • PUD | PORTC4 • PUD

| DDOE | RSTDISBL | TWEN | TWEN

| DDOV | 0 | SCL_OUT | SDA_OUT

| PVOE | 0 | TWEN | TWEN

| PVOV | 0 | 0 | 0

| DIEOE | RSTDISBL + PCINT14 • PCIE1 | PCINT13 • PCIE1 + ADC5D | PCINT12 • PCIE1 + ADC4D

| DIEOV | RSTDISBL | PCINT13 • PCIE1 | PCINT12 • PCIE1

| DI | PCINT14-Eingang | PCINT13-Eingang | PCINT12-Eingang

| AIO | RESET-Eingang | ADC5-Eingang / SCL-Eingang | ADC4-Eingang / SDA-Eingang

| |

| Signalname | PC3/ADC3/ PCINT11 | PC2/ADC2/ PCINT10 | PC1/ADC1/ PCINT9 | PC0/ADC0/ PCINT8 |

|---|---|---|---|---|

| PUOE | 0 | 0 | 0 | 0 |

| PUOV | 0 | 0 | 0 | 0 |

| DDOE | 0 | 0 | 0 | 0 |

| DDOV | 0 | 0 | 0 | 0 |

| PVOE | 0 | 0 | 0 | 0 |

| PVOV | 0 | 0 | 0 | 0 |

| DIEOE | PCINT11 • PCIE1 + ADC3D | PCINT10 • PCIE1 + ADC2D | PCINT9 • PCIE1 + ADC1D | PCINT8 • PCIE1 + ADC0D |

| DIEOV | PCINT11 • PCIE1 | PCINT10 • PCIE1 | PCINT9 • PCIE1 | PCINT8 • PCIE1 |

| DI | PCINT11-Eingang | PCINT10-Eingang | PCINT9-Eingang | PCINT8-Eingang |

| AIO | ADC3-Eingang | ADC2-Eingang | ADC1-Eingang | ADC0-Eingang |

| Portpin | Alternative Funktionen |

|---|---|

| PD7 | AIN1 (Analogvergleicher, negativer Eingang)

PCINT23 (Pegelwechselinterrupt 23) |

| PD6 | AIN0 (Analogvergleicher, positiver Eingang)

OC0A (Zähler/Zeitgeber0: Ausgang für Compare Match A) PCINT22 (Pegelwechselinterrupt 22) |

| PD5 | T1 (Zähler/Zeitgeber1 Zähleingang)

OC0B (Zähler/Zeitgeber0: Ausgang für Compare Match B) PCINT21 (Pegelwechselinterrupt 21) |

| PD4 | XCK (USART Taktein-/-ausgang)

T0 (Zähler/Zeitgeber0 Zähleingang) PCINT20 (Pegelwechselinterrupt 20) |

| PD3 | INT1 (Eingang Interrupt 1)

OC2B (Zähler/Zeitgeber2: Ausgang für Compare Match B) PCINT19 (Pegelwechselinterrupt 19) |

| PD2 | INT0 (Eingang Interrupt 0)

PCINT18 (Pegelwechselinterrupt 18) |

| PD1 | TXD (USART Datenausgang)

PCINT17 (Pegelwechselinterrupt 17) |

| PD0 | RXD (USART Dateneingang)

PCINT16 (Pegelwechselinterrupt 16) |

PCINT23: Pegelwechsel-Interruptquelle Nummer 23. Das Pin kann als externe Interruptquelle dienen.

PCINT22: Pegelwechsel-Interruptquelle Nummer 22. Das Pin kann als externe Interruptquelle dienen.

OC0B: (Output Compare 0 B) Das Pin kann als Ausgang für den Zähler/Zeitgeber0 Compare Match B dienen. Damit kann dieses PWM-Signale ausgeben. Das Pin muss hierfür als Ausgang konfiguriert werden (DDD5 auf 1 setzen).

PCINT21: Pegelwechsel-Interruptquelle Nummer 21. Das Pin kann als externe Interruptquelle dienen.

T0: Externe Quelle für den Zähler 0

PCINT20: Pegelwechsel-Interruptquelle Nummer 20. Das Pin kann als externe Interruptquelle dienen.

OC2B: (Output Compare 2 B) Das Pin kann als Ausgang für den Zähler/Zeitgeber2 Compare Match B dienen. Damit kann dieses PWM-Signale ausgeben. Das Pin muss hierfür als Ausgang konfiguriert werden (DDD3 auf 1 setzen).

PCINT19: Pegelwechsel-Interruptquelle Nummer 19. Das Pin kann als externe Interruptquelle dienen.

PCINT18: Pegelwechsel-Interruptquelle Nummer 18. Das Pin kann als externe Interruptquelle dienen.

PCINT17: Pegelwechsel-Interruptquelle Nummer 17. Das Pin kann als externe Interruptquelle dienen.

PCINT16: Pegelwechsel-Interruptquelle Nummer 16. Das Pin kann als externe Interruptquelle dienen.

Die nachfolgenden Tabellen zeigen die alternativen Funktionen von Port D und deren überschreibenden Signale.

| Signalname | PD7/AIN1/ PCINT23 | PD6/AIN0/OC0A/ PCINT22 | PD5/T1/OC0B/ PCINT21 | PD4/XCK/T0/ PCINT20 |

|---|---|---|---|---|

| PUOE | 0 | 0 | 0 | 0 |

| PUO | 0 | 0 | 0 | 0 |

| DDOE | 0 | 0 | 0 | 0 |

| DDOV | 0 | 0 | 0 | 0 |

| PVOE | 0 | OC0A-Freigabe | OC0B-Freigabe | UMSEL |

| PVOV | 0 | OC0A | OC0B | XCK-Ausgang |

| DIEOE | PCINT23 • PCIE2 | PCINT22 • PCIE2 | PCINT21 • PCIE2 | PCINT20 • PCIE2 |

| DIEOV | 1 | 1 | 1 | 1 |

| DI | PCINT23-Eingang | PCINT22-Eingang | PCINT21-Eingang T1-Eingang | PCINT20-Eingang XCK-Eingang T0-Eingang |

| AIO | AIN1-Eingang | AIN0-Eingang | – | – |

| Signalname | PD3/OC2B/INT1/ PCINT19 | PD2/INT0/ PCINT18 | PD1/TXD/ PCINT17 | PD0/RXD/ PCINT16 | ||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| PUOE | 0 | 0 | TXEN | RXEN | ||||||||||||||||||||||||||||||||||||||||

| PUO | 0 | 0 | 0 | PORTD0 • PUD

| DDOE | 0 | 0 | TXEN | RXEN

| DDOV | 0 | 0 | 1 | 0

| PVOE | OC2B-Freigabe | 0 | TXEN | 0

| PVOV | OC2B | 0 | TXD | 0

| DIEOE | INT1-Freigabe + PCINT19 • PCIE2 | INT0-Freigabe + PCINT18 • PCIE1 | PCINT17 • PCIE2 | PCINT16 • PCIE2

| DIEOV | 1 | 1 | 1 | 1

| DI | PCINT19-Eingang | INT1-Eingang PCINT18-Eingang | INT0-Eingang PCINT17-Eingang | PCINT16-Eingang | RXD AIO | – | – | – | –

| |

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x55) | - | BODS | BODSE | PUD | - | - | IVSEL | IVCE | MCUCR |

|---|---|---|---|---|---|---|---|---|---|

| Zugriff | R | R/W | R/W | R/W | R | R | R/W | R/W | |

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x25) | PORTB7 | PORTB6 | PORTB5 | PORTB4 | PORTB3 | PORTB2 | PORTB1 | PORTB0 | PORTB |

|---|---|---|---|---|---|---|---|---|---|

| Zugriff | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x24) | DDB7 | DDB6 | DDB5 | DDB4 | DDB3 | DDB2 | DDB1 | DDB0 | DDRB |

|---|---|---|---|---|---|---|---|---|---|

| Zugriff | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x23) | PINB7 | PINB6 | PINB5 | PINB4 | PINB3 | PINB2 | PINB1 | PINB0 | PINB |

|---|---|---|---|---|---|---|---|---|---|

| Zugriff | R | R | R | R | R | R | R | R | |

| Startwert | - | - | - | - | - | - | - | - |

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x28) | - | PORTC6 | PORTC5 | PORTC4 | PORTC3 | PORTC2 | PORTC1 | PORTC0 | PORTC |

|---|---|---|---|---|---|---|---|---|---|

| Zugriff | R | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x27) | - | DDC6 | DDC5 | DDC4 | DDC3 | DDC2 | DDC1 | DDC0 | DDRC |

|---|---|---|---|---|---|---|---|---|---|

| Zugriff | R | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x26) | - | PINC6 | PINC5 | PINC4 | PINC3 | PINC2 | PINC1 | PINC0 | PINC |

|---|---|---|---|---|---|---|---|---|---|

| Zugriff | R | R | R | R | R | R | R | R | |

| Startwert | 0 | - | - | - | - | - | - | - |

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x2B) | PORTD7 | PORTD6 | PORTD5 | PORTD4 | PORTD3 | PORTD2 | PORTD1 | PORTD0 | PORTD |

|---|---|---|---|---|---|---|---|---|---|

| Zugriff | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x2A) | DDD7 | DDD6 | DDD5 | DDD4 | DDD3 | DDD2 | DDD1 | DDD0 | DDRD |

|---|---|---|---|---|---|---|---|---|---|

| Zugriff | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x29) | PIND7 | PIND6 | PIND5 | PIND4 | PIND3 | PIND2 | PIND1 | PIND0 | PIND |

|---|---|---|---|---|---|---|---|---|---|

| Zugriff | R | R | R | R | R | R | R | R | |

| Startwert | - | - | - | - | - | - | - | - |