11. Systemkontrolle und Reset

11.1 Reset = Neustart

Während eines Resets werden alle I/O-Register auf ihre Initialwerte eingestellt

und das Programm wird ab der Adresse des Reset-Vektors gestartet.

Für ATmega168/328 muss der Befehl am Reset-Vektor ein JMP-Befehl sein,

der zum Initialisierunskode springt.

Für ATmega48/88 muss der Befehl ein RJMP-Befehl sein.

Wenn das Programm keinerlei Interrupts verwendet,

kann regulärer Programmkode an der Adresse des Reset-Vekotrs beginnen.

Dies gilt auch in den Fällen, in denen der Reset-Vektor

im Applikations-Sektor und die Interrupt-Vektoren im Boot-Sektor

liegen bzw. umgekehrt (nur ATmega88/168/328).

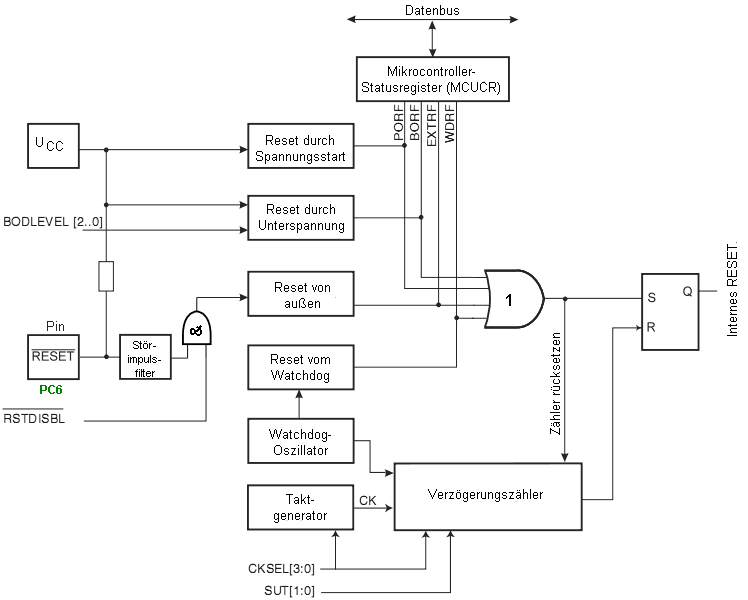

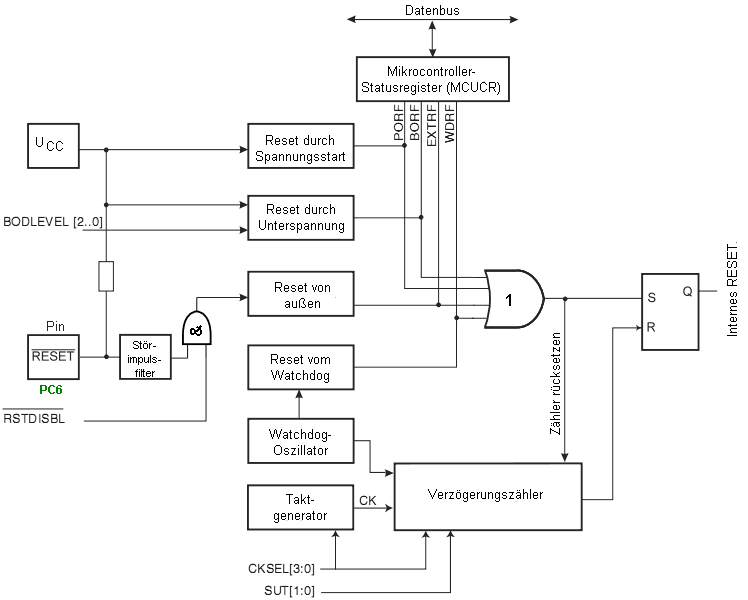

Die Schaltung im Bild 11-1 zeigt die Reset-Logik.

Tabelle 29-11 definiert elektrische Parameter der Reset-Schaltung.

Das Zurücksetzen der I/O-Register auf ihre Resetwerte geschieht unmittelbar

durch den Reset, die verschiedenen Takte müssen dafür nicht aktiv sein.

Nachdem die Resetbedingungen aller Resetquellen verschwunden sind,

wird ein interner Verzögerungszähler gestartet,

der den internen Rest verlängert.

Dadurch kann die Versorgungsspannung einen stabilen Pegel erreicht,

bevor mit der normalen Abarbeitung des Programms begonnen wird.

Die Verzögerungszeit des Verzögerungszählers wird mit den CKSEL-Fuses

eingestellt — siehe Auswahl der Taktquellen.

11.2 Reset-Quellen

Der Schaltkreis hat vier verschiedene Resetquellen:

- Power-on Reset. Der Controller wird neu gestartet,

wenn die Versorgungsspannung unterhalb des Power-on-Reset

Schwellwertes UPOT liegt.

- Externer Reset. Der Controller wird neu gestartet,

wenn ein Low-Pegel am RESET-Pin für länger

als die minimale Länge eines Taktpulses anliegt.

- Watchdog Reset. Der Controller wird neu gestartet,

wenn bei freigeschaltetem Watchdog der Watchdog-Timer überläuft.

- Brown-out Reset. Der Controller wird neu gestartet,

wenn bei freigeschalteter Unterspannungserkennung

die Versorgungsspannung unter den Unterspannungsdetektor-Schwellwert UBOT absinkt.

Bild 11-1: Reset-Logik

11.3 Power-on-Reset (POR)

Ein Power-on-Reset-Impuls wird durch eine Schaltung auf dem Chip erzeugt.

Die nominellen Schwellwerte sind in System- und Reset-Kennwerte dargestellt.

Ein POR wird immer dann erzeugt, wenn UCC unterhalb der Schwellwerte liegt.

Die POR-Schaltung kann genutzt werden, um einen Hochlauf-Reset auszulösen,

aber auch, um ein Fehlen der Versorgungsspannung zu erkennen.

Die Power-on-Reset-Schaltung stellt sicher,

dass der Baustein einen sauberen Reset beim Einschalten der Versorgungsspannung ausführt.

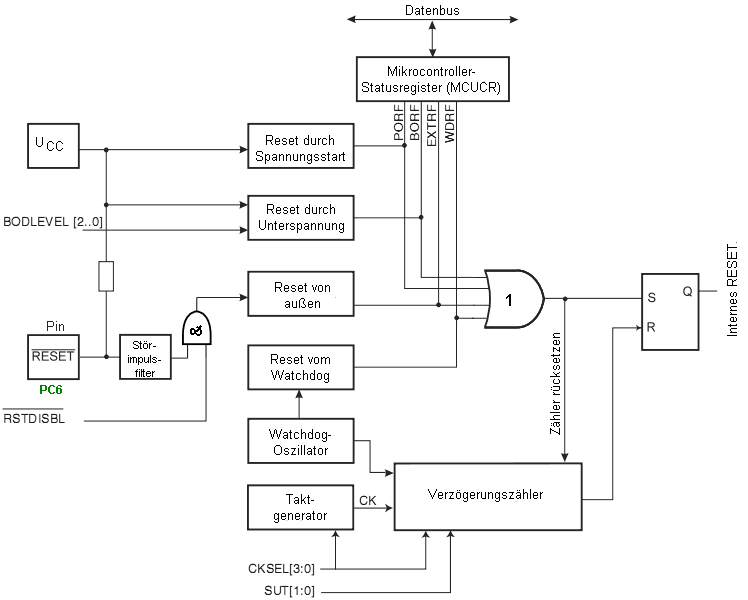

Wird die Power-on-Schwellwertspannung erreicht, wird ein Verzögerungszähler gestartet,

der die Verzögerung bestimmt,

für die der Baustein nach dem Einschalten der Versorgungsspannung im Reset bleibt.

Das Reset-Signal wird wiederholt und ohne Verzögerung erzeugt,

wenn UCC unter den Auslösepegel sinkt.

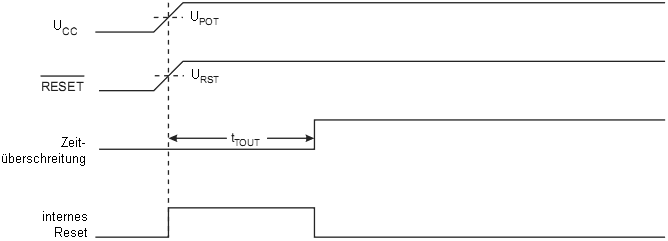

Bild 11-2: Mikrocontroller-Hochlauf, RESET an UCC angeschlossen

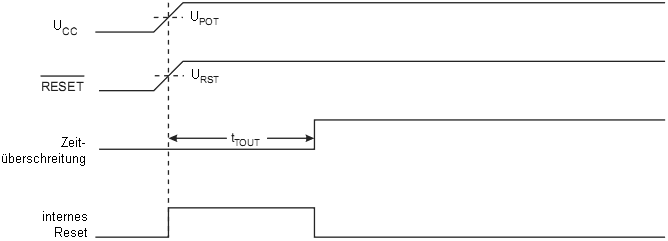

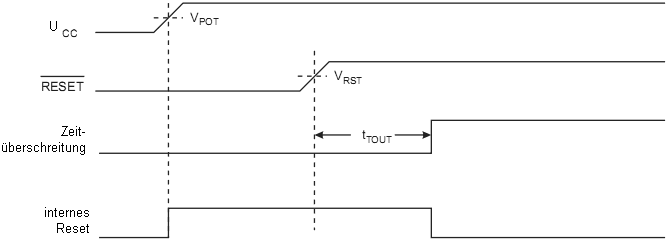

Bild 11-3: Mikrocontroller-Hochlauf, RESET extern verlängert

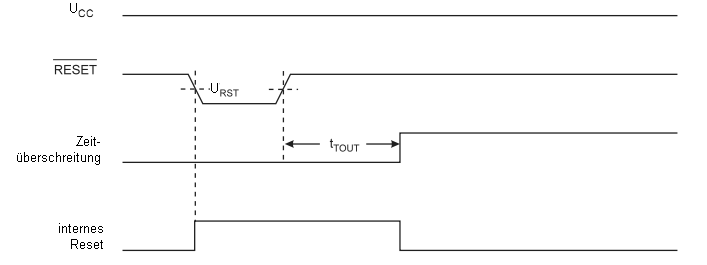

11.4 Externer Reset

Ein externer Reset wird durch einen Low-Pegel am RESET-Pin ausgelöst.

Reset-Pulse länger als die bei System- und Reset-Kennwerte angegebenen

lösen einen Reset aus, auch dann, wenn keine Takte laufen.

Kürzere Pulse führen nicht garantiert zu einem Reset.

Wenn das Reset-Signal am Eingang bei seiner positiven Flanke

die Reset-Schwellwertspannung URST erreicht,

wird der Verzögerungszeitgeber gestartet, so dass der Controller nach der Zeit

tTOUT die Arbeit beginnt.

Der externe Reset kann durch Programmieren der RSTDISBL-Fuse deaktiviert werden,

siehe Tabelle 28-7.

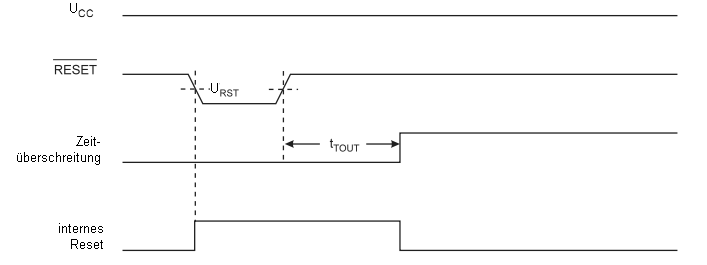

Bild 11-4: Externer Reset

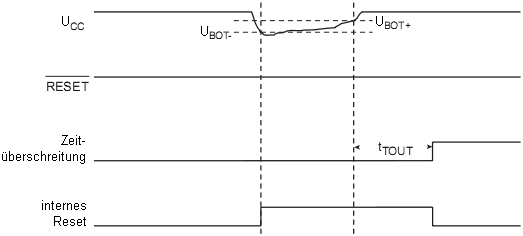

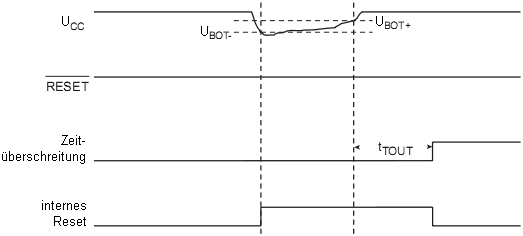

11.5 Unterspannungs-Reset

Der Schaltkreis hat einen Unterspannungsdetektor eingebaut,

die den Pegel der Versorgungsspannung überwacht, indem diese mit einem festen Triggerpegel verglichen wird.

Der Triggerpegel kann durch die BODLEVEL-Fuses festgelegt werden.

Der Triggerpegel hat eine Hysterese, um eine störspitzenfreie Spannungsüberwachung zu gewährleisten.

Die Hysterese der Triggerpegel kann interpretiert werden als

UBOT+ = UBOT + UHYST/2 und UBOT– = UBOT – UHYST/2.

Wenn BODLEVEL programmiert ist und UCC unter den Triggerpegel (UBOT– im Bild 11-5),

wird ein Unterspannungs-Reset ausgelöst.

Wenn UCC über den Triggerpegel steigt (UBOT+ im Bild 11-5),

startet der Verzögerungszähler und danach der Mikrocontroller nach Ablauf von tTOUT.

Der Unterspannungsdetektor kann nur einen Spannungsabfall unter dem Triggerpegel detektieren,

wenn dieser länger als tBOD vorliegt.

Die Zeit ist bei System- und Reset-Kennwerte angegeben.

Bild 11-5: Unterspannungs-Detektor-Reset

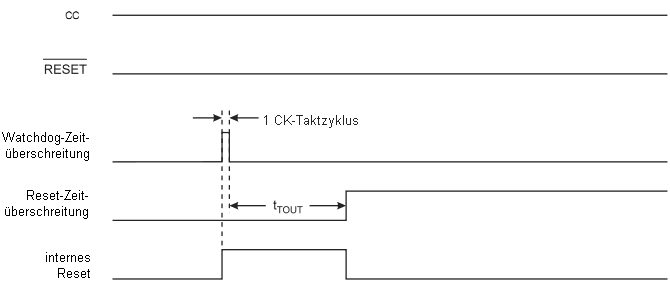

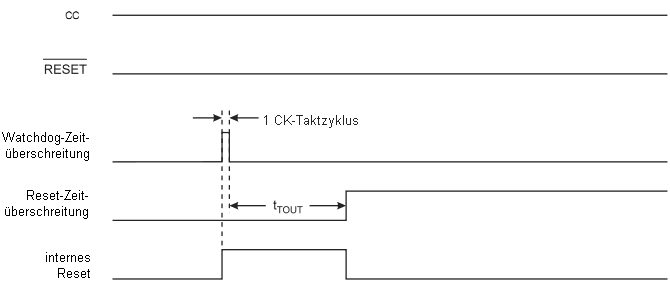

11.6 Watchdog-Reset

Wenn der Watchdog-Zeitgeber überläuft, wird ein Reset-Impuls von der Dauer eines Taktes erzeugt.

Mit der fallenden Flanke dieses Impulses wird der Verzögerungszähler gestartet, der die Verzögerungszeit tTOUT erzeugt.

Weiteres zu Watchdog steht weiter hinten.

Bild 11-6: Watchdog-Reset

11.7 Interne Spannungsreferenz

Der Controller hat eine interne Bandgap-Referenzspannungsquelle.

Diese Referenzspannung wird für die Unterspannungs-Erkennung verwendet

und kann auch als Eingang für den Analogvergleicher oder den Analog/Digital-Wandler benutzt werden.

11.7.1 Freigabesignale und Hochlaufzeiten

Die Referenzspannungsquelle hat eine Hochlaufzeit,

die Einfluss darauf hat, bis sie benutzt werden kann.

Die Zeit ist bei System- und Reset-Kennwerte angegeben.

Um Strom zu sparen ist die Referenzspannungsquelle nicht immer aktiv.

Sie wird nur in folgenden Fällen aktiviert:

- Wenn BOD durch Programmierung der BODLEVEL[2:0]-Fuses freigegeben ist

- Wenn die Referenzspannungsquelle mit dem Analogvergleicher verbunden ist (durch Setzen von ACBG im ACSR)

- Wenn der ADU freigegeben ist

Das heißt, wenn BOD nicht freigegeben ist

und das ACGB-Bit gesetzt wird oder des ADC aktiviert wird,

muss der Anwender also die Start-up Zeit abwarten,

bis der Analog Comparator oder der Analog-Digitalwandler genutzt werden kann.

Um im Leistung-weg-Energiesparmodus Strom zu sparen, muss der Anwender vermeiden,

dass einer der drei oben genannten Fälle auftritt,

indem er die Referenzspannungsquelle ausschaltet.

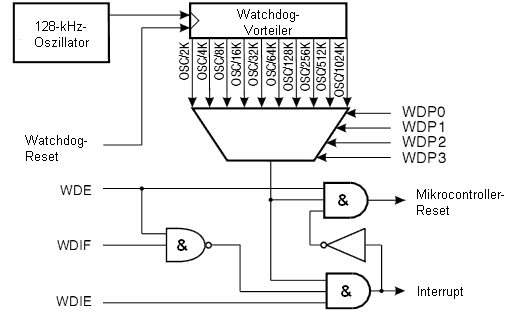

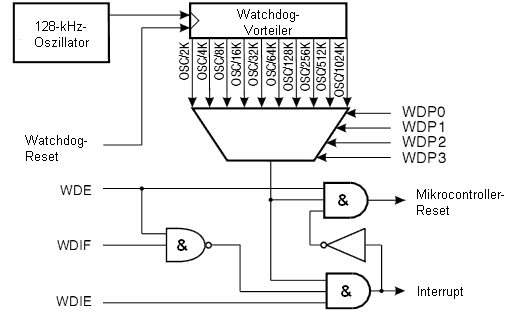

11.8 Watchdog-Zeitgeber

11.8.1 Features

- Getaktet von einem separaten On-Chip-Oszillator

- 3 Betriebsarten

- Interrupt

- Reset

- Interrupt und Reset

- Auswählbare Zeitüberschreitung von 16 ms bis 8 s

- Möglichkeit des Zwangs zum Watchdog mittels WDTON-Fuse für fehlersicheren Betrieb

11.8.2 Übersicht

Der Chip hat einen erweiterten Watchdog-Zeitgeber (WDT).

Er wird von einem separaten 128-kHz-Oszillator getaktet.

Der Watchdog kann einen Interrupt oder ein Reset auslösen,

wenn eine Zeitüberschreitung erreicht wird.

Im Normalfall wird der Befehl WDR (Watchdog Reset) benutzt,

um den Zeitgeber neu zu starten, bevor es zur Zeitüberschreitung kommt.

Andernfalls wird ein Interrupt oder Reset ausgelöst.

Bild 11-7: Watchdog-Timer

Im Interruptbetrieb gibt der WDT einen Interrupt, wenn der Zeitgeber abläuft.

Der Interrupt kann genutzt werden, um den Chip vom Schlafmodus aufzuwecken,

oder als allgemeiner Zeitgeber.

Ein Beispiel ist es, die Dauer einer bestimmten Rechenoperation zu begrenzen,

indem ein Interrupt auftaucht, wenn die Operation länger als erwartet dauert.

Im Reset-Betrieb gibt der WDT einen Reset, wenn der Zeitgeber abläuft.

Dies wird typischerweise eingesetzt, um Aufhänger durch Endlos-Kode abzubrechen.

Die dritte Betriebsart, Interrupt- und Reset-Betrieb, kombiniert beides

indem zuerst ein Interrupt ausgelöst wird und dann zum Reset-Betrieb gewechselt wird.

Diese Betriebsart ermöglicht beispielsweise ein geordnetes Herunterfahren

unter Speichern von kritischen Parametern, bevor es zum Reset kommt.

Die WDTON-Fuse (Watchdog immer an), falls programmiert, zwingt den Watchdog

in den Reset-Modus. Nur das Timeout kann noch eingestellt werden.

In diesem Fall ist das Bits WDE stets 1 und WDIE stets 0.

Für erhöhte Programmsicherheit müssen Änderungen am Watchdog durch eine

zeitbegrenzte Sequenz ausgeführt werden.

Die Sequenz zum Löschen von WDE oder dem Ändern der Zeiten ist wie folgt:

- In einem Befehl muss gleichzeitig eine 1 in die Bits WDCE und WDE geschrieben werden.

Die 1 muss — unabhängig vom vorherigen Zustand von WDE — in WDE geschrieben werden.

- Innerhalb der nächsten vier Taktzyklen muss die 0 in das WDE-Bit

oder die neuen Vorteiler-Bits WDP[3:0] geschrieben werden.

Der folgende Beispielkode zeigt eine Assembler- und eine C-Funktion,

um den Watchdog-Zeitgeber abzuschalten.

Die Beispiele verlassen sich darauf, dass Interrupts abgeschaltet sind

oder nicht auftreten.

Falsch! Interrupts werden zu Fuß gesperrt und wieder freigegeben.

Beispiel in Assembler (1)

WDT_off:

cli ; Interrupts global sperren

wdr ; Watchdog rücksetzen

in r16,MCUSR ; WDRF in MCUSR löschen

andi r16,~(1<<WDRF)

out MCUSR, r16

; Schreibe 1-Bits nach WDCE und WDE

; Alten Vorteiler behalten, um unerwartete Zeitüberschreitung zu vermeiden

lds r16,WDTCSR

ori r16,(1<<WDCE)|(1<<WDE)

sts WDTCSR, r16

ldi r16,0

sts WDTCSR, r16 ; Watchdog ausschalten (nach 3 Takten)

sei ; Interrupts global freigeben

ret

Beispiel in C (1)

void WDT_off(void) {

__disable_interrupt();

__watchdog_reset();

MCUSR &= ~(1<<WDRF); /* WDRF in MCUSR löschen */

/* Schreibe 1-Bits nach WDCE und WDE */

/* Alten Vorteiler behalten, um unerwartete Zeitüberschreitung zu vermeiden */

WDTCSR |= (1<<WDCE) | (1<<WDE);

WDTCSR = 0x00; /* Watchdog ausschalten */

__enable_interrupt();

}

| |

|---|

| |

|---|

Hinweis: Ist der Watchdog unerwartet freigegeben,

etwa durch einen unkontrollierten Kode-Ablauf oder bei Unterspannung,

gibt es einen Reset, und der Watchdog bleibt scharf.

Wenn Kode den Watchdog nicht behandelt, kann das zu einer endlosen

Reset-Schleife führen.

Um diese Situation zu vermeiden, sollte die Anwendungssoftware

stets die Bits WDRF und WDE in der Initialisierungsroutine löschen,

sogar wenn der Watchdog gar nicht benutzt wird.

Der folgende Beispielkode zeigt eine Assembler- und eine C-Funktion,

um den Zeitüberschreitungswert (Vorteiler) des Watchdogs zu ändern.

Hinweis: Der Watchdog sollte unmittelbar vor dem Ändern der Vorteiler-Bits mittels WDR-Befehl

beruhigt werden, da ansonsten beim Verkürzen der Zeit eine Zeitüberschreitung auftreten könnte.

11.9 Register-Beschreibung

11.9.1 MCUSR — Mikrocontroller-Status

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x54) | - | - | - | - | WDRF | BORF | EXTRF | PORF | MCUCSR

|

|---|

| Zugriff | R | R | R | R | R/W | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | Siehe Bit-Beschreibung

|

- Bit 7:4 — Res: Reservierte Bits

Diese Bits sind reserviert und werden immer als 0 gelesen.

- Bit 3 — WDRF: Watchdog-Reset-Flag

Dieses Bit wird gesetzt „1“, wenn ein Watchdog-Reset auftrat.

Es wird durch ein Power-on-Reset gelöscht oder wenn es mit einer logischen „0“ beschrieben wird.

- Bit 2 — BORF: Unterspannungs-Reset-Flag

Dieses Bit wird gesetzt „1“, wenn ein Unterspannungs-Reset auftrat.

Es wird durch eine Power-on-Reset gelöscht oder wenn es mit einer logischen „0“ beschrieben wird.

- Bit 1 — EXTRF: Externer-Reset-Flag

Dieses Bit wird gesetzt „1“, wenn ein externer Reset auftrat.

Es wird durch eine Power-on-Reset gelöscht oder wenn es mit einer logischen „0“ beschrieben wird.

- Bit 0 — PORF: Power-on-Reset-Flag

Dieses Bit wird gesetzt „1“, wenn ein Power-on-Reset auftrat.

(Die drei anderen Bits sind dann konsequenterweise Null.)

Diese Bit kann nur gelöscht werden, indem es mit einer logischen „0“ beschrieben wird.

Die Reset-Flags können ausgewertet werden, um die Ursache eines Resets festzustellen.

Dabei sollte das MCUSR so früh wie möglich im Programm ausgewertet und anschließend gelöscht werden.

11.9.2 WDTCR — Watchdog-Zeitgeber-Kontrolle

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x60) | WDIF | WDIE | WDP3 | WDCE | WDE | WDP2 | WDP1 | WDP0 | WDTCR

|

|---|

| Zugriff | R/W! | R/W↓ | R/W | R/W | R/W | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | X | 0 | 0 | 0

|

- Bit 7 — WDIF: Watchdog-Interrupt anhängig

Dieses Bit ist gesetzt, wenn der Watchdog-Zeitgeber überläuft

und der Watchdog auf Interrupt konfiguriert ist.

WDIF wird durch die Hardware gelöscht, wenn der Watchdog-Interrupt zur Ausführung kommt.

Alternativ kann WDIF durch Schreiben einer Eins gelöscht werden.

Wenn das I-Bit in SREG und WDIE gesetzt sind, wird der Watchdog-Interrupt ausgeführt.

- Bit 6 — WDIE: Watchdog-Interrupt-Freigabe

Wenn dieses Bit und das I-Bit im Statusregister gesetzt ist,

ist der Watchdog-Interrupt freigegeben.

Wird WDE gemeinsam mit dem Setzen dieses Bits gelöscht,

befindet sich der Watchdog im Interrupt-Betrieb,

und der zugehörige Interruptvektor wird bei Zeitgeber-Überlauf ausgelöst.

Ist sowohl WDIE als auch WDE gesetzt, befindet sich der Watchdog

im Interrupt- und im Reset-Betrieb.

Die erste Zeitüberschreitung setzt WDIF.

Die Ausführung des Interruptsvektors löscht sowohl WDIE als auch WDIF durch die Hardware,

der Watchdog ist nunmehr im Reset-Betrieb.

Dies ist sinnvoll wenn Watchdog-Sicherheit gemeinsam mit Interrupts verwendet werden soll.

Um im Interrupt- und Reset-Betrieb zu bleiben, muss nach Interruptroutine WDIE gesetzt werden.

Das sollte jedoch nicht innerhalb der Interruptroutine geschehen,

da dies die Sicherheitsfunktion des Watchdogs kompromittiert.

Kommt die Interruptroutine nicht zur Ausführung bis zur zweiten Zeitüberschreitung,

wird ein Reset ausgelöst.

Tabelle 11-1: Watchdog-Zeitgeber-Konfiguration

WDTON(1)| WDE | WDIE | Betriebsart | Aktion bei Zeitüberschreitung

| | 1 | 0 | 0 | inaktiv | keine

| | 1 | 0 | 1 | Interrupt-Betrieb | Interrupt

| | 1 | 1 | 0 | Reset-Betrieb | Reset

| | 1 | 1 | 1 | Interrupt- und Reset-Betrieb | Interrupt, dabei Wechsel zu Reset-Betrieb

| | 0 | x | x | Reset-Betrieb | Reset

| |

|---|

- Hinweis:

- WDTON-Fuse = „0“ bedeutet programmiert und „1“ bedeutet unprogrammiert.

- Bit 4 — WDCE: Freigabe des Watchdog-Änderns

Dieses Bit muss gesetzt sein, wenn das WDE-Bit gelöscht oder Vorteiler-Bits geändert werden sollen.

Wenn das WDCE-Bit gesetzt wurde, wird es durch die Hardware nach vier Taktzyklen wieder gelöscht.

- Bit 3 — WDE: Watchdog-Freigabe

WDE wird durch WDRF im MCUSR übergangen.

Das bedeutet, WDE ist immer gesetzt wenn WDRF gesetzt ist.

Um WDE zu löschen, muss erst WDRF gelöscht werden.

Dieses Feature sichert mehrere Resets bei verursachten Watchdog-Zeitüberschreitungen,

und ein sicheren Hochlauf nach dem Problem.

- Bit 5,[2:0] — WDP[3:0]: Watchdog-Zeitgeber-Vorteiler

Diese Bits definieren den Vorteiler des Watchdog-Zeitgebers, wenn dieser freigegeben ist.

Die Einstellmöglichkeiten und die dazugehörigen Zeitüberschreitungs-Zeiten

sind in nachfolgender Tabelle dargestellt.

Tabelle 11-2: Watchdog-Zeitgeber-Vorteiler-Auswahl

| WDP3 | WDP2 | WDP1 | WDP0 | WDT-Oszillator-Zyklen | Typische Zeitüberschreitung bei UCC = 5,0 V

|

|---|

| 0 | 0 | 0 | 0 | 2K (2048) | 16 ms

|

| 0 | 0 | 0 | 1 | 4K (4096) | 32 ms

|

| 0 | 0 | 1 | 0 | 8K (8192) | 64 ms

|

| 0 | 0 | 1 | 1 | 16K (16384) | 0,125 s

|

| 0 | 1 | 0 | 0 | 32K (32768) | 0,25 s

|

| 0 | 1 | 0 | 1 | 64K (65536) | 0,5 s

|

| 0 | 1 | 1 | 0 | 128K (131072) | 1 s

|

| 0 | 1 | 1 | 1 | 256K (262144) | 2 s

|

| 1 | 0 | 0 | 0 | 512K (524288) | 4 s

|

| 1 | 0 | 0 | 1 | 1024K (1048576) | 8 s

|

| 1 | 0 | 1 | 0 | reserviert

|

| 1 | 0 | 1 | 1

|

| 1 | 1 | 0 | 0

|

| 1 | 1 | 0 | 1

|

| 1 | 1 | 1 | 0

|

| 1 | 1 | 1 | 1

|