20. USART

20.1 Features

- Gegensprechen, d.h. unabhängiges Senden und Empfangen

- Asynchroner und synchroner Betrieb

- Synchroner Betrieb als Master oder Slave

- Baudraten-Generator mit hoher Auflösung

- Unterstützt serielle Rahmen mit 5, 6, 7, 8, oder 9 Datenbits und 1 oder 2 Stoppbits

- Erzeugen von geraden und ungeraden Paritätsbits und Paritätsprüfung durch die Hardware

- Datenüberlauf-Erkennung

- Rahmenfehler-Erkennung

- Störungsfilter mit Erkennung falscher Startbits und digitaler Tiefpassfilter

- Drei separate Interrupts bei Senden fertig, Senderegister leer und Empfangsdaten vorhanden

- Multiprozessor-Kommunikationsmodus

- Asynchroner Modus mit doppelter Geschwindigkeit

20.2 Übersicht

Der universelle synchrone und asynchrone serielle Empfänger und Sender (USART)

ist ein hochflexibler serieller Baustein.

Der USART0 kann auch als SPI-Master verwendet werden,

siehe gesondertes Kapitel.

Das Bit PRUSART0 im Leistungsreduktionsregister PRR muss gelöscht sein,

um den USART zu nutzen.

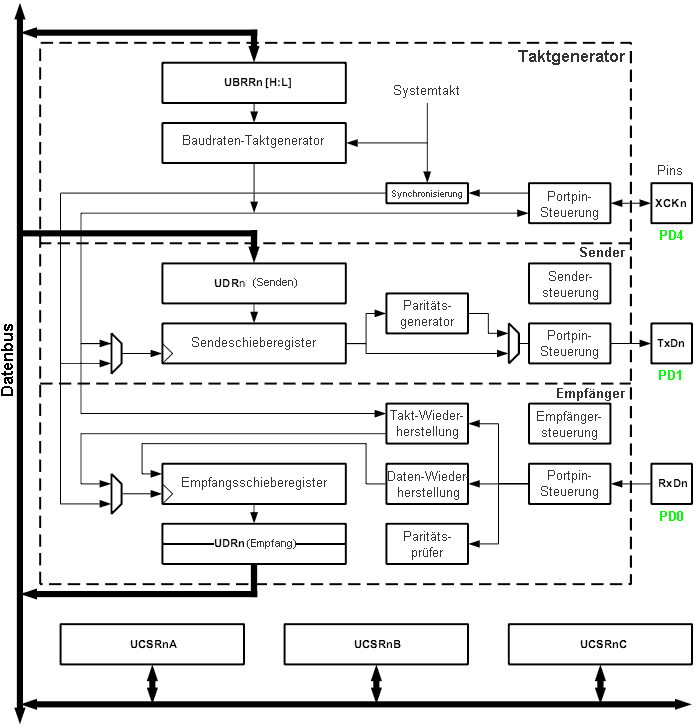

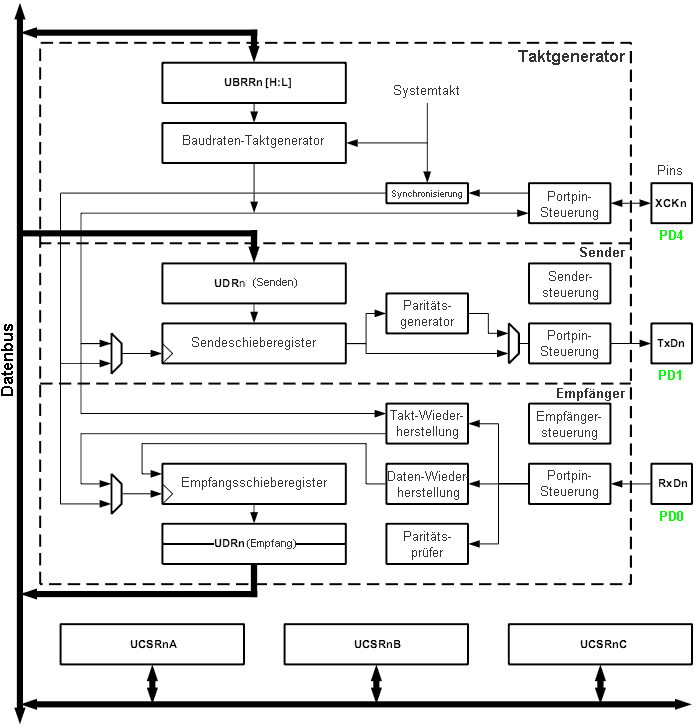

Das Bild 20-1 zeigt das vereinfachte Blockschaltbild des USART.

I/O-Register und I/O-Pins, auf die die CPU zugreifen kann, sind fett dargestellt.

Die gestrichelten Kästen im Blockschaltbild zeigen die drei

separaten Hauptbestandteile des USART: Taktgenerator, Sendeeinheit und Empfangseinheit.

Die Kontrollregister werden von allen drei Teilen genutzt.

Die Logik des Taktgenerators besteht aus einer Synchronisationslogik,

für den externen Takteingang, der im synchronen Slavemodus verwendet wird,

und dem Baudratengenerator.

Das XCK-Pin (Transfer-Takt) wird nur im synchronen Übertragungsmodus verwendet.

Der Sender besteht aus einem einfachen Schreibpuffer,

dem seriellen Schieberegister, dem Paritätsgenerator

und einer Kontrolllogik zum Handhaben der verschiedenen Rahmenformate.

Der Schreibpuffer erlaubt einen kontinuierlichen Datentransfer

ohne Verzögerung zwischen den Datenrahmen.

Der Empfänger ist der komplexeste Teil des USART

mit seinen Takt- und Datenwiederherstellungs-Einheiten.

Die Wiederherstellungseinheiten werden beim asynchronen Datenempfang benutzt.

Zusätzlich zu den Wiederherstellungseinheiten besteht der Empfänger

aus einem Paritätsprüfer, der Kontrolllogik,

einem Schieberegister und einem zweifachen Empfangspuffer (UDR).

Der Empfänger unterstützt die gleichen Rahmenformate

wie der Sender und kann Rahmenfehler, Datenüberläufe und Paritätsfehler erkennen.

Bild 20-1: Blockschaltbild USART

- Hinweis:

- Siehe Bild 1-1 und Tabelle 14-9

für die Platzierung der Anschlüsse

20.3 Takterzeugung

Die Takterzeugungslogik generiert den Basistakt für den Sender und Empfänger.

Der USART unterstützt vier Taktmodi: den normalen asynchronen Modus,

den asynchronen Modus mit doppelter Geschwindigkeit,

den synchronen Mastermodus und den synchronen Slavemodus.

Das UMSELn-Bit im USART-Steuerregister C (UCSRC)

wählt zwischen dem asynchronen und dem synchronen Modus aus.

Die doppelte Geschwindigkeit (nur asynchron) kann mit dem U2X-Bit im UCSRnA-Register ausgewählt werden.

Wenn ein synchroner Modus (UMSEL = 1) benutzt wird,

kontrolliert das Datenrichtungsregister für das XCK-Pin (DDR_XCK)

ob die Taktquelle intern (Mastermodus) oder extern (Slavemodus) ist.

Das XCK-Pin ist nur in den synchronen Modi aktiv.

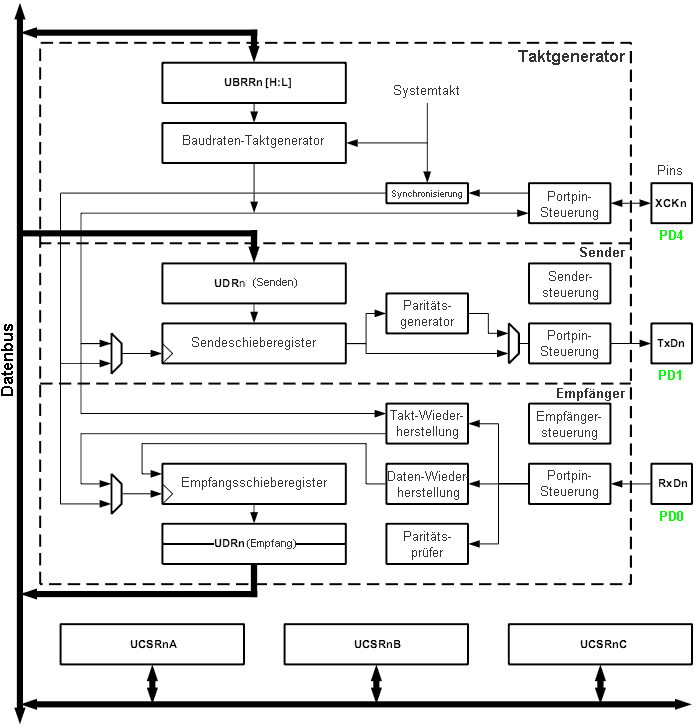

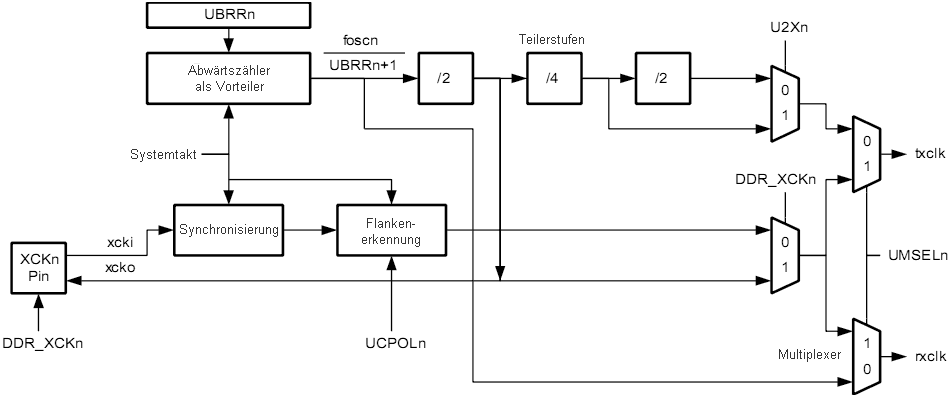

Das nachfolgende Bild zeigt das Blockdiagramm der Takterzeugungslogik.

Bild 20-2: Blockschaltbild Takterzeugung

Beschreibung der Signale:

| txclk | Sendetakt (internes Signal)

|

|---|

| rxclk | Empfänger-Basistakt (internes Signal)

|

|---|

| xcki | Eingang vom XCK-Pin (internes Signal), verwendet im synchronen Slavemodus

|

|---|

| xcko | Taktausgang zum XCK-Pin (internes Signal), verwendet im synchronen Mastermodus

|

|---|

| fosc | Systemtaktfrequenz, typischerweise Quarzfrequenz

|

|---|

20.3.1 Interner Takt

Die interne Takterzeugung wird für die asynchronen und den synchronen Mastermodus verwendet.

Die Beschreibung bezieht sich auf das Bild zuvor.

Das USART-Baudratenregister (UBRR) und der Rückwärtszähler arbeiten

zusammen als programmierbarer Vorteiler bzw. als Baudratengenerator.

Der Rückwärtszähler, der mit dem Systemtakt (fosc) getaktet wird,

wird jedes Mal wenn der Zähler bei Null angelangt ist oder das UBRR beschrieben wird,

mit dem Wert aus dem UBRR geladen.

Ein Takt wird jedes Mal erzeugt, wenn der Zähler bei Null angelangt.

Dieser Takt ist der Baudratengenerator-Ausgangstakt (= fosc/(UBRR+1)).

Der Sender teilt den Baudraten-generator-Ausgangstakt durch 2, 8 oder 16, abhängig vom Modus.

Der Baudraten-generatorausgang wird direkt vom Empfängertakt und den Datenwiederherstellungseinheiten verwendet.

Die Wiederherstellungseinheiten verwenden eine Takterzeugung

die 2, 8, oder 16 Zustände benutzt, unabhängig von dem Modus,

der durch die UMSEL, U2X und DDR_XCK-Bits eingestellt ist.

Tabelle 20-1: Baudraten ermitteln

| Betriebsart | Gleichung

Baudrate aus UBRRn | Gleichung

UBRRn aus Baudrate

|

|---|

Asynchron, normal

U2Xn = 0

|

|

|

Asynchron, doppelt schnell

U2Xn = 1

|

|

|

| Synchron, Master

|

|

|

- Hinweis:

- Die Baudrate ist die Symbolrate in baud

Einige Beispiele für UBRR-Werte und Frequenzen des Systemtaktes

sind in Tabellen unten abgebildet.

20.3.2 Doppelte Geschwindigkeit

Die Datentransferrate kann verdoppelt werden, wenn das U2X-Bit im UCSRA gesetzt wird.

Das Setzen dieses Bits wirkt sich nur im asynchronen Modus aus.

Wenn ein synchroner Modus verwendet wird, sollte das Bit gelöscht bleiben.

Das Setzen des Bits reduziert den Divisor des Baudratenteilers von 16 auf 8,

was einer Verdopplung der Transferrate für die asynchrone Kommunikation entspricht.

Man beachte, dass der Empfänger in diesem Fall nur die halbe Anzahl von Abtastungen (8 statt 16)

bei der Datenerfassung und Taktwiederherstellung verwendet wird

und daher genauere Baudrateneinstellungen und Systemtakte erforderlich sind,

wenn dieser Modus verwendet wird.

Für den Sender gibt es keine Beeinträchtigungen.

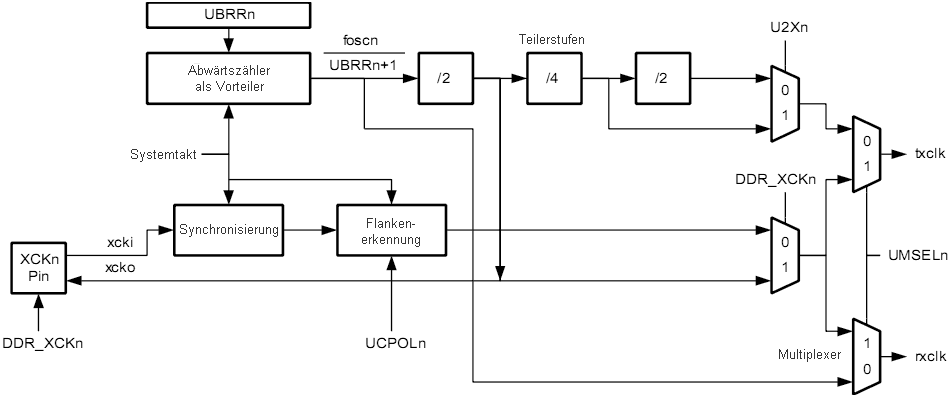

20.3.3 Externer Takt

Die externe Taktung wird im synchronen Slavemodus verwendet.

Die Beschreibung bezieht sich auf das Abbild zuvor.

Der externe Takt vom XCK-Pin wird durch ein Synchronisationsregister

abgetastet.

Der Ausgang des Synchronisationsregisters muss durch einen Flankenerkenner

bevor er für den Sender und Empfänger verwendet werden kann.

Dieser Vorgang leitet eine Verzögerung von zwei CPU-Takten ein,

daher ist die maximale externe Taktfrequenz von XCK begrenzt auf:

Man beachte, dass fosc von der Stabilität der Quelle des Systemtaktes abhängt.

Es wird daher empfohlen, einigen Spielraum einzukalkulieren,

um den möglichen Datenverlust durch Veränderungen der Frequenz zu vermeiden.

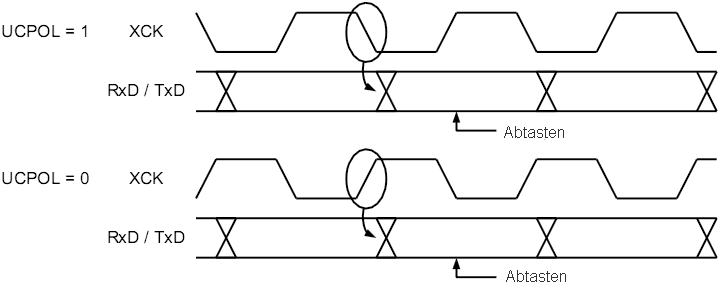

20.3.4 Synchrone Taktung

Wenn ein synchroner Modus ausgewählt wurde (USEL=1),

dann wird der XCK-Pin entweder als Takteingang (Slave) oder als Taktausgang verwendet.

Der Zusammenhang zwischen den Taktflanken,

den Datenabtasten oder Datenänderungen ist der gleiche.

Das grundsätzliche Prinzip ist,

dass der Dateneingang (RxD) mit der gegenüberliegenden Flanke des XCK-Taktes

abgetastet wird als bei der Flanke, zu dem der Datenausgang (TxD) wechselt.

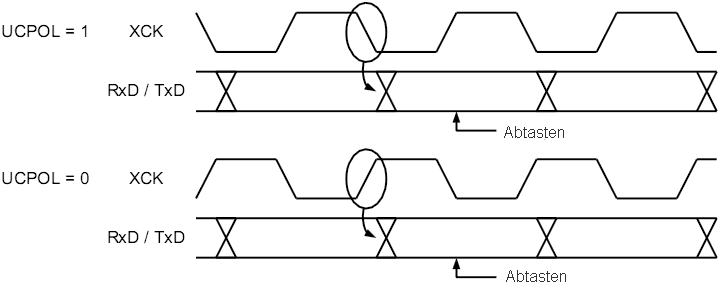

Bild 20-3: Zeitdiagramm synchroner Takt

Das UCPOL-Bit im UCRSC-Register legt fest,

welche XCK-Taktflanke für das Abtasten der Daten verwendet wird und welche für den Datenwechsel.

Wie in obiger Abbildung zu sehen werden die Daten bei UCPOL=0

mit der steigenden Flanke von XCK gewechselt und mit der fallenden Flanke abgetastet.

Bei UCPOL = 1 werden die Daten mit der fallenden Flanke gewechselt

und mit der steigenden Flanke abgetastet.

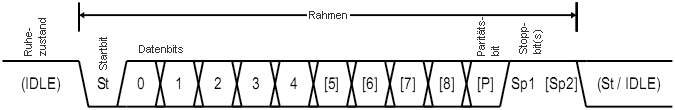

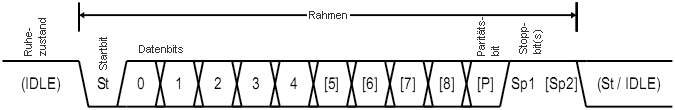

20.4. Rahmenformate

Ein serieller Rahmen ist definiert als ein Zeichen mit Daten mit

Synchronisationsbits (Start- und Stoppbits) und einem optionalen

Paritätsbit für die Fehlererkennung.

Die USART akzeptiert alle 30 Kombinationen aus dem Folgenden als gültige Rahmenformate:

- 1 Startbit

- 5, 6, 7, 8 oder 9 Datenbits

- kein, gerades oder ungerades Paritätsbit

- 1 oder 2 Stoppbits

Ein Rahmen beginnt mit dem Startbit, gefolgt von dem LSB-Datenbit.

Anschließend folgen die anderen bis zu insgesamt neun Datenbits, mit dem MSB endend.

Wenn freigegeben wird ein Paritätsbit nach den Datenbits eingefügt, bevor dann die Stoppbits folgen.

Wenn ein vollständiger Rahmen übertragen wurde kann direkt ein weiterer Rahmen folgen

oder die Kommunikationsverbindung kann in einen idle (High) Zustand gesetzt werden.

Das nachfolgende Bild zeigt die möglichen Rahmenformate, die Bits in Klammern sind optional.

Bild 20-4: Rahmenformate

| St | Startbit (immer Low)

|

|---|

| (n) | Datenbits (0 bis 8)

|

|---|

| P | Paritätsbit, gerade oder ungerade

|

| Sp | Stoppbit (immer High)

|

| IDLE | Keine Übertragung auf der Kommunikationsleitung (RxD oder TxD). Eine IDLE-Leitung muss immer High sein.

|

Das Rahmenformat, das die USART verwendet, wird durch die Bits UCSZ2 bis UCSZ0,

UPM1 bis UPM0 und das USBS-Bit in den Registern UCSRB und UCSRC eingestellt.

Der Empfänger und der Sender verwenden die gleichen Einstellungen.

Zu beachten ist, dass ein Verändern dieser Bits alle laufenden Übertragungen

des Senders und Empfängers unbrauchbar macht.

Die Bits UCSZ2 bis UCSZ0 legen die Anzahl der Datenbits im Rahmen fest.

Die Bits UPM1 bis UPM0 geben das Paritätsbit und dessen Art frei.

Die Auswahl zwischen einem oder zwei Stoppbits erfolgt mit dem Bit USBS.

Der Empfänger ignoriert ein zweites Stoppbit.

Ein Rahmenfehler wird daher nur in den Fällen erkannt,

in denen das erste Stoppbit Null ist.

20.4.1 Paritätsbit-Berechnung

Die Parität ist die Exklusiv-ODER-Verknüpfung aller Datenbits.

Bei ungerader Parität wird davon die Invertierung verwendet.

Die Beziehung zwischen Datenbits und Parität ist folgende:

| Peven | Parity bit using even parity

|

|---|

| Podd | Parity bit using odd parity

|

|---|

| dn | Data bit n of the character

|

|---|

Wenn benutzt liegt das Paritätsbit stets zwischen dem letzten Datenbit (MSB)

und dem ersten Stoppbit.

20.5 Initialisierung

Die USART muss initialisiert werden, bevor irgendeine Datenübertragung stattfinden kann.

Die Initialisierungssequenz besteht normalerweise aus

dem Einstellen des Baudratengenerators, dem Einstellen des Rahmenformates

und der Freigabe des Senders und Empfängers abhängig davon, welcher benötigt wird.

Bei interruptgetriebener USART-Arbeitsweise muss das globale Interruptflag

während der Initialisierung des USART gelöscht (und damit alle Interupts gesperrt) sein.

Bevor eine erneute Initialisierung mit Verändern der Baudrate

oder des Rahmenformates vorgenommen wird, muss man sich vergewissern,

dass keine Übertragung läuft, während die Register geändert werden.

Das TXC-Flag kann genutzt werden, um zu prüfen, ob der Sender

alle Übertragungen abgeschlossen hat und das RXD-Flag kann verwendet werden,

um zu prüfen, ob keine ungelesenen Daten im Empfangspuffer liegen.

Man beachte, dass das TXC-Flag vor jeder Übertragung

(also bevor in das UDR geschrieben wird) gelöscht werden muss,

wenn es in diesem Sinne verwendet werden soll.

Das folgende einfache Beispiel zur Initialisierung des USART

ist in Assembler und C identisch.

Die Beispiele setzen voraus, dass mit einem Polling

und nicht mit Interrupts gearbeitet wird

und ein festes Rahmenformat verwendet wird.

Die Baudrate wird als Parameter der Funktion übergeben.

Im Assemblercode wird angenommen, dass der Baudraten-Parameter

in den Registern R25:R24 abgelegt ist.

Wenn die Funktion in das UCSRC-Register schreibt,

muss das URSEL-Bit (MSB) gesetzt sein,

da sich UBRRH und UCSRC eine I/O-Speicherzelle teilen.

Kodebeispiel in Assembler(1)

USART_Init:

; Baudrate setzen

sts UBRR0H,r25

sts UBRR0L,r24

; Sender und Empfänger freigeben

ldi r24,1<<RXEN0 | 1<<TXEN0

sts UCSR0B,r24

; Rahmenformat setzen: 8 Datenbits, 2 Stoppbits, keine Parität

ldi r24,1<<USBS0 | 3<<UCSZ00

sts UCSR0C,r24

ret

Kodebeispiel in C(1)

#define F_CPU 1843200 // Taktfrequenz, kann auch vom Makefile kommen

#define BAUD 9600

void main(void) {

...

/* Dieser Ausdruck rundet korrekt und generiert eine Konstante */

USART_Init((unsigned)(F_CPU/16.0/BAUD-0.5));

...

}

void USART_Init(unsigned ubrr) {

/* Baudrate setzen */

UBRR0 = ubrr;

/* Sender und Empfänger freigeben */

UCSR0B = (1<<RXEN0)|(1<<TXEN0);

/* Rahmenformat setzen: 8 Datenbits, 2 Stoppbits, keine Parität */

UCSR0C = (1<<USBS0)|(3<<UCSZ00);

}

| |

|---|

| |

|---|

- Hinweis:

- Siehe „Über Kode-Beispiele“

Weiter fortgeschrittene Initialisierungsroutinen können so ausgelegt sein,

dass auch das Rahmenformat als Parameter übergeben wird

und die Interrupts automatisch gesperrt und freigegeben werden usw.

Viele Applikationen verwenden allerdings feste Einstellungen

für die Baudrate und die Kontrollregister,

so das für diese Arten von Applikation das Beispiel

direkt in das Programm übernommen werden kann.

20.6 Daten senden

Der Sender der USART wird durch Setzen des Bits Transmit Enable (TXEN) im UCSRB-Register freigegeben.

Wenn der Sender freigegeben ist, wird die normale Portfunktion des TxD-Pins durch die USART überschrieben

und hat die Funktion als Ausgang des seriellen Senders.

Die Baudrate, der Operationsmodus und das Rahmenformat müssen zunächst eingestellt werden,

bevor eine Übertragung stattfinden kann.

Wenn die synchrone Arbeitsweise verwendet wird,

wird der Takt am XCK Pin als Sendetakt verwendet.

20.6.1 5-8 Datenbits

Eine Übertragung wird dadurch gestartet, indem der Sendepuffer mit den zu sendenden Daten geladen wird.

Die CPU lädt den Sendebuffer, indem UDR beschrieben wird.

Die gepufferten Daten im Sendepuffer werden in das Schieberegister transportiert,

wenn das Schieberegister zum Senden eines neuen Rahmens bereit ist.

Das Schieberegister wird geladen, wenn es im Idle-Zustand ist

(d.h. keine laufende Übertragung)

oder unmittelbar nachdem das letzte Stoppbit vom vorherigen Rahmen übertragen wurde.

Wenn das Schieberegister mit neuen Daten geladen wird,

wird ein kompletter Rahmen mit einer Rate, die durch das Baudratenregister,

das U2X-Bit oder den XCK-Takt abhängig vom Betriebsmodus vorgegeben wird, übertragen.

Das folgende Programmbeispiel zeigt eine einfache USART-Sendefunktion,

die auf dem Pollen des Flags „Datenregister leer“ UDRE basiert.

Wenn Rahmen mit weniger als 8 Datenbits verwendet werden,

werden die MSB, die ins UDR geschrieben wurden, ignoriert.

Die USART muss initialisiert werden, bevor die Funktion genutzt werden kann.

Im Assemblercode wird vorausgesetzt, dass die zu sendenden Daten im Register R24 stehen.

Die Funktion wartet, bis der Sendepuffer leer ist, indem es das UDRE-Flag abfragt,

bevor er mit den neuen zu sendenden Daten geladen wird.

Wenn der entsprechende Interrupt verwendet wird,

schreibt die Interruptroutine die Daten in den Sendepuffer.

20.6.2 9 Datenbits

Wenn 9-Bit Zeichen verwendet werden (UCSZ = 7),

wird das neunte Bit in das TXB8-Bit im UCSRB Register geschrieben,

bevor das Low-Byte des Zeichens in UDR geschrieben wird.

Das folgende Programmbeispiel zeigt die Funktion für das Senden eine 9-Bit-Zeichens.

Im Assemblerbeispiel wird vorausgesetzt,

dass die zu sendenden Daten in den Registern R25 und R24 stehen.

- Hinweise:

- Die Sendefunktion ist allgemein gehalten.

Sie kann dahingehend optimiert werden, dass der Inhalt des UCSR0B-Registers statisch ist.

Beispielsweise könnte das TXB8-Bit einmalig in der Initialisierung geladen werden.

- Siehe „Über Kode-Beispiele“

Das neunte Bit kann dazu verwendet werden,

um ein Adressframe bei der Multiprozessor-Kommunikation

zu kennzeichnen oder für andere Protokollaufgaben wie z.B. zur Synchronisation.

20.6.3 Sendeflags und Interrupts

Der USART Sender hat zwei Flags, die folgende Stati kennzeichnen:

USART Data Register Empty (UDRE) und Transmit Complete (TXC).

Beide Flags können zum Erzeugen eines Interrupts verwendet werden.

Das Data Register Empty Flag (UDRE) signalisiert, dass der Sendebuffer zur Aufnahmen neuer Daten bereit ist.

Dieses Bit wird gesetzt, wenn der Sendebuffer leer ist und wird gelöscht,

wenn der Sendebuffer zu sendende Daten enthält,

die noch nicht in das Schieberegister übernommen wurden.

Um die Kompatibilität zu zukünftigen Bausteinen sicherzustellen,

sollte das Bit immer auf Null gesetzt werden,

wenn in das UCSRA Register geschrieben wird.

Wenn das Data Register Empty Interrupt Enable (UDRIE) Bit im UCSRB Register auf 1 gesetzt wird,

wird der entsprechende Interrupt so lange ausgeführt wie das UDRE Flag gesetzt ist,

vorausgesetzt, dass die Interrupts global freigegeben sind.

Das UDRE Falg wird gelöscht, indem in das UDR geschrieben wird.

Wenn eine Interruptgesteuerte Datenübertragung verwendet wird,

muss die Interrupt Routine entweder ein neues Datum in das UDR schreiben

um das UDRE Flag zu löschen oder den Data Register Empty Interrupt sperren,

da sonst ein neuer Interrupt ausgelöst wird, sobald die Interruptroutine beendet wurde.

Das Transmit Complete (TXC) Flag wird gesetzt, wenn ein vollständiger Frame

aus dem Schieberegister des Senders übertragen wurde und keine weiteren Daten im Sendebuffer vorhanden sind.

Das TXC Flag wird automatisch gelöscht, wenn der Transmit Complete Interrupt ausgeführt wird,

oder indem einen 1 in das Bit geschrieben wird.

Das TXC Bit ist hilfreich bei halb-duplex Schnittstellen (wie dem RS485 Standard),

bei denen die sendende Einheit in den Empfangsmodus gehen muss

um den Kommunikationsbus im Anschluss an eine erfolgte Übertragung freizugeben.

Wenn das Transmit Complete Interrupt Enable (TXCIE) Bit im UCSRB gesetzt ist,

wird der USART Transmit Complete Interrupt ausgeführt, sobald das TXC Flag gesetzt wird,

vorausgesetzt, die Interrupts sind global freigegeben.

Wenn der Interrupt verwendet wird, muss die Interruptroutine des TXC Falg nicht extra löschen,

da dies automatisch geschieht, wenn die Interruptroutine ausgeführt wird.

20.6.4 Paritätsgenerator

Der Parity Generator berechnet das Paritätsbit für die seriellen Framedaten.

Wenn das Paritybit freigegeben ist (UPM1 = 1),

dann fügt die Sender Kontrolllogik das Paritätsbit

zwischen dem letzten Datenbit und dem ersten StoppBit des Frames ein, der gesendet wird.

20.6.5 Deaktivierung des Senders

Das Sperren des Senders durch Setzen des TXEN auf Null,

wird nicht wirksam, bis eine laufende bzw. anstehende Übertragung abgeschlossen ist.

D.h. die Sperre wird erst wirksam, wenn das Schieberegister des Senders

und der Sendebuffer keine zu sendenden Daten mehr enthalten.

Wenn der Sender gesperrt ist, wird er den TxD Pin nicht mehr überlagern.

20.7 Daten empfangen

Der USART Empfänger wird freigegeben,

indem das Receive Enable (RXEN) Bit im UCSRB Register auf 1 gesetzt wird.

Wenn der Empfänger freigegeben ist,

wird die normale Funktion des RxD Pins durch die Funktion des USART Empfänger Eingangs überschrieben.

Die Baudrate, der Operationsmodus und das Rahmen Format muss eingestellt werden,

bevor der erste serielle Empfang stattfinden kann.

Wenn der synchrone Modus verwendet wird, wird der Takt vom XCK Pin als Übertragungstakt verwendet.

20.7.1 5-8 Datenbits

Der Empfänger startet einen Datenempfang, wenn er ein gültiges Startbit erkennt. Jedes Bit das darauf folgt, wird mit der Baudrate oder dem XCK Takt abgetastet und in das Empfangsschieberegister geschoben bis das erste Stoppbit des Frames empfangen wird. Das zweite Stoppbit wird vom Empfänger ignoriert. Wenn das erste Stoppbit empfangen wurde, d.h. ein komplettes serielles Frame liegt im Eingangsbuffer, wird der Inhalt des Schieberegisters in den Empfangsbuffer geschoben. Der Empfangsbuffer kann dann ausgelesen werden, indem die UDR I/O Speicherzelle gelesen wird.

Das folgende Programmbeispiel zeigt eine einfache USART Empfangsfunktion, die auf dem Pollen des Receive Complete (RXC) Flags basiert. Wenn Frames mit weniger als 8 Datenbits verwendet werden, werden die MSB, die aus dem UDR gelesen werden mit Null maskiert. Die USART muss initialisiert werden, bevor die Funktion genutzt werden kann.

Die Funktion wartet bis Daten im Empfangsbuffer vorliegen,

indem es permanent das RXC Flag abfragt, bevor es den Buffer ausliest.

20.7.2 9 Datenbits

Wenn 9-bit Zeichen verwendet werden (UCSZ = 7) muss das neunte Bit

aus dem RXB8 Bit im UCSRB Register gelesen werden bevor das Low-Byte aus dem UDR gelesen wird.

Diese Regel gilt auch für das FE, DOR und PE Status Flag.

Erst den Status von UCSRA lesen, dann die Daten vom UDR.

Das Lesen der UDR I/O Speicherzelle verändert den Status

des Empfangsbuffer FIFO und somit werden auch die TXB8, FE, DOR und PE Bits,

die im FIFO gespeichert sind, verändert.

Das folgende Programmbeispiel zeigt eine einfache USART Empfangsfunktion,

das die Statusbits und das 9-bit Zeichen handhabt.

Kodebeispiel in Assembler(1)

USART_Receive:

; Wait for data to be received

lds r16,UCSR0A

sbrs r16,RXC0

rjmp USART_Receive

; Get status and 9th bit, then data from buffer

lds r18,UCSR0A

lds r17,UCSR0B

lds r16,UDR0

; If error, return -1

andi r18,(1<<FE0)|(1<<DOR0)|(1<<UPE0)

breq USART_ReceiveNoError

ldi r17, HIGH(-1)

ldi r16, LOW(-1)

USART_ReceiveNoError:

; Filter the 9th bit, then return

lsr r17

andi r17,0x01

ret

Kodebeispiel in C(1)

unsigned int USART_Receive(void) {

unsigned char status,resh,resl;

/* Wait for data to be received */

while (!(UCSR0A & (1<<RXC0)));

/* Get status and 9th bit, then data from buffer */

status = UCSR0A;

resh = UCSR0B;

resl = UDR0;

/* If error, return -1 */

if (status & (1<<FEn)|(1<<DORn)|(1<<UPEn)) return -1;

/* Filter the 9th bit, then return */

resh = (resh >> 1) & 0x01;

return ((resh << 8) | resl);

}

| |

|---|

| |

|---|

- Hinweis:

- Siehe „Über Kode-Beispiele“

For I/O Registers located in extended I/O map, “IN”, “OUT”, “SBIS”, “SBIC”, “CBI”, and “SBI” instructions must

be replaced with instructions that allow access to extended I/O. Typically “LDS” and “STS” combined with

“SBRS”, “SBRC”, “SBR”, and “CBR”.

Die Empfangsfunktion liest alle I/O Register in das Register File bevor eine weitere Berechnung erfolgt.

Das gibt eine optimale Ausnutzung des Empfangsbuffers,

da der Empfangsbuffer durch das Auslesen geleert wird

und daher so früh wie möglich für die Aufnahme neuer Daten bereit steht.

20.7.3 Empfangs-komplett-Flag und Interrupt

Das USART hat ein Flag, das seinen Zustand signalisiert.

Das Receive Complete Flag (RXC) zeigt an, dass ungelesene Daten im Empfangsbuffer stehen. Das Bit ist 1, wenn ungelesene Daten im Empfangsbuffer liegen und es ist 0, wenn der Empfangsbuffer leer ist, d.h. wenn er keine ungelesenen Daten enthält. Wenn der Empfänger gesperrt wird (RXEN = 0), dann wird der Empfangsbuffer geleert und konsequenter Weise wird das RXC Bit gelöscht.

Wenn das Receive Complete Interrupt Enable (RXCIE) Bit im UCSRB Register gesetzt ist,

wird der USART Receive Complete Interrupt so lange ausgeführt wie das RXC Flag gesetzt ist,

vorausgesetzt, die Interrupts sind global freigegeben.

Wenn eine Interruptgesteuerter Datenempfang verwendet wird,

muss die Interruptroutine die empfangenen Daten aus dem UDR Register auslesen,

um das RXC Flag zu löschen.

Andernfalls tritt nach dem Beenden der Interruptroutine sofort ein neuer Interrupt auf.

20.7.4 Empfangsfehler-Flags

Der USART Empfänger hat drei Fehler Flags: Frame Error (FE), Data OverRun (DOR) und Parity Error (PE).

Auf alle Flags kann durch Lesen des UCSRA Registers zugegriffen werden.

Die Fehler Flags werden im Eingangsbuffer zusammen mit dem Frame,

für den sie den Fehlerstatus signalisieren, abgelegt.

Da auch die Fehler Flags gebuffert werden, muss das UCSRA Register ausgelesen werden,

bevor der Empfangsbuffer (UDR) gelesen wird,

da das Lesen des UDR I/O Speicherzelle die Bufferlesestelle verändert.

Eine andere Eigenschaft der Fehler Flags ist,

dass sie durch das Beschreiben durch die Software nicht verändert werden können.

Trotzdem müssen alle Flags beim Schreiben in das UCSRA Register auf Null gesetzt sein,

um die Kompatibilität zu zukünftigen USART Erweiterungen sicherzustellen.

Keines der Fehler Flags löst einen Interrupt aus.

Das Frame Error (FE) Flag zeigt des Status des ersten Stoppbits des als nächstes auszulesenden Frames an,

der im Empfangsbuffer steht.

Das FE Bit ist null, wenn das Stoppbit korrekt (als 1) gelesen wurde und das Bit ist eins,

wenn das Stoppbit falsch (also 0) war.

Dieses Bit kann also verwendet werden, um Synchronisationsfehler, Abbrüche oder Protokollfehler zu erkennen.

Das FE Flag wird durch das Setzen des USBS Bits im UCSRC Register nicht beeinflusst,

da der Empfänger alle Stoppbits außer dem ersten ignoriert.

Um die Kompatibilität zu zukünftigen Bausteinen zu gewährleisten,

sollte das Bit beim Schreiben in das UCSRA Register auf 0 gesetzt sein.

Das Data OverRun Flag (DOR) signalisiert einen Datenverlust durch den Überlauf des Empfangsbuffers.

Ein Datenüberlauf tritt auf, wenn der Empfangsbuffer voll ist (also zwei Zeichen enthält),

ein neues Zeichen im Empfangsschieberegister wartet und ein neues Startbit erkannt wird.

Wenn das DOR Flag gesetzt ist, sind also ein oder mehrere Frames

zwischen dem zuletzt gelesenen Frame und dem nächsten Frame,

des aus dem UDR gelesen werden kann, verloren gegangen.

Um die Kompatibilität zu zukünftigen Bausteinen zu gewährleisten,

sollte das Bit beim Schreiben in das UCSRA Register auf 0 gesetzt sein.

Das DOR Flag wird gelöscht, wenn ein empfangenes Frame erfolgreich aus dem Schieberegister

in den Eingangsbuffer transportiert wurde.

Das Parity Error Flag (PE) zeigt an, dass der nächste Frame im Empfangsbuffer einen Paritätsfehler

beim Empfangen hatte. Wenn der Paritätscheck nicht freigegeben ist, wird das PE Bit immer als 0 gelesen.

Um die Kompatibilität zu zukünftigen Bausteinen zu gewährleisten,

sollte das Bit beim Schreiben in das UCSRA Register auf 0 gesetzt sein.

20.7.5 Paritätsprüfer

Der Paritätsprüfer ist aktiv, wenn das obere USART Parity Mode Bit (UPM1) gesetzt ist.

Die Art des Paritätschecks (gerade oder ungerade) wird durch das UPM0 Bit festgelegt.

Wenn freigegeben, berechnet der Paritätsprüfer die Parität der Datenbits

des einkommenden Frames und vergleicht das Ergebnis mit dem Paritätsbit des Frames.

Das Ergebnis des Vergleiches wird zusammen mit den empfangenen Daten und Stoppbits im Empfangsbuffer gespeichert.

Das Parity Error Flag (PE) kann dann durch die Software ausgelesen werden, um zu überprüfen,

ob das Frame einen Paritätsfehler hat.

Das PE Bit ist gesetzt, wenn das nächste Zeichen, das aus dem Empfangsbuffer ausgelesen werden kann,

beim Empfang einen Paritätsfehler hatte und in diesem Augenblick der Paritätscheck freigegeben war (UPM1 = 1).

Das Bit ist so lange gültig, bis der Empfangsbuffer gelesen wird.

20.7.6 Deaktivierung des Empfängers

Im Gegensatz zum Sender wirkt das Sperren des Empfängers sofort.

Die Daten eines laufenden Empfanges gehen daher verloren.

Wenn der Empfänger gesperrt wird (RXEN wird auf 0 gesetzt),

dann überschreibt der Empfänger nicht länger die normale Funktion des RxD Portpins.

Der Empfängerbuffer FIFO wird gespült wenn der Empfänger gesperrt wird.

Die übrig bleibenden Daten im Buffer werden gelöscht.

20.7.7 Ausräumen des Empfangspuffers

Der Empfängerbuffer FIFO wird geleert, wenn der Empfänger gesperrt wird,

d.h. der Buffer wird von seinem Inhalt entleert.

Ungelesene Daten gehen dadurch verloren.

Wenn der Buffer während des normalen Betriebes geleert werden soll,

zum Beispiel aufgrund eines Fehlers, so sollte das UDR I/O Register gelesen werden,

bis das RXD Flag Null wird.

Das folgende Beispiel zeigt, wie der Eingangsbuffer geleert werden kann.

- Hinweis:

- Siehe „Über Kode-Beispiele“

For I/O Registers located in extended I/O map, “IN”, “OUT”, “SBIS”, “SBIC”, “CBI”, and “SBI” instructions must

be replaced with instructions that allow access to extended I/O. Typically “LDS” and “STS” combined with

“SBRS”, “SBRC”, “SBR”, and “CBR”.

20.8 Asynchroner Datenempfang

Der USART enthält eine Takt- und Datenwiederherstellungseinheit,

um den asynchronen Datenempfang zu handhaben.

Die Taktwiederherstellungslogik wird verwendet,

um den internen Takt des Baudratengenerators mit dem am RxD Pin

eingehenden seriellen Rahmen zu synchronisieren.

Die Datenwiederherstellungslogik tastet jedes eingehende Bit ab

und filtert es in einem Tiefpass.

Dadurch verbessert sich die Störanfälligkeit es Empfängers.

Der Arbeitsbereich beim asynchronen Empfang hängt von der Genauigkeit

des internen Baudraten Taktes, der Genauigkeit der ankommenden Rahmens

und der Anzahl der Bits pro Rahmen ab.

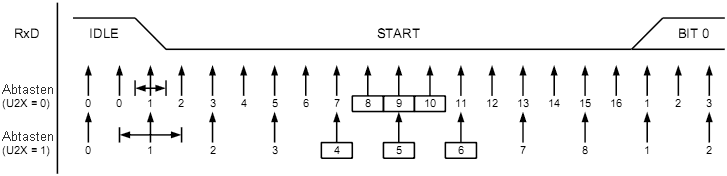

20.8.1 Asynchrone Taktregenerierung

Die Taktwiederherstellungslogik synchronisiert den internen Takt mit dem eingehenden seriellen Frame.

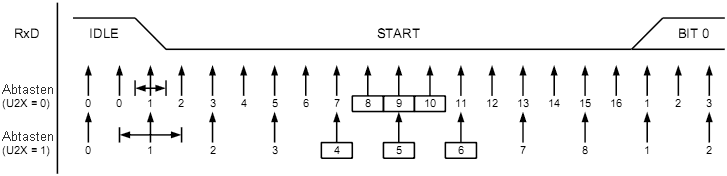

Das nachfolgende Bild zeigt den Abtastvorgang des Startbits eines ankommenden Frames.

Die Abtastrate ist im normalen Modus das 16-fache und im Modus mit doppelter Geschwindigkeit

das 8-fache der Baudrate. Die Pfeile zeigen die Synchronisationsabweichungen im Abtastprozess.

Zu beachten ist die größere Zeitabweichung wenn der Modus mit doppelter Geschwindigkeit verwendet wird (U2X = 1).

Die Abtastungen, die mit Null bezeichnet sind, sind Abtastungen, die ausgeführt wurden,

als die RxD Leitung inaktiv war.

Bild 20-5: Startbit-Erfassung

Wenn die Taktwiederherstellungslogik einen High (inaktiv) zu Low (Startbit) Übergang auf der RxD Leitung erkennt,

beginnt die Sequenz zur Startbiterkennung.

Gehen wir davon aus, dass die Abtastung 1 die erste Nullabtastung war.

Dann verwendet die Taktwiederherstellungslogik im normalen Modus die 8, 9 und 10 Abtastung,

um zu entscheiden, ob ein gültiges Startbit empfangen wurde.

Im Modus mit doppelter Geschwindigkeit werden die Abtastungen 4, 5 und 6 verwendet.

Wenn zwei oder mehr der drei Abtastungen als High erkannt werden,

wird das Startbit als Störspitze interpretiert

und der Empfänger wartet auf das Erkennen des nächsten High-Low Übergangs.

Immer wenn ein gültiges Startbit erkannt wurde,

ist die Taktwiederherstellungslogik synchronisiert und die Datenwiederherstellung kann beginnen.

Der Synchronisationsvorgang wird bei jedem Startbit wiederholt.

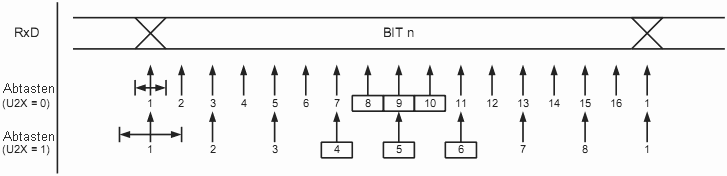

20.8.2 Asynchrone Datenregenerierung

Wenn der Empfängertakt durch das Startbit synchronisiert ist, kann die Datenwiederherstellung beginnen.

Auch die Datenwiederherstellungseinheit tastet im normalen Modus 16 mal

und im Modus mit doppelter Geschwindigkeit 8 mal ab.

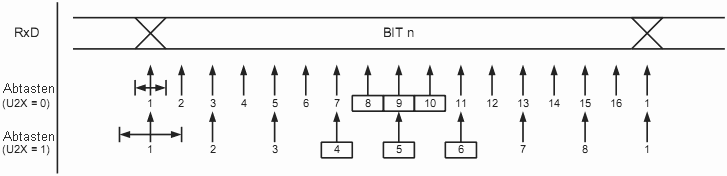

Das nachfolgende Bild zeigt das Abtasten eines Datenbits oder des Paritätsbits.

Jeder Abtastung wird eine Nummer gegeben, die mit dem Status der Wiederherstellungseinheit übereinstimmt.

Bild 20-6: Daten- und Paritätsbit-Erfassung

Die Entscheidung über den logischen Pegel des empfangenen Bits treffen die drei Abtastungen

in der Mitte (Nummer in einem Kästchen) der Abtastsequenz durch Mehrheitsentscheidung.

Die Mehrheitsentscheidung läuft wie folgt:

Haben zwei oder alle Abtastungen High-Pegel, so wird das empfangene Bit als 1 erkannt,

haben zwei oder alle Abtastungen Low-Pegel, so wird das empfangene Bit als 0 erkannt.

Der Prozess der Mehrheitsentscheidung arbeitet wie ein Tiefpassfilter für die über den RxD Pin ankommenden Signale.

Der Wiederherstellungsvorgang wird so lange wiederholt,

bis ein vollständiger Frame empfangen wurde, inklusive des ersten Stoppbits.

Man beachte: Der Empfänger wertet nur das erste Stoppbit aus.

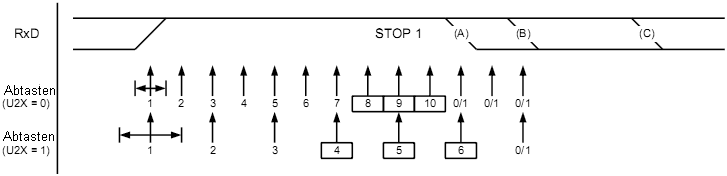

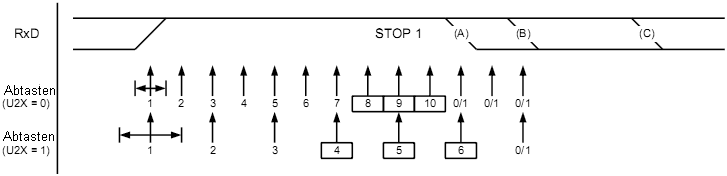

Das nachfolgende Bild zeigt die Abtastung des Stoppbits

und den frühstmöglichen Beginn des Startbits vom nächsten Frame.

Bild 20-7: Stoppbit- und Nächstes-Startbit-Erfassung

Die Mehrheitsentscheidung läuft beim Stoppbit genauso ab,

wie bei den anderen Bits eines Frames.

Wenn das Stopbit als 0 erkannt wird, wird das Frame Error (FE) Flag gesetzt.

Ein neuer High-Low Übergang der das Startbit eines neuen Frames anzeigt,

kann unmittelbar nach dem letzten Bit, das für die Mehrheitsentscheidung benötigt wird, kommen.

Im normalen Modus kann der erste Low-Pegel am Punkt (A) abgetastet werden.

Im Modus mit Doppelter Geschwindigkeit muss der erste Low-Pegel bis zum Punkt (B) warten.

Der Punkt (C) kennzeichnet ein Stoppbit mit voller Länge.

Die frühe Startbiterkennung hat Einfluss auf den Arbeitsbereich des Empfängers.

20.8.3 Asynchroner Arbeitsbereich

Der Arbeitsbereich des Empfängers ist von der Fehlabweichung zwischen der empfangenen Bitrate

und der internen Baudrate abhängig.

Wenn der Sender die Frames mit zu großer oder zu kleiner Bitrate sendet

oder die interne Baudrate des Empfängers nicht die gleiche Basisfrequenz aufweist,

ist es dem Empfänger nicht möglich die Frames mit den Startbit zu synchronisieren.

Die folgenden Gleichungen können verwendet werden,

um das Verhältnis der ankommenden Datenrate zu der internen Baudrate zu berechnen.

| D | Summe aus Zeichengröße und Größe des Paritätsbits

|

|---|

| S | Abtastungen pro Bit (S=16 im normalen Modus, S=8 im Modus mit doppelter Geschwindigkeit)

|

|---|

| SF | Nummer der ersten Abtastung für die Mehrheitsentscheidung (SF=8 im normalen Modus, SF=4 im Modus mit doppelter Geschwindigkeit)

|

|---|

| SM | Nummer der mittleren Abtastung für die Mehrheitsentscheidung (SM=9 im normalen Modus, SM=5 im Modus mit doppelter Geschwindigkeit)

|

|---|

Rlangsam| ist das Verhältnis der kleinsten eingehenden Datenrate, die akzeptiert werden kann zur Baudrate des Empfängers

| Rschnell| ist das Verhältnis der größten eingehenden Datenrate, die akzeptiert werden kann zur Baudrate des Empfängers

| | |

|---|

Die nachfolgenden Tabellen zeigen den maximalen Fehler des Baudrate des Empfängers, der toleriert werden kann. Man beachte, dass im normalen Modus größere Abweichungen der Baudrate toleriert werden.

Tabelle 20-2: Empfohlener maximaler Empfängerbaudratenfehler für normale Geschwindigkeit

Daten-

+ Paritätsbits | Rlangsam

in % | Rschnell

in % | Max. Gesamtfehler

in %

| Empfohlener max.

Fehler in %

|

|---|

| 5 | 93,20 | 106,67 | +6,67/-6,8 | ± 3,0

|

| 6 | 94,12 | 105,79 | +5,79/-5,88 | ± 2,5

|

| 7 | 94,81 | 105,11 | +5,11/-5,19 | ± 2,0

|

| 8 | 95,36 | 104,58 | +4,58/-4,54 | ± 2,0

|

| 9 | 95,81 | 104,14 | +4,14/-4,19 | ± 1,5

|

| 10 | 96,17 | 103,78 | +3,78/-3,83 | ± 1,5

|

Tabelle 20-3: Empfohlener maximaler Empfängerbaudratenfehler für doppelte Geschwindigkeit

Daten-

+ Paritätsbits | Rlangsam

in % | Rschnell

in % | Max. Gesamtfehler

in %

| Empfohlener max.

Fehler in %

|

|---|

| 5 | 94,12 | 105,66 | +5,66/-5,88 | ± 2,5

|

| 6 | 94,92 | 104,92 | +4,92/-5,08 | ± 2,0

|

| 7 | 95,52 | 104,35 | +4,35/-4,48 | ± 1,5

|

| 8 | 96,00 | 103,90 | +3,90/-4,00 | ± 1,5

|

| 9 | 96,39 | 103,53 | +3,53/-3,61 | ± 1,5

|

| 10 | 96,70 | 103,23 | +3,23/-3,30 | ± 1,0

|

Die Empfehlungen für den maximalen Baudratenfehler des Empfängers wurden unter der Voraussetzung berechnet, dass Sender und Empfänger den maximalen Fehler gleichermaßen teilen.

Es gibt zwei wichtige Quellen für den Baudratenfehler des Empfängers.

Der Systemtakt (XTAL) des Empfängers hat immer geringe Instabilitäten im Spannungs- und Temperaturbereich.

Wenn ein Quarz zum Erzeugen des Systemtaktes verwendet wird, ist dies selten ein Problem.

Aber bei einem Resonator kann der Systemtakt schon mal um 2% abweichen,

was von der Toleranz des Resonators abhängt.

Die zweite Quelle für Fehler lässt sich besser kontrollieren.

Der Baudratengenerator kann den Systemtakt nicht immer exakt auf die gewünschte Baudrate runterteilen.

In diesem Fall kann ein UBRR Wert genommen werden, der eine akzeptabel kleine Abweichung bringt.

20.9 Multiprozessor-Kommunikation

Das Setzen des Multi-Prozessor Communikaton Mode (MPCM) Bits im UCSRA Register

schaltet eine Filterfunktion für die vom USART empfangenen Rahmens ein.

Rahmens, die keine Adressinformationen enthalten

werden ignoriert und nicht in den Empfangspuffer übernommen.

Dies reduziert die Anzahl der eingehenden Rahmens,

die in einem System mit einer Kommunikation mehrerer MCUs über den selben Datenbus,

von der CPU zu behandelnden sind.

Der Sender wird von den Einstellungen des MPCM Bits nicht beeinflusst,

er muss aber anders verwendet werden,

wenn er Bestandteil eines Multiporzessor Kommunikationssystems ist.

Wenn der Empfänger zum Empfangen von Rahmens mit 5 bis 8 Datenbits eingestellt ist,

zeigt das erste Stoppbit an, ob der Rahmen Daten- oder Adressinformationen enthält.

Wenn der Empfänger aus Rahmens mit 9 Datenbits eingestellt ist,

so wird das neunte Bit (RXB8) verwendet, um Adress- und Dateninformationen zu unterscheiden.

Wenn das Rahmen Type Bit (erstes Stoppbit bzw. neuntes Bit) auf 1 ist,

enthält der Rahmen eine Adresse, wenn der Rahmen Type 0 ist, enthält der Rahmen Daten.

Der Multiprozessor Kommunikations Modus ermöglicht mehreren Slave MCUs

Daten von der Master MCU zu empfangen.

Dies ist möglich, da zuerst das Adressframe dekodiert wird,

um zu ermitteln, welche MCU adressiert wurde.

Wenn ein bestimmter Slave MCU addressiert wurde,

wird der die folgenden Datenrahmens normal empfangen,

während die anderen Slave MCUs diese ignorieren

bis ein weiteres Adressframe empfangen wird.

20.9.1 Anwendung der Multiprozessor-Kommunikation

Eine MCU, die als Master MCU arbeitet, kann das 9-bit Zeichen Frame Format (UCSZ = 7) verwenden. Das neunte Bit (TXB8) muss gesetzt werden, wenn ein Adressframe (TXB8 = 1) oder gelöscht werden, wenn ein Datenframe (TXB8 = 0) gesendet wird. Die Slave MCUs müssen in diesem Fall ebenfalls in das 9-bit Zeichen Frame Format eingestellt sein.

Die folgende Prozedur sollte beim Austausch von Daten im Multiprozessor Modus verwendet werden:

- Alle Slaves in den Multiprozessor Modus setzen (MPCM im UCSRA auf 1)

- Der Master MCU sendet ein Adressframe, das alle Slaves empfangen und lesen. In den Slave MCU wird das RXD Flag im OCSRC Register wie gewöhnlich gesetzt.

- Jeder Slave liest das UDR Register und bestimmt, ob er angesprochen wurde. Wenn ja, so löscht er das MPCM Bit im PCSRA Register, wenn nein, so wartet er auf das nächste Adress Byte und behält die MPCM Einstellungen.

- Die adressierte MCU empfängt alle Datenfarmes, bis ein neues Adressframe empfangen wird. Die anderen Slave MCUs, bei denen das MPCM Bit nach wie vor gesetzt ist, ignorieren die Datenfarmes.

- Wenn das letzte Datenframe durch die adressierte MCU empfangen wurde, setzt auch die adressierte MCU das MPCM Bit wieder auf 1 und wartet auf das nächste Adressframe vom Master. Der Vorgang wiederholt sich dann ab Schritt 2.

Das Verwenden von 5 bis 8-bit Zeichen Frame Formaten ist zwar möglich, aber unpraktisch, da der Empfänger zwischen der Verwendung von n und n+1 Zeichen Frame Format umschalten muss. Das macht voll-duplex Operationen schwierig, da der Sender und der Empfänger die gleichen Zeichenbreiten Einstellungen haben müssen. Wenn 5 bis 8-bit Zeichen Frame Formate verwendet werden, muss der Sender auf zwei Stoppbits (USBS = 1) eingestellt werden, da das erste Stoppbit zum Kennzeichnen des Frametypes verwendet wird.

Man sollte keine Lesen-Ändern-Schreiben Befehle (SBI und CBI) zum Setzen und Löschen des MPCM Bits verwenden. Das MPCM Bit ist in der gleichen I/O Speicherzelle untergebracht wie das TXC Flag und dieses kann versehentlich gelöscht werden, wenn ein SBI oder CBI Befehl ausgeführt wird.

20.10 Beispiele für die Baudraten Einstellung

Für Standard-Quarz- und Resonator-Frequenzen können

die am häufigsten verwendeten Baudraten in asynchronen Modus

durch die Einstellungen des UBRR wie in folgenden Tabellen erzeugt werden.

UBRR-Werte, deren prozentuale Abweichung von der exakten Baudrate

weniger als 0,5 % beträgt sind fett dargestellt.

Höhere Fehlerraten können akzeptiert werden,

allerdings hat der Empfänger dann eine schlechtere Störungssicherheit,

besonders bei langen seriellen Rahmen (siehe asynchrone Arbeitsweise).

Der Fehlerwert kann mit folgender Formel berechnet werden:

20.11 Register-Beschreibung

20.11.1 UDRn — Bidirektionales Datenregister

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0xC6) | RxB[7:0] | UDR0 (Lesen)

|

|---|

| (0xC6) | TxB[7:0] | UDR0 (Schreiben)

|

|---|

| Zugriff | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

Das USART Sender Daten Buffer Register und das Empfänger Daten Buffer Register teilen sich die gleiche I/O Speicherstelle, die mit USART Data Register oder UDR bezeichnet wird. Das Sender Data Buffer Register (TXB) ist das Ziel für Daten, die in das UDR geschrieben werden. Das Lesen des UDR Registers wird den Inhalt des Empfänger Daten Buffer Registers (RXB) zurückgeben. Bei 5, 6 oder 7 Bit Zeichen werden die oberen, ungenutzten Bits vom Sender ignoriert und vom Empfänger auf Null gesetzt.

Der Sendebuffer kann nur beschrieben werden, wenn das UDRE Flag im UCSRC Register gesetzt ist. Daten, die in das UDR geschrieben werden, wenn das UDRE Flag nicht gesetzt ist, werden durch den Sender ignoriert. Wenn Daten in den Senderbuffer geschrieben wurden und der Sender freigegeben ist, wird der Sender die Daten in das Schieberegister laden, sobald das Schieberegister leer ist. Dann werden die Daten seriell über den TxD Pin ausgesendet.

Der Empfängerbuffer besteht aus zwei FIFOs. Die FIFOs ändern ihren Status, wenn auf den Empfängerbuffer zugegriffen wird. Aufgrund dieses Verhaltens des Empfängerbuffers sollten keine Lesen-Ändern-Schreiben Befehle auf diese Speicherstelle angewendet werden. Man muss auch vorsichtig bei der Verwendung von Bit-Test Befehlen sein, da diese ebenfalls den Status des FIFO verändern.

20.11.2 UCSRnA — Kontroll- und Statusregister A

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0xC0) | RXC0 | TXC0 | UDRE0 | FE0 | DOR0 | UPE0 | U2X0 | MPCM0 | UCSR0A

|

|---|

| Zugriff | R | R/W | R | R | R | R | R/W | R/W

|

| Startwert | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0

|

- Bit 7 – RXC: USART Receive Complete

Dieses Bit ist gesetzt, wenn ungelesenen Daten im Empfängerbuffer vorliegen und das Bit wird gelöscht,

wenn der Empfängerbuffer leer ist, d.h. keine ungelesenen Daten enthält.

Wenn der Empfänger gesperrt wird, wird der Empfängerbuffer gelöscht und somit auch das RXC Bit auf Null gesetzt.

Das RXC Falg kann genutzt werden, um einen Receive Complete Interrupt auszulösen (siehe RXCIE Bit).

- Bit 6 – TXC: USART Transmit Complete

Dieses Bit ist gesetzt, wenn ein Frame im Senderschieberegister vollständig ausgeschoben wurde

und keine weiteren Daten im Senderbuffer (UDR) warten.

Das TXC Flag wird automatisch gelöscht, wenn der Transmit Complete Interrupt ausgeführt wird

oder eine logische 1 in dieses Bit geschrieben wird.

Das TXC Falg kann genutzt werrden, um einen Transmit Complete Interrupt auszulösen (siehe TXCIE Bit).

- Bit 5 – UDRE: USART Data Register Empty

Das UDER Flag zeigt an, dass der Senderbuffer zur Aufnahme neuer Daten bereit ist.

Wenn UDRE auf 1 ist, ist der Buffer leer und kann somit mit neuen Daten beschrieben werden.

Das UDRE Falg kann genutzt werrden, um einen Data Register Empty Interrupt auszulösen (siehe UDRIE Bit).

Nach einem Reset wird das UDRE Bit gesetzt und zeigt an, dass der Sender fertig ist.

Dieses Bit ist gesetzt, wenn das nächste Zeichen im Empfängerbuffer einen Framefehler beim Empfangen hatte,

d.h wenn das erster Stoppbit des nächten Zeichens im Empfängerbuffer Null war.

Dieses Bit ist so lange gültig, bis der Empfangsbuffer gelesen wird.

Das FE Bit ist Null, wenn das Stoppbit der empfangenen Daten 1 war.

Das Bit sollte immer auf 0 gesetzt werden, wenn in das UCSRA Register geschrieben wird.

- Bit 3 – DOR: Data OverRun

Dieses Bit wird gesetzt, wenn eine Datenüberlaufbedingung erkannt wurde.

Ein Datenüberlauf tritt auf, wenn der Empfangsbuffer voll ist (zwei Zeichen enthält),

ein weiteres Zeichen im Empfangsschieberegister wartet und eine neue Startbedingung erkannt wird.

Dieses Bit ist so lange gültig, bis der Empfangsbuffer gelesen wird.

Das Bit sollte immer auf 0 gesetzt werden, wenn in das UCSRA Register geschrieben wird.

Dieses Bit ist gesetzt, wenn das nächste Zeichen im Empfangsbuffer einen Paritätsfehler

beim Empfang hatte und der Paritätscheck zu diesem Zeitpunkt freigegeben war (UPM = 1).

Dieses Bit ist so lange gültig, bis der Empfangsbuffer gelesen wird.

Das Bit sollte immer auf 0 gesetzt werden, wenn in das UCSRA Register geschrieben wird.

- Bit 1 – U2X: Double the USART Transmission speed

Dieses Bit hat nur im asynchronen Modus Auswirkungen.

Das Bit sollte im synchronen Modus auf Null gesetzt sein.

Wird das Bit mit einer 1 beschrieben, so wird der Teiler des Baudratengenerators von 16 auf 8 gesetzt,

was eine Verdopplung der Übertragungsrate im asynchronen Modus zur Folge hat.

- Bit 0 – MPCM: Multi-Prozessor Communication Mode

Dieses Bit gibt die Multiprozessor Kommunikation frei.

Wenn das MPCM Bit auf 1 gesetzt ist, werden alle ankommenden Frames,

die keine Adressinformationen vom USART Empfänger ignoriert.

Der Sender wird durch das MPCM Bit nicht beeinflusst.

20.11.3 UCSRnB — Kontroll- und Statusregister B

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0xC1) | RXCIE0 | TXCIE0 | UDRIE0 | RXEN0 | TXEN0 | UCSZ02 | RXB80 | TXB80 | UCSR0B

|

|---|

| Zugriff | R/W | R/W | R/W | R/W | R/W | R/W | R | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

- Bit 7 – RXCIE: USART RX Complete Interrupt Enable

Das Setzen dieses Bits auf 1 gibt den Interrupt für das RXC Flag frei.

Der USART Receive Complete Interrupt wird nur ausgeführt, wenn RXCIE auf 1 steht,

die Interrupts global freigegeben sind und das RXC Flag im UCSRA gesetzt wird.

- Bit 6 – TXCIE: TX Complete Interrupt Enable

Das Setzen dieses Bits auf 1 gibt den Interrupt für das TXC Flag frei.

Der USART Transmit Complete Interrupt wird nur ausgeführt, wenn TXCIE auf 1 steht,

die Interrupts global freigegeben sind und das TXC Flag im UCSRA gesetzt wird.

- Bit 5 – UDRIE: USART Data Register Empty Interrupt Enable

Das Setzen dieses Bits auf 1 gibt den Interrupt für das UDRE Flag frei.

Ein Data Register Empty Interrupt wird nur ausgeführt, wenn UDRIE auf 1 steht,

die Interrupts global freigegeben sind und das UDRE Flag im UCSRA gesetzt wird.

- Bit 4 – RXEN: Receiver Enable

Das Setzen dieses Bits auf 1 gibt den USART Empfänger frei.

Der Empfänger überschreibt die normale Portfunktion des RxD Pins, wenn er freigegeben ist.

Das Sperren des Empfängers löscht den Empfängerbuffer und macht die FE, DOR und PE Flags ungültig.

- Bit 3 – TXEN: Transmitter Enable

Das Setzen dieses Bits gibt den USART Sender frei.

Der Sender überschreibt die normale Portfunktion des TxD Pins, wenn er freigegeben ist.

Das Sperren des Senders (TXEN auf 0 setzen) wird erst wirksam,

wenn laufende und wartende Übertragungen abgeschlossen sind,

d.h. wenn das Senderschieberegister und der Senderbuffer keine noch zu übertragenden Daten mehr enthalten.

Nach dem Sperren wird der TxD Port nicht meht überschrieben.

- Bit 2 – UCSZ2: Character Size 2

Dieses Bit legt zusammen mit den UCSZ1 und UCSZ0 Bits im UCSRC Register

die Anzahl der Bits pro Zeichen in einem Frame für den Empfänger und den Sender fest.

- Bit 1 – RXB8: Receive Data Bit 8

Das RXB8 Bit ist das neunte Datenbit des empfangenen Zeichens,

wenn mit Frames mit neun Datenbits gearbeitet wird.

Es muss gelesen werden bevor die unteren Bits aus dem UDR Register gelesen werden.

- Bit 0 – TXB8: Transmit Data Bit 8

Das TXB8 Bit ist das neunte Datenbit des zu sendenden Zeichens,

wenn mit Frames mit neun Datenbits gearbeitet wird.

Es muss geschrieben werden bevor die unteren Bits in das UDR Register geschrieben werden.

20.11.4 UCSRnC — Kontroll- und Statusregister C

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0xC2) | UMSEL01 | UMSEL00 | UPM01 | UPM00 | USBS0 | UCSZ01 | UCSZ00 | UCPOL0 | UCSR0C

|

|---|

| Zugriff | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0

|

Diese Bit wählt zwischen einem Zugriff auf das UCSRC oder dass UBRRH Register aus.

Es wird als 1 gelesen, wenn das UCSRC Register gelesen wird.

Das URSEL Bit muss 1 sein, wenn in das UCSRC Register geschrieben wird.

- Bit 6 – UMSEL: USART Mode Select

Dieses Bit wählt zwischen dem asynchronen und dem synchronen Betriebsmodus aus.

Bei UMSEL = 0 ist der asynchrone, bei UMSEL = 1 der synchrone Betriebsmodus ausgewählt.

Tabelle 20-8: Werte für UMSELn-Bits

| UMSELn1 | UMSELn0 | Modus

|

|---|

| 0 | 0 | Anynchrone USART (also ART)

|

| 0 | 1 | Synchrone USART (also SRT)

|

| 1 | 0 | reserviert

|

| 1 | 1 | SPI-Master (MSPIM)(1)

|

- Hinweis:

- Siehe USART im SPI-Modus zur Beschreibung der SPI-Master-Betriebsart

- Bit 5 und 4 – UPM1, UPM0: Parity Mode

Diese Bits geben den Paritätscheck frei und setzen seinen Typ.

Wenn freigegeben, erzeugt und sendet der Sender automatisch die Parität der gesendeten Daten in jedem Frame.

Der Empfänger erzeugt den Paritätswert für die ankommenden Daten

und vergleicht diesen mit den Einstellungen des UPM0 Bits.

Wenn keine Übereinstimmung erkannt wird, wird das PE Flag im UCSRA Register gesetzt.

Tabelle 20-9: Werte für UPMn-Bits

| UPMn1 | UPMn0 | Paritäts-Modus

|

|---|

| 0 | 0 | Kein Paritätsbit

|

| 0 | 1 | reserviert

|

| 1 | 0 | Gerade Parität

|

| 1 | 1 | Ungerade Parität

|

- Bit 3 – USBS: Stop Bit Select

Dieses Bit legt die Anzahl der Stoppbits fest, die vom Sender eingefügt werden.

Bei USBS = 0 wird ein Stoppbit, bei USBS = 1 werden zwei Stoppbits eingefügt.

Der Empfänger ignoriert die Einstellungen des USBS Bits.

Tabelle 20-10: Werte für das USBS-Bit

| USBSn | Stoppbits

|

|---|

| 0 | 1 Bitzeit

|

| 1 | 2 Bitzeiten

|

- Bit 2 und 1 – UCSZ1, UCSZ0: Character Size 1 und 0

Diese Bits legt zusammen mit dem UCSZ2 Bits im UCSRB Register

die Anzahl der Bits pro Zeichen in einem Frame für den Empfänger und den Sender fest.

Tabelle 20-11: Werte für UCSZn-Bits

| UCSZn2 | UCSZn1 | UCSZn0 | Zeichenlänge

|

|---|

| 0 | 0 | 0 | 5 Bit

|

| 0 | 0 | 1 | 6 Bit

|

| 0 | 1 | 0 | 7 Bit

|

| 0 | 1 | 1 | 8 Bit

|

| 1 | 0 | 0 | reserviert

|

| 1 | 0 | 1 | reserviert

|

| 1 | 1 | 0 | reserviert

|

| 1 | 1 | 1 | 9 Bit

|

- Bit 0 – UCPOL: Taktpolarität

Dieses Bit wird nur im synchronen Modus verwendet.

Im asynchronen Modus muss das Bit mit einer Null beschrieben werden.

Das UCPOL-Bit legt die Beziehung zwischen dem Wechsel der Ausgangsdaten

und dem Abtasten der Eingangsdaten und dem synchronen Taktsignal (XCK) fest.

20.11.5 UBRRn — Baudraten-Register

| Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8

|

| (0xC5) | - | - | - | - | UBRR0[11:8] | UBRR0H

|

|---|

| (0xC4) | UBRR0[7:0] | UBRR0L

|

|---|

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| Zugriff | R | R | R | R | R/W | R/W | R/W | R/W

|

| R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

Bit 15 bis 12 – Res: Reservierte Bits

Dieses Bits sind für zukünftige Erweiterungen reserviert.

Um die Kompatibilität sicherzustellen müssen diese Bits mit Null beschrieben werden,

wenn UBRRH beschrieben wird.

- Bit 11 bis 0 – UBRR11 bis UBRR0: USART Baud Rate Register

Dieses Bits bilden zusammen ein 12-bit Register,

welches die USART-Baudrate beinhaltet.

Das UBRRH enthält die vier obersten Bits,

das UBRRL die acht unteren Bits der USART-Baudrate.

Laufende Übertragungen des Senders und Empfängers werden unbrauchbar,

wenn die Baudrate verändert wird.

Ein Schreiben in das UBRRL-Register hat eine unmittelbare Aktualisierung

des Baudraten-Vorteilers zur Folge.