16. 16-bit-Zähler/Zeitgeber 1

16.1 Features

- Echtes 16-bit Design

- Zwei unabhängige Output Compare Einheiten

- Zweifach gebufferte Output Compare Register

- Eine Input Capture Einheit

- Input Capture Rauschunterdrückung

- Löschen des Timers bei Compare Match (auto Reload)

- Glitch-freier, phasenkorrekter Pulsweitenmodulator (PWM)

- Variable PWM Frequenz

- Frequenzgenerator

- Externer Ereigniszähler

- Vier unabhängige Interruptquellen (TOV1, OCF1A, OCF1B und ICF1)

16.2 Übersicht

Viele Register und Bits in diesem Dokument werden allgemein beschrieben.

Der Index „n“ steht für die Nummer des Zähler/Zeitgeber,

in diesem Fall also für eine 1, und der Index „x“ steht für den Kanal der Output Compare Einheit.

In einem Programm müssen aber immer die präzisen Bezeichnungen angegeben werden,

also z.B.

TCNT1 um auf den Wert des Zähler/Zeitgeber1 zuzugreifen.

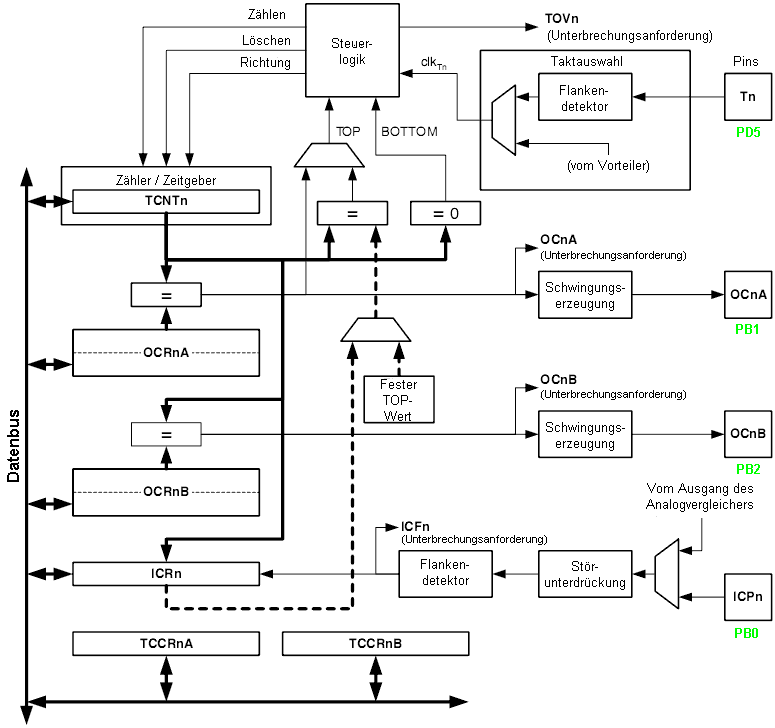

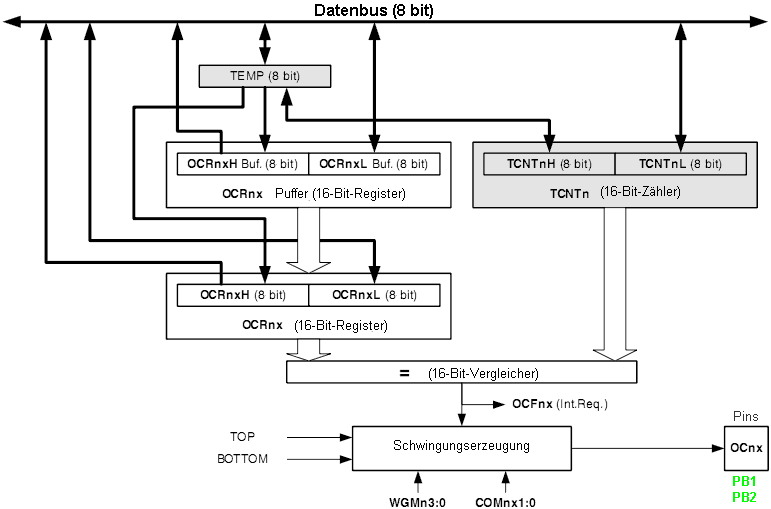

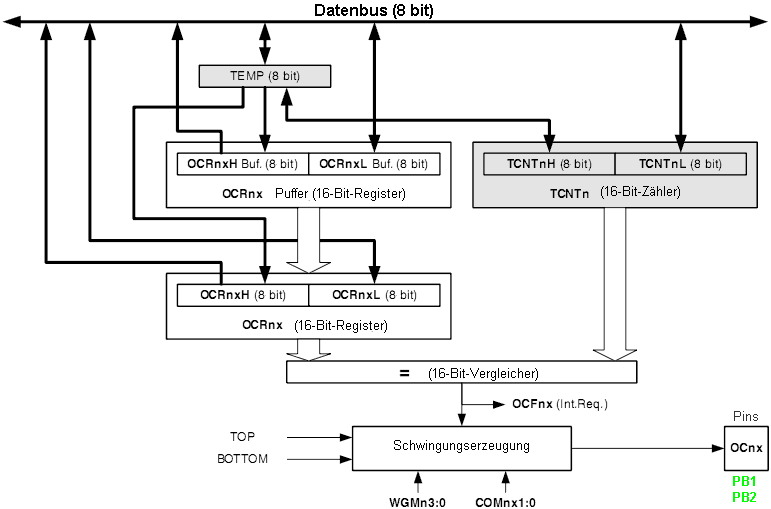

Ein einfaches Blockschaltbild des 16-bit Zähler/Zeitgeber ist nachfolgend dargestellt.

Die Nummern der Pins sind von der Gehäuseform des Bausteins abhängig (siehe Anschlussbelegung).

Die I/O-Register, die dazugehörigen I/O-Bits und die I/O-Pins,

auf die die CPU direkt zugreifen kann, sind fett dargestellt.

16.2.1 Register

Das Zähler/Zeitgeber Register (TCNT1), die Output Compare Register (OCR1A/B)

und das Input Capture Register (ICR1) sind alle 16-bit Register.

Der Zugriff auf diese Register erfordert eine besondere Vorgehensweise,

wie sie im Kapitel „Zugriff auf die 16-bit Register“ beschrieben wird.

Die Zähler/Zeitgeber Control Register (TCCR1A/B) sind 8-bit Register,

auf die die CPU normal zugreifen kann.

Die Signale der Interruptanforderungen

(im Blockschaltbild als Int.Req.

bezeichnet) sind im

Timer Interrupt Flag Register (TIFR) sichtbar.

Alle Interrupts können individuell im Timer Interrupt Mask Register (TIMSK)

maskiert werden.

Die beiden letztgenannten Register sind im Blockschaltbild nicht abgebildet,

da sie auch die Bits für andere Timer-Einheiten enthalten.

Der Zähler/Zeitgeber kann intern, über einen Vorteiler

oder durch eine externe Taktquelle am T1 Pin getaktet werden.

Die Taktauswahl-Logik gibt vor,

durch welchen Takt und mit welcher Flanke der Timer

seinen Wert inkrementiert oder dekrementiert.

Der Zähler/Zeitgeber ist inaktiv, wenn keine Taktquelle ausgewählt wurde.

Der Ausgang der Taktauswahl-Logik wird als Timer-Takt clkT1 bezeichnet.

Die zweifach gebufferten Output Compare Register (OCR1A/B)

werden ständig mit dem Wert des Timers verglichen.

Das Ergebnis dieses Vergleiches kann vom Wellenformerzeuger genutzt werden,

um eine PWM oder eine variable Frequenz am Ausgang

des Output Compare Pins (OC1A/B) zu erzeugen.

Das Ereignis der Vergleichsübereinstimmung setzt außerdem

das Compare Match Flag (OCF1A/B),

das genutzt werden kann, um einen Output Compare Interrupt auszulösen.

Das Input Capture Register kann den Wert des Zähler/Zeitgebers vorgeben,

wenn ein externes Ereignis an dem Input Capture Pin (ICP1)

oder den Analog-Comparator Pins dies antriggert.

Die Input Capture Einheit beinhaltet einen digitalen Filter,

um Spitzen bei Wertveränderungen zu unterdrücken.

Der Top-Wert oder der Maximal-Wert des Timers kann in einigen Betriebsmodi

durch das OCR1A Register,

das ICR1 Register oder durch einen festen Wert vorgegeben werden.

Wenn das OCR1A Register als Top-Wert im PWM-Modus verwendet wird,

kann es nicht mehr verwendet werden, um den PWM Ausgang zu erzeugen.

Der Top-Wert wird in diesen Fällen zweifach gebuffert

und kann daher auch während des Laufens verändert werden.

Wenn ein fester Top-Wert erforderlich ist,

kann das ICR1 Register verwendet werden,

wodurch das OCR1A Register für den PWM-Ausgang zur Verfügung steht.

16.2.2 Definitionen

| BOTTOM

| Der Zähler erreicht BOTTOM, wenn er 0000 wird.

|

| MAX

| Der Zähler erreicht sein MAXimum, wenn er FFFFh (65535 dezimal) wird

|

| TOP

| Der Zähler erreicht TOP, wenn die Zählung einen oberen Grenzwert erreicht.

Als oberer Wert kann 00FF, 01FF und 03FF oder der Wert im OCR1A bzw.

ICR1 Register festgelegt werden.

Diese Festlegung ist vom Operationsmodus abhängig.

|

16.3 Zugriff auf 16-Bit-Register

Das TCNT1, die OCR1A/B und das ICR1 Register sind 16-bit Register, auf die die CPU über den 8-bit Datenbus zugreift.

Der Zugriff muss also in zwei Schreib- oder Lesebefehlen erfolgen.

Daher hat der 16-bit Timer ein 8-bit Zwischenspeicher,

in dem das High-Byte des 16-bit Zugriffes temporär zwischengespeichert wird.

Dieses eine Schattenregister wird für alle 16-bit-Register des Timers verwendet.

Der Zugriff auf das Low-Byte triggert den 16-bit-Lese- oder -Schreibbefehl.

Wenn das Low-Byte eines 16-bit Registers durch die CPU geschrieben wird,

wird im gleichen Taktzyklus auch der High-Teil aus dem Schattenregister in das 16-bit Register geschrieben.

Wenn das Low-Byte eines 16-bit Registers gelesen wird,

wird im gleichen Taktzyklus das High-Byte aus dem Register

in das Schattenregister kopiert.

Nicht alle 16-bit-Zugriffe verwenden das Schattenregister für das High-Byte:

Beim Lesen der OCR1A/B-Register wird das Schattenregister nicht verwendet.

Bei einem 16-bit Schreibvorgang muss erst das High-Byte geschrieben werden,

bevor das Low-Byte geschrieben wird.

Bei einem 16-bit Lesevorgang wird erst das Low-Byte gelesen,

anschließend das High-Byte.

Das folgende Beispiel zeigt den Zugriff auf das 16-bit Timer Register,

wobei unterstellt wird, dass ein zwischenzeitlicher Interrupt

das Schattenregister nicht verändern kann.

Das gleiche Prinzip kann auch beim Zugriff auf die OCR1A/B Register

oder das ICR1 Register angewandt werden.

Bei dem „C“ Beispiel handelt es sich um eine 16-bit Adresse.

| Kodebeispiel in Assembler

|

|---|

...

; Setze TCNT1 auf 0x01FF

ldi r17,0x01

ldi r16,0xFF

out TCNT1H,r17

out TCNT1L,r16

; Lese TCNT1 nach r17:r16

in r16,TCNT1L

in r17,TCNT1H

...

| Kodebeispiel in C

|

|---|

unsigned int i;

...

/* Setze TCNT1 auf 0x01FF */

TCNT1 = 0x1FF;

/* Lese TCNT1 nach i */

i = TCNT1;

...

| |

- Hinweis:

- See ”About Code Examples” on page 8.

For I/O Registers located in extended I/O map, “IN”, “OUT”, “SBIS”, “SBIC”, “CBI”, and “SBI” instructions must

be replaced with instructions that allow access to extended I/O.

Typically “LDS” and “STS” combined with

“SBRS”, “SBRC”, “SBR”, and “CBR”.

Es ist wichtig zu beachten, dass die Zugriffe auf das Low- und High-Byte

zwei zusammenhängende Befehle sind.

Tritt während der beiden Befehle, mit denen auf das 16-bit Register

zugegriffen wird, ein Interrupt auf, in dessen Bearbeitung

ebenfalls auf eines der 16-bit Register zugegriffen wird,

so wird der durch den Interrupt unterbrochene Zugriff fehlerhaft werden.

Daher sollte in den Fällen, in denen das Hauptprogramm

und eine Interruptroutine auf die 16-bit Register zugreifen,

im Hauptprogramm die Interrupts vor dem Zugriff gesperrt werden.

Das nachfolgende Beispiel zeigt die beiden zusammenhängenden Befehle

zum Auslesen des TCNT1 Registers.

Das Auslesen der OCR1A/B und des ICR1 Registers

kann nach dem gleichen Prinzip erfolgen.

| Kodebeispiel in Assembler

|

|---|

TIM16_ReadTCNT1:

; Globales Interruptflag retten

in r18,SREG

; Interrupts sperren

cli

; Lese TCNT1 nach r17:r16

in r16,TCNT1L

in r17,TCNT1H

; Globales Interruptflag wiederherstellen

out SREG,r18

ret

| Kodebeispiel in C

|

|---|

unsigned int TIM16_ReadTCNT1(void) {

unsigned char sreg;

unsigned int i;

/* Globales Interruptflag retten */

sreg = SREG;

/* Interrupts sperren */

_CLI();

/* Lese TCNT1 nach i */

i = TCNT1;

/* Globales Interruptflag wiederherstellen */

SREG = sreg;

return i;

}

| |

- Hinweis:

- See ”About Code Examples” on page 8.

For I/O Registers located in extended I/O map, “IN”, “OUT”, “SBIS”, “SBIC”, “CBI”, and “SBI” instructions must

be replaced with instructions that allow access to extended I/O.

Typically “LDS” and “STS” combined with

“SBRS”, “SBRC”, “SBR”, and “CBR”.

Das Assembler Beispiel schreibt den Wert des TCNT1

in das Registerpaar R17:R16 zurück.

Das nachfolgende Beispiel zeigt die beiden zusammenhängenden Befehle

zum Schreiben des TCNT1 Registers.

Das Schreiben der OCR1A/B und des ICR1 Registers

kann nach dem gleichen Prinzip erfolgen.

| Kodebeispiel in Assembler

|

|---|

TIM16_WriteTCNT1:

; Globales Interruptflag retten

in r18,SREG

; Interrupts sperren

cli

; Setze TCNT1 auf r17:r16

out TCNT1H,r17

out TCNT1L,r16

; Globales Interruptflag wiederherstellen

out SREG,r18

ret

| Kodebeispiel in C

|

|---|

void TIM16_WriteTCNT1(unsigned int i) {

unsigned char sreg;

unsigned int i;

/* Globales Interruptflag retten */

sreg = SREG;

/* Interrupts sperren */

_CLI();

/* Setze TCNT1 auf i */

TCNT1 = i;

/* Globales Interruptflag wiederherstellen */

SREG = sreg;

}

| |

- Hinweis:

- See ”About Code Examples” on page 8.

For I/O Registers located in extended I/O map, “IN”, “OUT”, “SBIS”, “SBIC”, “CBI”, and “SBI” instructions must

be replaced with instructions that allow access to extended I/O.

Typically “LDS” and “STS” combined with

“SBRS”, “SBRC”, “SBR”, and “CBR”.

Das Assembler Beispiel unterstellt, dass im Registerpaar R17:R16

der Wert enthalten ist, der in das TCNT1 Register schrieben werden soll.

Wenn mehrere 16-bit Register nacheinander beschrieben werden sollen

und das High-Byte in allen Fällen gleich ist,

so muss das High-Byte nur einmal beschrieben werden.

16.3.1 Mehrfachnutzung des Schattenregisters

Falls mehrere 16-Bit-Register mit dem gleichen High-Byte geschrieben werden müssen,

muss das Schattenregister nur einmal geladen werden.

Jedoch muss weiterhin darauf geachtet werden, dass Interrupts nicht das Schattenregister

zwischendurch verändern, entweder indem alle freigegebenen Interruptroutinen

das Schattenregister unberührt lassen oder indem die Sequenz von Schreibzugriffen

mit abgeschalteten Interrupts (cli/sei) ausgeführt wird.

16.4 Taktquellen

Der Zähler/Zeitgeber kann durch eine interne oder durch eine externe Quelle getaktet werden.

Die Taktquelle wird mit den Taktauswahl-Bits CS12 bis CS10 im

Zähler/Zeitgeber Control Register B (TCCR1B) festgelegt.

Details zu den Taktquellen und dem Vorteiler finden sich

unter dem Kapitel „Vorteiler für Zähler/Zeitgeber0 und 1“.

16.5 Zählereinheit

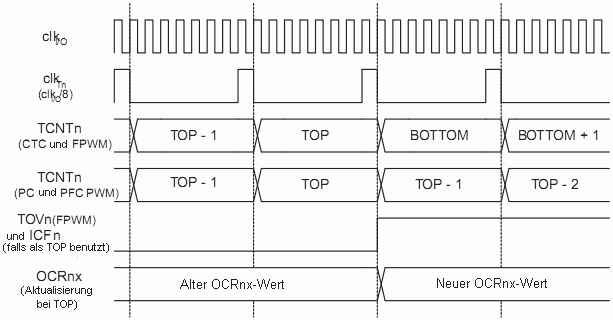

Der Hauptteil des Zähler/Zeitgeber1 ist die programmierbare 16-bit bidirektionale Zählereinheit.

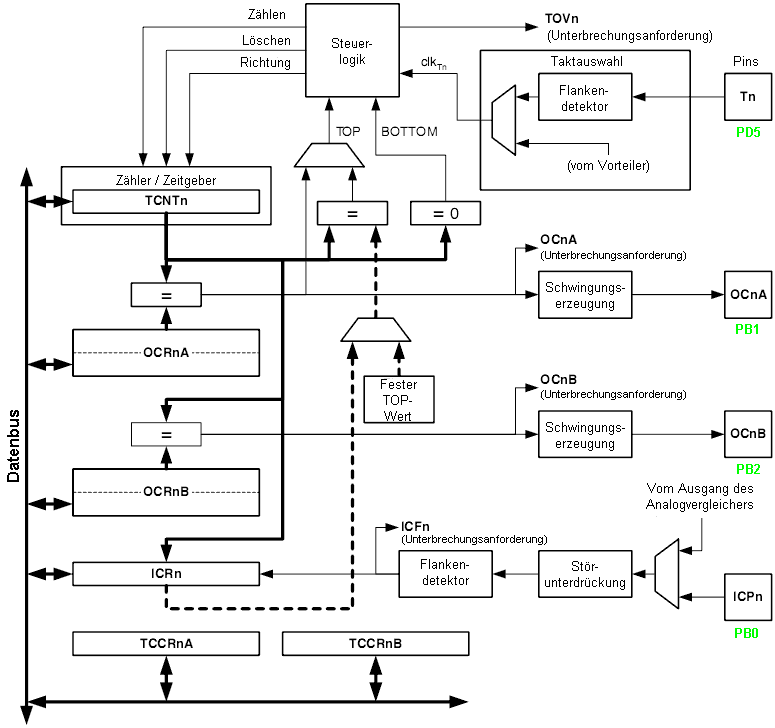

Das Blockschaltbild zeigt die Zählereinheit mit ihrer Umgebung.

Bild 16-2: Blockschaltbild des Zählers

Beschreibung der internen Signale:

| count | Inkrementiert oder dekrementiert TCNT1 um 1

|

| direction | Auswahl zwischen Inkrement und Dekrement

|

| clear | Löscht TCNT1 (alle Bits Null)

|

clkT1| Zähler/Zeitgeber-Takt

| | TOP | Signalisiert, dass TCNT1 den Maximalwert erreicht hat

| | BOTTOM | Signalisiert, dass TCNT1 den Minimalwert (Null) erreicht hat

| |

Der 16-bit Zähler ist in zwei 8-bit I/O-Speicher aufgeteilt:

Counter high (TCNT1H) enthält die oberen acht Bits des Zählers,

Counter low (TCNT1L) enthält die unteren acht Bits des Zählers.

Auf das TCNT1H Register kann die CPU nur indirekt,

nämlich über das Schattenregister TEMP zugreifen.

Das Schattenregister wird mit dem Wert von TCNT1H gefüllt,

wenn TCNT1L gelesen wird und das TCNT1H Register wird mit dem Wert

des Schattenregisters gefüllt, wenn TCNT1L geschrieben wird.

Dadurch ist es für die CPU möglich, alle 16 Bits des Zählers

innerhalb des gleichen Taktzyklus über einen 8-bit Datenbus zu verändern.

(A.d.Ü.: Der C-Compiler kann 16-Bit-Register direkt in einem Stück ansprechen,

hier über das Symbol TCNT1.)

Es ist wichtig zu wissen, dass es beim Beschreiben des TCNT1 Registers

während der Zähler läuft, spezielle Fälle gibt,

in denen das Ergebnis unvorhersehbar wird.

Diese Fälle werden an den entsprechenden Stellen erläutert.

Abhängig vom gewählten Arbeitsmodus wird der Zähler mit Takt des Timer Clock clkT1 gelöscht,

inkrementiert oder dekrementiert.

Der Takt clkT1 kann durch eine externe oder interne Quelle erzeugt werden,

die Einstellung erfolgt mit den Clock Select Bits CS12 bis CS10.

Wenn keine Taktquelle ausgewählt ist CS12 bis CS10 =000,

dann wird der Zähler gestoppt.

Auf den Wert von TCNT1 kann aber jederzeit zugegriffen werden,

unabhängig davon, ob der Takt clkT1 vorhanden ist oder nicht.

Das Beschreiben des Zählers durch die CPU hat Vorrang

vor allen Lösch- und Zähl-Operationen des Zählers.

Eine Zählsequenz wird durch die Einstellungen des Waveform Generation Mode Bits

(WGM13 bis WGM10) in den TCCR1A und TCCR1B Registern bestimmt.

Es besteht ein fester Zusammenhang zwischen der Arbeitsweise des Zählers

und der erzeugten Wellenform am Output Compare Ausgang OC1x.

Das Timer Counter Overflow Flag (TOV1) wird den Einstellungen der WGM1x Bits entsprechend gesetzt.

Es kann genutzt werden, um einen Interrupt auszulösen.

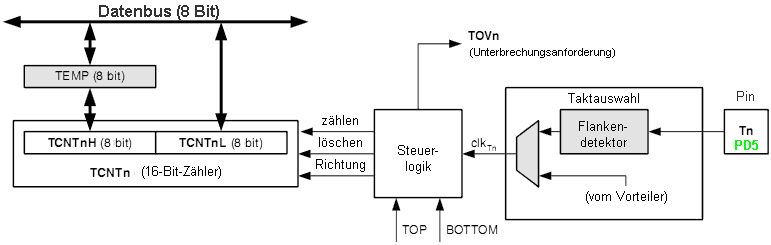

16.6 Input Capture

Der Zähler/Zeitgeber arbeitet mit einer Input Capture Einheit zusammen,

mit der externe Ereignisse erfasst und mit einem Zeitstempel versehen werden können.

Das externen Signal kennzeichnet ein oder mehrer externe Ereignisse

das über den ICP1 Pin angelegt werden kann oder alternativ

aus der Analogvergleicher Einheit stammen kann.

Der Zeitstempel kann dann genutzt werden,

um die Frequenz, das Tastverhältnis oder andere Eigenschaften

des externen Signals zu ermitteln.

Außerdem können die Zeitstempel auch verwendet werden,

um eine Aufzeichnung der eingetretenen Ereignisse zu erstellten.

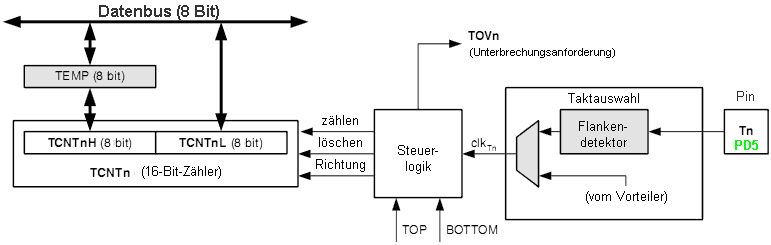

In nachfolgendem Abbild ist die Input Capture Einheit dargestellt.

Die Elemente, die nicht unmittelbar zur Input Capture Einheit gehören

sind grau schattiert.

Das „n“ in den Registern und Bitnamen steht für die Nummer des Zähler/Zeitgebers.

Bild 16-3: Blockschaltbild Input-Capture-Einheit

Wenn ein Wechsel des logischen Pegels (Ereignis) am Input Capture Pin (ICP1)

oder am Analogvergleicher Output (ACO) auftritt,

und diese Wechsel mit den Einstellungen des Flankendetektors zusammepassen,

dann wird die Erfassung getriggert.

Wenn die Erfassung getriggert wird,

wird der aktuelle 16-bit Wert des Zählers (TCNT1)

in das Input Capture Register (ICR1) geschrieben.

Das Input Capture Flag (IVF1) wird im selben Taktzyklus gesetzt,

in dem der Wert von TCNT1 in das ICR1 Register kopiert wird.

Wenn freigegeben (TICIE1=1) erzeugt das Input Capture Flag einen Interrupt.

Das ICF1 Flag wird automatisch gelöscht,

wenn die Interruptroutine ausgeführt wird.

Alternativ kann das ICF1 Flag auch dadurch gelöscht werden,

indem eine logische 1 in das Flag geschrieben wird.

Das Auslesen des 16-bit Wertes aus dem Input Capture Register (ICR1) erfolgt,

indem zunächst das Low-Byte (ICR1L) und danach das High-Byte (ICR1H) gelesen wird.

In dem Moment, in dem das Low-Byte gelesen wird,

wird das High-Byte in das Schattenregister (TEMP) kopiert.

Wenn dann das High-Byte gelesen wird,

greift die CPU auf dieses Schattenregister zu.

Das ICR1-Register kann nur beschrieben werden,

wenn ein Waveform Generation Modus benutzt wird,

der das ICR1-Register zum Festlegen des TOP-Wertes für den Zähler/Zeitgeber verwendet.

In diesem Fällen müssen die Waveform Generation Modus Bits WGM13 bis WGM10 gesetzt werden,

bevor der Wert in das ICR1-Register geschrieben werden kann.

Beim Schreiben wird zunächst das High-Byte geschrieben und im Schattenregister abgelegt.

Beim Schreiben des Low-Byte werden beiden Bytes in das ICR1-Register übernommen.

16.6.1 Triggerquelle

Die Haupt-Triggerquelle für die Input Capture Einheit ist der Input Capture Pin (ICP1).

Der Zähler/Zeitgeber 1 kann aber alternativ auch den Ausgang des Analogvergleichers verwenden,

um die Input Capture Einheit zu triggern.

Der Analogvergleicher wird das Triggerquelle ausgewählt,

indem das Analogvergleicher Input Capture Bit (ACIC) im Analogvergleicher Control und Status Register (ACSR) gesetzt wird.

Das Umschalten zwischen den Triggerquellen kann zu einer Erfassung führen.

Daher muss das Input Capture Flag nach einem Wechsel der Triggerquelle gelöscht werden.

Beide, der Input Capture Pin und der Analogvergleicher Ausgang werden mit der gleichen Technik abgetastet

wie das T1-Pin (siehe Seiten vorher).

Auch der Flankenerkenner ist identisch.

Wenn auch der Störungsunterdrücker freigeschaltet ist, wird zusätzliche Logik vor den Flankenerkenner geschaltet,

die eine zusätzliche Verzögerung von vier Takten verursacht.

Der Eingang des Störungsunterdrückers und des Flankenerkenners sind immer freigeschaltet

außer wenn der Timer/Counter in einem Waveform Generation Modus arbeitet, der ICR1 als TOP Wert für den Zähler verwendet.

Ein Erfassung kann auch durch die Software getriggert werden, indem an den Pin ICP1 der entsprechende Pegel ausgegeben wird.

16.6.2 Störunterdrückung

Der Störunterdrückung verbessert die Rauschfestigkeit durch einen einfachen digitalen Filter.

Der Eingang des Störunterdrückungs wird für vier Takte untersucht und muss in allen vier Takten gleich sein,

um den Ausgang zum Flankenerkenner zu ändern.

Der Störunterdrückung wird freigegeben, indem das Input Capture Noise Canceler Bit (ICNC1)

im Timer/Counter Control Register B (TCCR1B) gesetzt wird.

Wenn der Rauchunterdrücker freigegeben ist, erzeugt er eine zusätzliche Verzögerung

von (mindestens) vier Takten zwischen dem Auftreten des Ereignisses am Eingang

und der Übernahme des Zählerwertes in das ICR1 Register.

Die Störunterdrückung verwendet den Systemtakt und wird daher nicht durch den Vorteiler beeinflusst.

16.6.3 Anwendung des Input-Capture

Die größte Herausforderung bei der Verwendung der Input Capture Einheit liegt darin,

ausreichend Prozessorkapazität zur Verfügung zu stellen, um die eingehenden Ereignisse zu bearbeiten.

Vor allem die Zeit zwischen zwei auftretenden Ereignissen ist kritisch.

Wenn der Prozessor den erfassten Wert im ICR1 Register noch nicht gelesen hat,

bevor das nächste Ereignis auftritt, so wird das ICR1 Register mit dem neuen Wert überschrieben.

In diesem Fall wird das Ergebnis also unbrauchbar.

Wenn der Input Capture Interrupt verwendet wird, muss der Wert des ICR1 Registers

so früh wie möglich in den Interruptroutine gelesen werden.

Auch wenn der Input Capture Interrupt eine relativ hohe Priorität hat,

ist die maximale Antwortzeit von der maximalen Länge der anderen Interruptroutinen abhängig.

Es wird nicht empfohlen, die Input Capture Einheit zu verwenden,

wenn der TOP Wert aktiv während der Arbeit verändert wird.

Messungen von Pulsweiten externe Signale erfordert, dass die Flankenerkennung nach jeder Erfassung umgeschaltet wird.

Das Umschalten der Flankenrichtung muss so früh wie möglich nach dem Auslesen des ICR1 Registers erfolgen.

Nach dem Ändern der Flankenrichtung muss das Input Capture Flag (ICF1) durch die Software gelöscht werden.

Wenn nur die Frequenz des externen Signals gemessen werden soll,

so muss das ICF1 Bit nicht durch die Software gelöscht werden, wenn die entsprechende Interruptroutine verwendet wird.

16.7 Output Compare

Der 16-bit Vergleicher vergleicht kontinuierlich den Wert des TCNT1 Registers mit den Output Compare Register OCR1A und OCR1B.

Wenn die Werte von TCNT1 und OCR1x gleich sind, signalisiert der Vergleicher die Übereinstimmung.

Durch die Übereinstimmung wird das Output Compare Flag (OPCF1x) mit dem nächsten Timer Takt gesetzt.

Wenn freigegeben (OCIE1x = 1), erzeugt das Output Compare Flag einen Interrupt.

Das Flag wird automatisch gelöscht, wenn die Interruptroutine ausgeführt wird.

Es kann aber auch per Software gelöscht werden, indem eine logische 1 in das Bit geschrieben wird.

Der Waveform-Generator verwendet das Übereinstimmungssginal,

um ein Ausgangssignal entsprechend der Einstellungen der Waveform Generation Mode Bits (WGM13 bis WGM10)

und der Compate Output Mode Bits (COM1x1 bis COM 1x0) zu erzeugen.

Das TOP- und BOTTOM-Signal wird vom Waveform-Generator verwendet um die besonderen Fälle

von extremen Werten in einigen Betriebsmodi zu handhaben.

Die besonderen Eigenschaften der Output Compare Einheit A erlaubt es,

den TOP Wert (das heißt die Auflösung) des Zähler/Zeitgeber zu bestimmen.

In Zusammenhang mit der Auflösung des Zählers bestimmt der TOP Wert die Periodendauer des Ausgangssignals,

das der Waveform-Generator erzeugt.

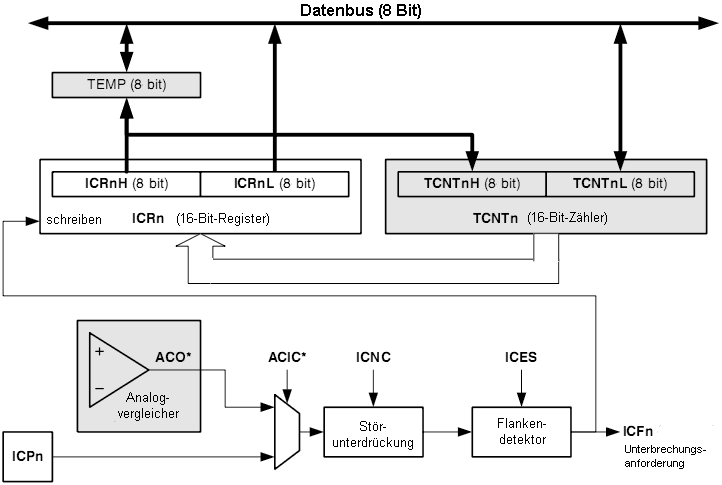

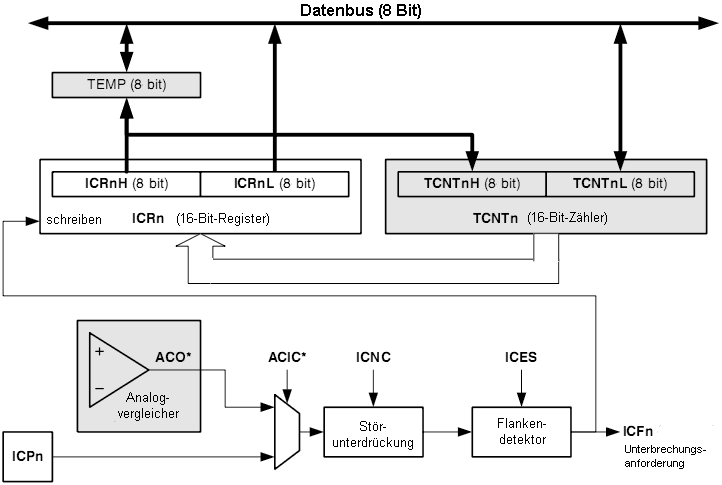

Das nachfolgende Bild zeigt das Blockschaltbild der Output Compare Einheit.

Das „n“ steht für die Nummer des Zähler/Zeitgebers (also 1), das „x“ steht für die beiden Output Compare Einheiten A und B.

Die Teile, die nicht unmittelbar zur Output Compare Einheit gehören, sind grau schattiert.

Bild 16-4: Blockschaltbild der Output-Compare-Einheit

Die OCR1x Register sind zweifach gepuffert,

wenn einer der zwölf PWM Modi verwendet wird.

Im normalen Clear Timer on Compare (CTC) Modus

ist die zweifache Bufferung ausgeschaltet.

Die zweifache Bufferung dient zur Synchronisation der laufenden Zählung

mit sich verändernden TOP und BOTTOM Werten in den Registern ORC1x.

Die Synchronisation verhindert das Auftreten von unsymmetrischen

PWM Pulsen und macht den Ausgang glitch frei.

Der Zugriff auf die OCR1x Register sieht kompliziert aus,

ist es aber nicht.

Wenn die Bufferung freigegeben ist,

dann greift die CPU auf die ORC1x-Buffer Register zu,

wenn die Bufferung ausgeschaltet ist,

dann greift die CPU direkt auf die OCR1x Register zu.

Der Inhalt der OCR1x Register kann nur durch einen Schreibbefehl geändert werden,

er wird nicht wie das TCNT1 oder das ICR1 Register automatisch

durch den Zähler aktualisiert.

Daher muss das High-Byte auch nicht über ein Schattenregister gelesen werden.

Allerdings ist es gute Praxis,

beim Zugriff auf 16-bit Register stets das Low-Byte zuerst zu lesen.

Das Schreiben der OCR1x Register erfolgt aber über das Schattenregister,

da der Vergleich aller 16 Bit kontinuierlich läuft.

Das High-Byte (OCR1xH) muss als erstes geschrieben werden

und wird dabei im Schattenregister (TEMP) abgelegt.

Wenn anschließend das Low-Byte in das OCR1xL Register geschrieben wird,

wird gleichzeitig auch der Wert aus dem TEMP Register

in das OCR1xH Register kopiert.

Der C-Compiler realisiert die 16-Bit-Zugriffe automatisch richtig

beim Ansprechen des Symbols OCR1x.

16.7.1 Output Compare erzwingen

In nicht PWM-Modi kann der Übereinstimmungsausgang des Vergleiches auch erzwungen werden,

indem man eine 1 in das Force Output-Compare-Bit FOC1x schreibt.

Bei der erzwungenen Vergleichsübereinstimmung wird weder das OCF1x-Flag gesetzt

noch der Timer gelöscht oder neu geladen.

Allerdings wird das OCP1x-Pin aktualisiert,

so als sei eine echte Vergleichsübereinstimmung aufgetreten.

Ob das OCP1x-Pin gelöscht, gesetzt oder gewechselt wird,

wird durch die Einstellungen der COM1x1- bis COM1x0-Bits festgelegt.

16.7.2 Blockade von Output Compare beim Schreiben auf TCNT1

Alle Schreibversuche der CPU in das TCNT1-Register blockieren eine Vergleichsübereinstimmung,

die im nächsten Taktzyklus auftritt, auch wenn der Timer gestoppt ist.

Dadurch ist des möglich, die OCR1x-Register mit den gleichen Werten wie das TCNT1-Register zu beschreiben,

ohne dass dadurch ein Interrupt ausgelöst wird.

16.7.3 Nutzung der Output-Compare-Einheit

Da das Beschreiben des TCNT1-Registers in jedem Modus die Vergleichsübereinstimmung für einen Timertakt blockiert,

entstehen gewisse Risiken beim Verändern von TCNT1, wenn einer der Output-Compare-Kanäle verwendet wird,

unabhängig davon, ob der Timer läuft oder nicht.

Wenn ein Wert in das TCNT1 geschrieben wird, der dem Wert eines OCR1x entspricht,

wird die Vergleichsübereinstimmung ausbleiben, wodurch eine unkorrekte Ausgangsform erzeugt wird.

Das TCNT1 sollte daher in PWM-Modi mit variablen TOP-Werten nicht mit dem TOP-Wert beschrieben werden.

Die Vergleichsübereinstimmung beim TOP-Wert würde ignoriert und der Zähler bis zum Maximalwert FFFF weiterzählen.

Umgekehrt gilt, dass TCNT1 nicht mit dem BOTTOM-Wert beschrieben werden sollte, wenn der Zähler rückwärts läuft.

Das Einstellen der OC1x Register sollte vorgenommen werden,

bevor der entsprechende Portpin als Ausgang konfiguriert wird.

Der einfachste Weg, den OC1x-Wert zu setzen, ist die Verwendung

des Force-Output-Compare-Bits (FOC1x) im normalen Modus.

Die OCR1x-Register behalten ihren Wert auch dann,

wenn zwischen den Kurvenform-Erzeugungsmodi umgeschaltet wird.

Zu beachten ist, dass die COM1x1 bis COM1x0 Bits nicht zweifach gepuffert sind.

Daher wirken sich Veränderungen dieser Bits unmittelbar aus.

16.8 Compare-Match

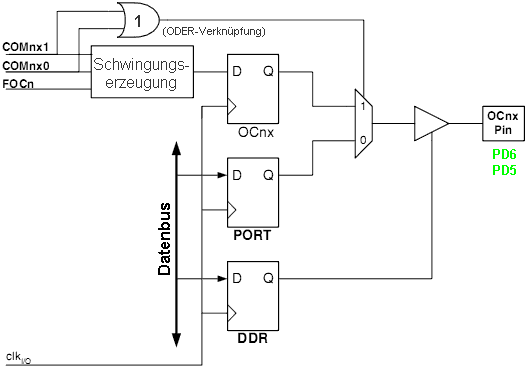

Die Compare-Output-Modusbits COM1x1 und COM1x0 haben zwei Funktionen.

Zum einen verwendet der Waveform-Generator die beiden Bits,

um den Zustand des OCR1x-Registers bei der nächsten Vergleichsübereinstimmung festzulegen.

Und zweitens kontrollieren die Bits die Ausgangsquelle des OC1x-Pins.

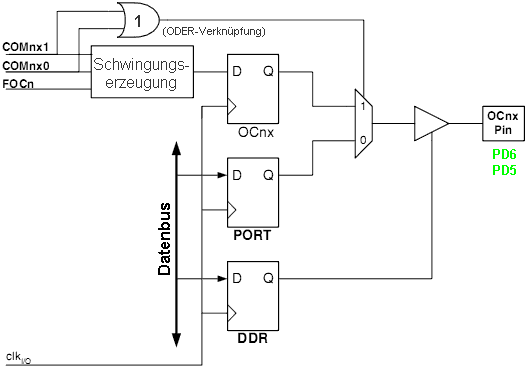

Das nachfolgende Bild zeigt das einfache Blockschaltbild der Logik,

die durch die COM1x1- und COM1x0-Bits beeinflusst wird.

Die I/O-Register, die I/O-Bits und die I/O-Pins sind fett dargestellt,

wobei von den Portkontrollregistern DDR und PORT nur der durch die Bits beeinflusste Teil dargestellt ist.

Wenn auf den Zustand des OCR1x verwiesen wird,

so ist damit das interne Register OCR1x gemeint und nicht das OC1x-Pin.

Bei einem Systemreset wird das OCR1x-Register auf 0 gesetzt.

Bild 16-5: Blockschaltbild der Compare-Match-Output-Einheit

Die allgemeine I/O Portfunktion wird durch den Output-Compare (OC1x) überschrieben,

wenn eines der beiden Bits COM1x1 oder COM1x0 gesetzt ist.

Allerdings wird die Richtung des OC1x-Pins (Eingang oder Ausgang)

nach wie vor durch durch das Datenrichtungsregister (DDR) bestimmt.

Das Richtungsbit für die OC1x-Pins (DDR_OC1x) muss als Ausgang gesetzt werden,

bevor der Wert von OC1x am Ausgang sichtbar wird.

Die überschreibende Funktion ist grundsätzlich unabhängig

von dem ausgewählten Waveform-Generator-Modus.

Allerdings gibt es einige Ausnahmen,

die in den nachfolgenden Tabellen ersichtlich sind.

Das Design der Output-Compare-Pinlogik erlaubt das Initialisieren

des OC1x-Zustandes, bevor der Ausgang freigegeben wird.

Einige COM1x1/COM1x0-Kombinationen sind für spätere Funktionen reserviert

(siehe Beschreibung der Register).

Die beiden COM1x-Bits haben keinen Einfluss auf die Input Capture Einheit.

16.8.1 Compare Output und Kurvenform-Erzeugung

Der Waveform-Generator verwendet die COM1x1 und COM1x0 Bits in den Modi normal,

CTC und PWM unterschiedlich.

In allen Fällen wird bei einer Vergleichsübereinstimmung keine Aktion ausgelöst,

wenn beide Bits auf 0 gesetzt sind.

Weitere Details in den späteren Tabellen.

16.9 Betriebsarten

Die Betriebsart, das heißt das Verhalten des Zähler/Zeitgebers und des Output Compare Pins,

wird durch die Kombination der Waveform Generation Mode Bits

(WGM13 bis WGM10) und den Compare Output Mode Bits (COM1x1 bis COM1x0) bestimmt.

Die Compare Output Mode Bits beeinflussen die Zählsequenz nicht,

die Waveform Generation Mode Bits hingegen schon.

Die COM1x1 und COM1x0 Bits legen fest, ob der PWM Ausgang invertiert sein soll oder nicht.

In nicht PWM Modi legen die COM1x1 und COM1x0 Bits fest,

ob der Ausgang gelöscht, gesetzt oder gewechselt werden soll,

wenn eine Vergleichsübereinstimmung auftritt.

16.9.1 Normalmodus

Der einfachste Betriebsmodus ist der normale Modus (WGM13 bis WGM10 = 000).

In diesem Modus zählt der Zähler immer vorwärts (inkrementieren) und wird nicht gelöscht.

Wenn der Zähler seinen maximalen Wert erreicht (FFFF) läuft er über

und beginnt erneut bei seinem BOTTOM Wert 0000.

Im normalen Modus wird das Timer Overflow Flag (TOV1) in dem Augenblick gesetzt,

in dem das TCNT1 Register wieder 0000 wird.

Das TOV1 Flag kann in diesem Fall wie ein 17 Bit betrachtet werden,

dass aber nur gesetzt und nicht automatisch gelöscht wird.

In Kombination mit dem Timer Overflow Interrupt, der das TOV1 Flag automatisch löscht,

kann also die Auflösung des Timers durch die Software erheblich erweitert werden.

Im normalen Modus sind keine Besonderheiten zu beachten,

der Wert des TCNT1 Registers kann jederzeit überschrieben werden.

Die Input Capture Einheit ist im normalen Modus einfach zu verwenden.

Es ist darauf zu achten, dass die maximale Zeit zwischen zwei externen Ereignissen

nicht außerhalb der Auflösung des Timer/Counters liegt.

Wenn dieses Intervall zu lang ist, so kann der Timer Overflow Interrupt

oder der Vorteiler verwendet werden, um die Auflösung für die Capture Einheit zu vergrößern.

Die Output Compare Einheit kann verwendet werden, um Interrupts beim jeweiligen Zählerstand zu erzeugen.

Das Erzeugen von Ausgangsfrequenzen im normal Modus wird nicht empfohlen, da dafür zu viel Prozessorkapazität verbraucht wird.

16.9.2 Verkürzter Zählzyklus

Im Clear Timer on Compare Modus (CTC) (WGM13 bis WGM10 = 4 oder 12)

werden die Register OCR1A oder ICR1 dazu verwendet, die Auflösung des Timers zu manipulieren.

Im CTC Modus wird der Zähler gelöscht, wenn der Wert des Zählers (TNCT1)

entweder mit dem des OCR1A Registers (WGM13 bis WGM10 = 4) oder dem des ICR1 Registers (WGM13 bis WGM10 = 12) übereinstimmt.

Die beiden Register OCR1A und ICR1 bestimmen also den Maximalwert des Zählers und somit seine Auflösung.

Dieser Modus erlaubt eine größere Kontrolle der Compare Match Ausgangsfrequenz.

Er vereinfacht auch das Zählen externer Ereignisse.

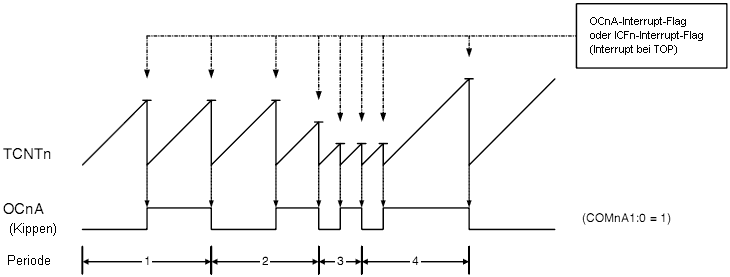

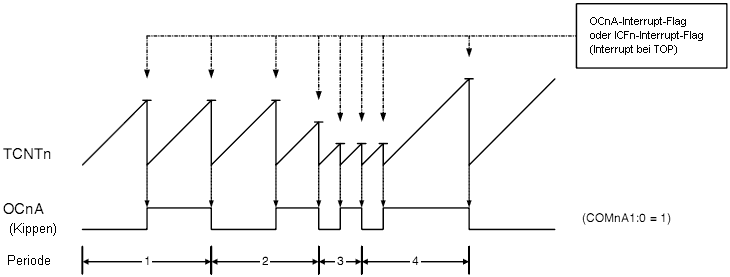

Das Zeitdiagramm des CTC Modus ist nachfolgend abgebildet.

Der Wert des Zählers (TCNT1) wächst so lange bis eine Vergleichsgleichheit mit dem OCR1A oder ICR1 auftritt,

dann wird der Zähler (TCNT1) gelöscht.

Bild 16-6: Zeitverlauf bei verkürztem Zählzyklus

Durch die Flags OCF1A oder ICF1 kann ein Interrupt generiert werden, zu jedem Zeitpunkt,

wenn der Wert des Zählers den TOP Wert erreicht, der durch das OCR1A oder ICR1 Register vorgegeben ist.

Wenn der Interrupt freigegeben ist, kann die Interruptroutine dazu verwendet werden, um den TOP Wert zu verändern.

Das Einstellen des TOP Wertes in die Nähe des BOTTOM Wertes muss mit Vorsicht geschehen,

wenn der Zähler ohne oder mit einem geringen Vorteiler betrieben wird, da der CTC Modus keine Zweifachbuffer Eigenschaft hat.

Wenn ein neuer Wert in das OCR1A oder ICR1 Register geschrieben wird,

der kleiner als der aktuelle Wert des TCNT1 ist, so wird zunächst keine Vergleichsübereinstimmung erkannt.

Der Zähler wird dann zunächst bis zu seinem maximalen Wert (FFFF) laufen und von 0000 erneut starten,

erst dann kann eine Vergleichsübereinstimmung erkannt werden.

In vielen Fällen ist dieses Verhalten nicht wünschenswert.

Eine Alternative ist dann die Verwendung des Fast PWM Modus, in dem OCR1A den TOP Wert bildet, der zweifach gebuffert ist.

Beim Generieren einer Ausgangsfrequenz im CTC Modus kann der OC1A Ausgang so eingestellt werden,

dass er seinen Zustand bei jeder Vergleichsübereinstimmung wechselt, indem die COM1A1 und COM1A0 Bits auf 1 gesetzt werden.

Der OC1A Wert wird nicht am Port Pin erscheinen, wenn die Datenrichtung nicht auf Ausgang (DDR_OC1A = 1) eingestellt ist.

Die erzeugte Ausgangswelle kann eine maximale Frequenz von fOC1A = fclk_I/O/2 haben,

wenn OCR1A auf 0000 gesetzt wird.

Allgemein wird die Ausgangsfrequenz mit folgender Gleichung bestimmt:

Die Variable N steht für den Faktor des Vorteilers (1, 8, 64, 256 oder 1024).

Im normalen Modus wird das TOV1 Flag in dem selben Taktzyklus gesetzt,

in dem der Zähler von seinem MAX Wert auf 0000 wechselt.

16.9.3 Schnelle Pulsweitenmodulation (PWM)

Der Fast PWM Modus (WGM13 bis WGM10 = 5, 6, 7, 14 oder 15) bietet eine hochfrequente Ausgangswelle.

Der Fast PWM Modus unterscheidet sich von den anderen PWM Modi durch seine einfache Impulsflanke.

Der Zähler zählt vom BOTTOM Wert bis zum TOP Wert und beginnt danach wieder mit dem BOTTOM Wert.

Im nicht invertierenden Compare Output Mode wird der Output Compare (OC1x) gesetzt,

wenn eine Vergleichsübereinstimmung zwischen dem TCNT1 und OCR1x auftritt und wird gelöscht,

wenn der TOP Wert erreicht ist.

Im invertierenden Output Compare Modus ist es genau umgekehrt.

Durch die einfache Impulsflanke kann die Frequenz im Fast PWM Modus doppelt so hoch sein

wie in den anderen PWM Modi, die mit einer doppelten Impulsflanke arbeiten.

Die hohe Frequenz des PWM Signals ist günstig bei der Verwendung als Spannungsregulierung,

Gleichrichtung und ähnlichen Digital-Analogwandler Anwendungen.

Hohe Frequenzen erlauben kleine externe Komponenten (Spulen, Kondensatoren)

wodurch die Systemkosten reduziert werden können.

Die PWM Auflösung im Fast PWM Modus kann fest eingestellt werden auf 8-, 9- oder 10-bit,

oder durch das ICR1 oder OCR1A festgelegt werden.

Die minimale Auflösung beträgt 2 Bit (ICR1 oder OCR1A auf 0003 eingestellt),

die maximale Auflösung beträgt 16 Bit (ICR1 oder OCR1A auf MAX eingestellt).

Die Auflösung der PWM in Bits kann mit folgender Formel berechnet werden:

Im Fast PWM Modus wird der Zähler so lange inkrementiert,

bis der Zähler entweder einen der festen Werte 00FFh, 01FFh oder 03FFh (WGM13 bis WGM10 = 5, 6, oder 7)

oder den Wert des ICR1 (WGM13 bis WGM10 = 14) bzw. den Wert des OCR1A (WGM13 bis WGM10 = 15) erreicht.

Der Zähler wird dann mit dem folgenden Zyklus des Timertaktes gelöscht.

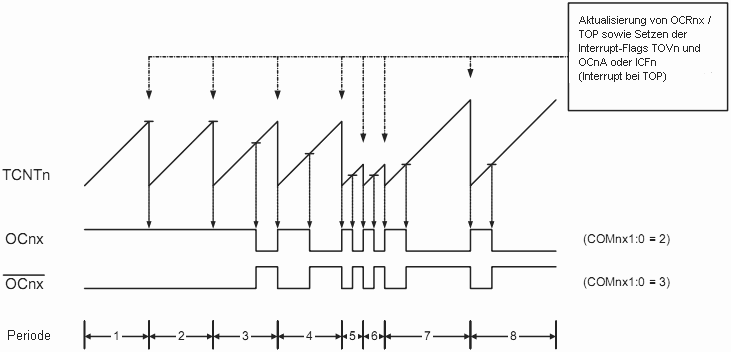

Das Zeitdiagramm des Fast PWM Modus ist im nachfolgenden Bild zu sehen.

Es zeigt den Fall, in dem ICR1 bzw.

OCR1A den TOP Wert vorgeben.

Der Wert des TCNT1 ist als Histogramm dargestellt, um die einfache Impulsflanke darzustellen.

Auch der invertierende und der nicht invertierende Ausgang sind dargestellt.

Die kleinen horizontalen Linien an der TCNT1 Flanke kennzeichnen die Vergleichsübereinstimmung zwischen OCR1x und TCNT1.

Das OC1x Interrupt Flag wird gesetzt, wenn eine Vergleichsübereinstimmung auftritt.

Bild 16-7: Zeitverlauf bei schneller Pulsweitenmodulation

Das Timer/Counter Overflow Flag (TOV1) wird jedes Mal gesetzt, wenn der Zähler seinen TOP Wert erreicht.

Zusätzlich werden auch das OCF1A bzw.

das ICF1 Flag gesetzt, wenn das OCR1A oder das ICR1 Register den TOP Wert bestimmen.

Wenn einer der Interrupts freigegeben ist, kann die Interruptroutine dazu verwendet werden,

die TOP und Vergleichswerte zu aktualisieren.

Wenn der TOP Wert geändert wird, muss das Programm sicherstellen, dass der neue TOP Wert

größer oder gleich dem Wert aller Vergleichsregister ist.

Ist der neue TOP Wert kleiner, so kann keine Vergleichsübereinstimmung zwischen TCNT1 und OCR1x auftreten.

Wenn die festen TOP Werte verwendet werden, werden die ungenutzten Bits mit 0 maskiert

wenn eines der OCR1x Register beschrieben wird.

Das Vorgehen bei der Aktualisierung des ICR1 Registers unterscheidet sich von der Aktualisierung

des OCR1A Registers, wenn diese dazu verwendet werden, den TOP Wert festzulegen.

Das ICR1 Register ist nicht zweifach gebuffert.

Das bedeutet, dass, wenn das ICR1 in einen kleinen Wert verändert wird und der Zähler mit keinem

oder einen kleinen Vorteiler betrieben wird, ein Risiko besteht,

dass der neue ICR1 Wert kleiner ist als der aktuelle Wert von TCNT1.

Das Ergebnis wird sein, dass der Zähler keine Vergleichsübereinstimmung erreicht bevor er den TOP Wert erreicht.

Der Zähler wird dann bis zum maximalen Wert FFFF laufen, überlaufen und bei 0000 neu beginnen,

bevor eine Vergleichsübereinstimmung auftritt.

Das OCR1A Register hingegen ist zweifach gebuffert.

Diese Eigenschaft erlaubt es das OCR1A Register jederzeit zu beschreiben.

Der neue Wert des OCR1A wird zunächst in das Buffer Register geschrieben

und erst mit dem Taktzyklus in das OCR1A Vergleichsregister übernommen,

der auf das Erreichen des TOP Wertes durch den TCNT1 folgt.

Die Übernahme des neuen Wertes erfolgt im gleichen Augenblick in dem das TCNT1 gelöscht und das TOV1 Flag gesetzt wird.

Das ICR1 Register für das Definieren des TOP Wertes zu verwenden ist ähnlich sinnvoll wie das Arbeiten mit den festen Werten.

Wenn das ICR1 Register für den TOP Wert verwendet wird, steht das OCR1A Register zur Verfügung,

um den PWM Ausgang an OC1A zu generieren.

Wann immer die Basisfrequenz des PWM Signals während des laufenden Betriebes verändert werden soll,

so ist es besser das OCR1A Register als TOP Wert zu verwenden, da es zweifach gebuffert ist.

Im Fast PWM Modus erlauben die Vergleichseinheiten das Erzeugen von PWM Signalen an den OC1x Pins.

Durch Setzen der COM1x1 und COM1x0 Bits auf 2 wird ein nicht invertiertes PWM-Signal erzeugt.

Ein invertiertes PWM-Signal kann erzeugt werden, indem COM1x1 und COM1x0 auf 3 gesetzt werden.

Um das PWM Signal am Port Pin sichtbar zu machen muss dieser als Ausgang konfiguriert werden (DDR_OC1X = 1).

Das PWM Signal wird erzeugt indem das OC1x Register gesetzt (gelöscht) wird,

wenn eine Vergleichsübereinstimmung zwischen OCR1x und TCNT1 besteht

und das OC1x Register in dem Taktzyklus gelöscht (gesetzt) wird, in dem der Zähler durch den Wechsel

von TOP zu BOTTOM gelöscht wird.

Die Frequenz des Ausgangssignals kann mit folgender Formel berechnet werden:

Die Variable N steht für den Faktor des Vorteilers (1, 8, 64, 256 oder 1024).

Extreme Werte der OCR1x Register stellen spezielle Fälle bei der Erzeugung des PWM Signals im Fast PWM Modus dar.

Wenn ein OCR1x Register auf den gleichen Wert wie BOTTOM (also 0000) eingestellt wird,

wird eine schmale Spitze am Ausgang erzeugt, die mit jedem TOP+1 Takt auftritt.

Das Setzen des OCR1x Registers auf den TOP Wert wird zu einem konstanten

Low- oder High-Pegel am Ausgang führen (abhängig ob invertierender oder nicht invertierender Ausgang eingestellt).

Eine Frequenz mit einem Tastverhältnis von 50% kann im Fast PWM Modus dadurch erreicht werden,

indem man OC1A so einstellt, dass es seinen Pegel bei jeder Vergleichsübereinstimmung wechselt (COM1x1 und COM1x0 Bits auf 1).

Das kann aber nur erreicht werden, wenn OCR1A zum definieren des TOP Wertes verwendet wird.

Die erzeugte Ausgangswelle kann eine maximale Frequenz von fOC1A = fclk_I/O/2 haben, wenn OCR1A auf 0000 gesetzt wird.

Diese Eigenschaft ist gleich dem OC1A Toggel im CTC Modus, mit der Ausnahme,

dass die zweifach gebufferte Output Compare Einheit im Fast PWM Modus zur Verfügung steht.

16.9.4 Phasenrichtige PWM

Der Phase Correct PWM Modus (WGM13 bis WGM10 = 1, 2, 3, 10 oder 11) bietet

eine phasenkorrekte Ausgangswelle mit hoher Auflösung.

Der Phase correct PWM Modus basiert, wie der phase an frequenzy correct PWM Modus,

auf einer zweifachen Impulsflanke.

Der Zähler zählt vom BOTTOM Wert bis zum TOP Wert und wieder zurück vom TOP zum BOTTOM Wert.

Im nicht invertierenden Compare Output Mode wird der Output Compare (OC1x) gelöscht,

wenn beim Hochzählen eine Vergleichsübereinstimmung zwischen dem TCNT1 und OCR1x auftritt

und wird gesetzt wenn beim Runterzählen eine Vergleichsübereinstimmung auftritt.

Im invertierenden Output Compare Modus ist es genau umgekehrt.

Durch die zweifache Impulsflanke ist die Frequenz im phase correct PWM Modus niedriger als in den PWM Modi, die mit einer einfachen Impulsflanke arbeiten.

Wegen der symmetrischen Eigenschaften der PWM Modi mit zweifacher Impulsflanke eigenen sich diese besonders

für die Steuerung von Motoren.

Die PWM Auflösung im Phase Correct PWM Modus kann fest eingestellt werden auf 8-, 9- oder 10-bit, oder durch das ICR1 oder OCR1A festgelegt werden.

Die minimale Auflösung beträgt 2 Bit (ICR1 oder OCR1A auf 0003 eingestellt), die maximale Auflösung beträgt 16 Bit (ICR1 oder OCR1A auf MAX eingestellt).

Die Auflösung der PWM in Bits kann mit folgender Formel berechnet werden:

Im Phase Correct PWM Modus wird der Zähler so lange inkrementiert, bis der Zähler entweder einen der festen Werte 00FF, 01FF oder 03FF (WGM13 bis WGM10 = 1, 2, oder 3) oder den Wert des ICR1 (WGM13 bis WGM10 = 10) bzw.

den Wert des OCR1A (WGM13 bis WGM10 = 11) erreicht.

Der Zähler hat dann den TOP Wert erreicht und ändert daraufhin seine Zählrichtung.

Der Wert von TCNT1 wird für einen Takt lang gleich dem ausgewählten TOP Wert sein.

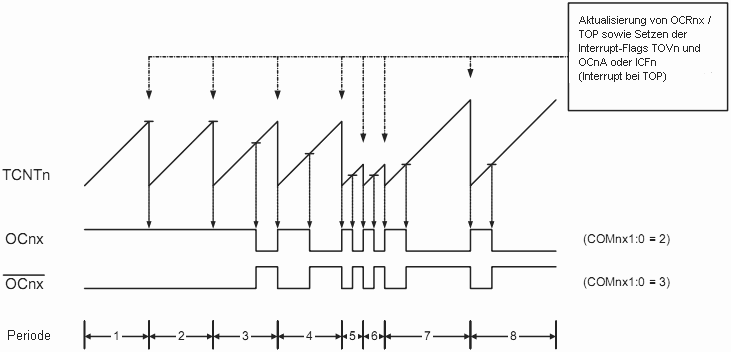

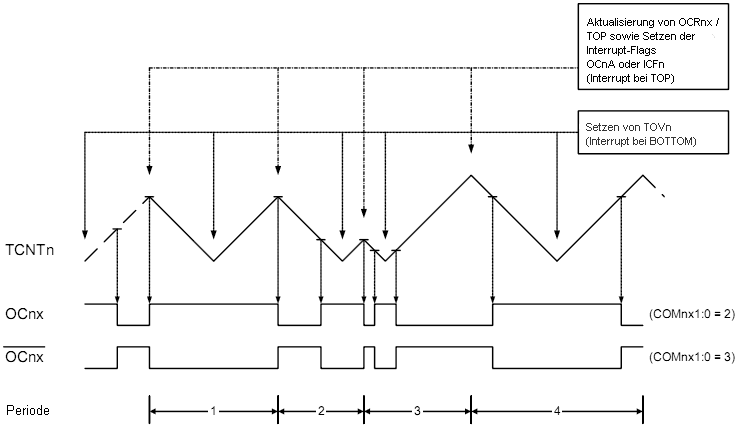

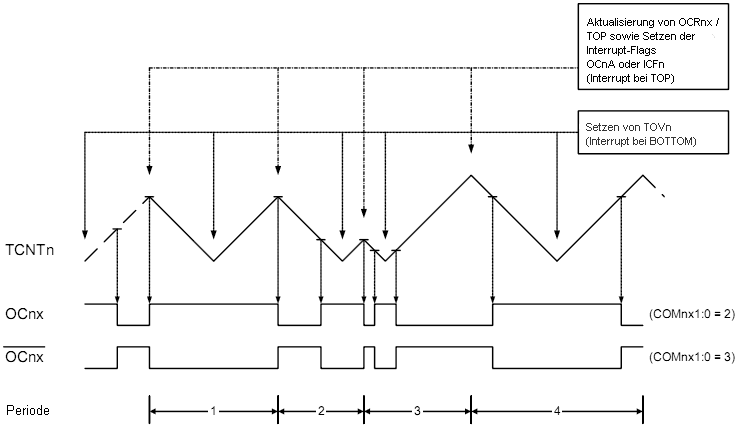

Das Zeitdiagramm des Phase Correct PWM Modus ist im nachfolgenden Bild zu sehen.

Es zeigt den Fall, in dem ICR1 bzw.

OCR1A den TOP Wert vorgeben.

Der Wert des TCNT1 ist als Histogramm dargestellt, um die zweifache Impulsflanke darzustellen.

Auch der invertierende und der nicht invertierende Ausgang sind dargestellt.

Die kleinen horizontalen Linien an der TCNT1 Flanke kennzeichnen die Vergleichsübereinstimmung zwischen OCR1x und TCNT1.

Das OC1x Interrupt Flag wird gesetzt, wenn eine Vergleichsübereinstimmung auftritt.

Bild 16-8: Zeitverlauf bei phasenrichtiger PWM

Das Timer/Counter Overflow Flag (TOV1) wird jedes Mal gesetzt, wenn der Zähler seinen BOTTOM Wert erreicht.

Wenn das OCR1A oder das ICR1 Register den TOP Wert bestimmen werden dementsprechend auch das OCF1A bzw.

das ICF1 Flag gesetzt in dem gleichen Timertakt in dem das OCR1x Register

mit dem zweifach gebufferten Wert upgedatet wird (bei TOP).

Die Interrupt Flags können genutzt werden, um einen Interrupt bei jedem Erreichen des

TOP oder BOTTOM Wertes durch den Zähler zu erzeugen.

Wenn der TOP Wert geändert wird, muss das Programm sicherstellen, dass der neue TOP Wert

größer oder gleich dem Wert aller Vergleichsregister ist.

Ist der neue TOP Wert kleiner, so kann keine Vergleichsübereinstimmung zwischen TCNT1 und OCR1x auftreten.

Wenn die festen TOP Werte verwendet werden, werden die ungenutzten Bits mit 0 maskiert

wenn eines der OCR1x Register beschrieben wird.

Wie in der dritten Periode in dem Zeitdiagramm zu sehen, kann das Verändern des TOP Wertes

während des laufenden Betriebes zu einem unsymmetrischen Ausgang führen.

Der Grund hierfür liegt in der Zeit, in der das OCR1x Register aktualisiert wird.

Weil das OCR1x Register bei Erreichen des TOP Wertes aktualisiert wird, beginnt und endet eine Periode am TOP Wert.

Das hat zur Folge, dass die Länge der fallenden Flanke durch den alten TOP Wert bestimmt wird,

während sich die Länge der steigenden Flanke aus dem neuen TOP Wert ergibt.

Wenn diese beiden Werte unterschiedlich sind unterscheidet sich auch die Länge der beiden Flanken.

Der Unterschied in der Länge führt dann zu dem unsymmetrischen Ausgangssignal.

Es wird empfohlen den Phasen und Frequenzkorrekten PWM Modus zu verwenden,

wenn der TOP Wert während des laufenden Zählers verändert werden soll.

Wenn ein fester TOP Wert verwendet wird, unterscheiden sich diese beiden Modi nicht.

Im Phase correct PWM Modus erlauben die Vergleichseinheiten das Erzeugen von PWM Signalen an den OC1x Pins.

Durch Setzen der COM1x1 und COM1x0 Bits auf 2 wird ein nicht invertiertes PWM-Signal erzeugt.

Ein invertiertes PWM-Signal kann erzeugt werden, indem COM1x1 und COM1x0 auf 3 gesetzt werden.

Um das PWM Signal am Port Pin sichtbar zu machen muss dieser als Ausgang konfiguriert werden (DDR_OC1X = 1).

Das PWM Signal wird erzeugt indem das OC1x Register gesetzt (gelöscht) wird,

wenn beim Hochzählen eine Vergleichsübereinstimmung zwischen OCR1x und TCNT1 besteht

und das OC1x Register wird gelöscht (gesetzt) wird, wenn beim Runterzählen eine Vergleichsübereinstimmung

zwischen OCR1x und TCNT1 besteht.

Die Frequenz des Ausgangssignals kann mit folgender Formel berechnet werden:

Die Variable N steht für den Faktor des Vorteilers (1, 8, 64, 256 oder 1024).

Extreme Werte der OCR1x Register stellen spezielle Fälle bei der Erzeugung des PWM Signals im Phase correct PWM Modus dar.

Wenn ein OCR1x Register auf den gleichen Wert wie BOTTOM eingestellt wird,

bleibt der Ausgang permanant auf Low-Pegel Das Setzen des OCR1x Registers auf den TOP Wert

wird zu einem konstanten High-Pegel am Ausgang führen (beim invertierenden Modus ist es dann genau anders herum).

Wenn das OCR1A verwendet wird, um den TOP Wert festzulegen (WGM13 bis WGM10 = 11) und COM1A1 und COM1A0

auf 1 sind, dann wechselt der OC1A Ausgang mit einem Tastverhältnis von 50%.

16.9.5 Phasen- und frequenzrichtige PWM

Der Phase and Frequency Correct PWM Modus (WGM13 bis WGM10 = 8 oder 9) bietet eine

phasen- und frequenzkorrekte Ausgangswelle mit hoher Auflösung.

Der Phase and Frequency correct PWM Modus basiert, wie der phase correct PWM Modus, auf einer zweifachen Impulsflanke.

Der Zähler zählt vom BOTTOM Wert (0000) bis zum TOP Wert und wieder zurück vom TOP zum BOTTOM Wert.

Im nicht invertierenden Compare Output Mode wird der Output Compare (OC1x) gelöscht,

wenn beim Hochzählen eine Vergleichsübereinstimmung zwischen dem TCNT1 und OCR1x auftritt

und wird gesetzt wenn beim Runterzählen eine Vergleichsübereinstimmung auftritt.

Im invertierenden Output Compare Modus ist es genau umgekehrt.

Durch die zweifache Impulsflanke ist die Frequenz im phase and Frequency correct PWM Modus niedriger als in den PWM Modi,

die mit einer einfachen Impulsflanke arbeiten.

Wegen der symmetrischen Eigenschaften der PWM Modi mit zweifacher Impulsflanke eigenen sich diese besonders für die

Steuerung von Motoren.

Der wesentliche Unterschied zwischen dem phasenkorrekten und dem phasen- und frequenzkorrekten

PWM Modus ist der Augenblick, in dem das OCR1x Register mit dem Wert aus dem OCR1x Buffer-Register aktualisiert wird.

Die PWM Auflösung im Phase and Frequency PWM Modus kann durch das ICR1 oder das OCR1A festgelegt werden.

Die minimale Auflösung beträgt 2 Bit (ICR1 oder OCR1A auf 0003 eingestellt), die maximale Auflösung beträgt 16 Bit (ICR1 oder OCR1A auf MAX eingestellt).

Die Auflösung der PWM in Bits kann mit folgender Formel berechnet werden:

Im Phase and Frequency Correct PWM Modus wird der Zähler so lange inkrementiert,

bis der Zähler den Wert des ICR1 (WGM13 bis WGM10 = 8) bzw.

den Wert des OCR1A (WGM13 bis WGM10 = 9) erreicht.

Der Zähler hat dann den TOP Wert erreicht und ändert daraufhin seine Zählrichtung.

Der Wert von TCNT1 wird für einen Takt lang gleich dem ausgewählten TOP Wert sein.

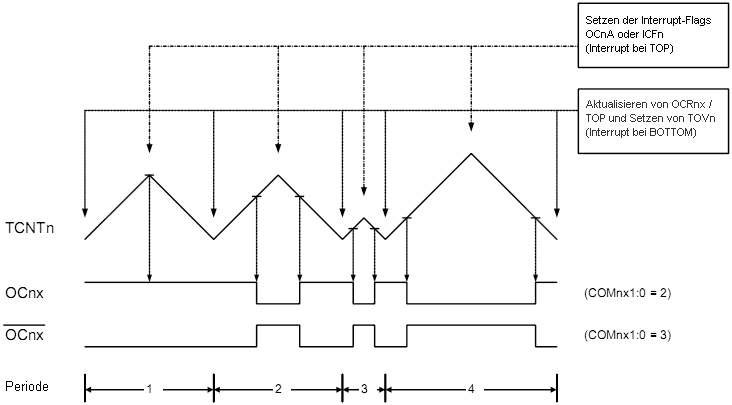

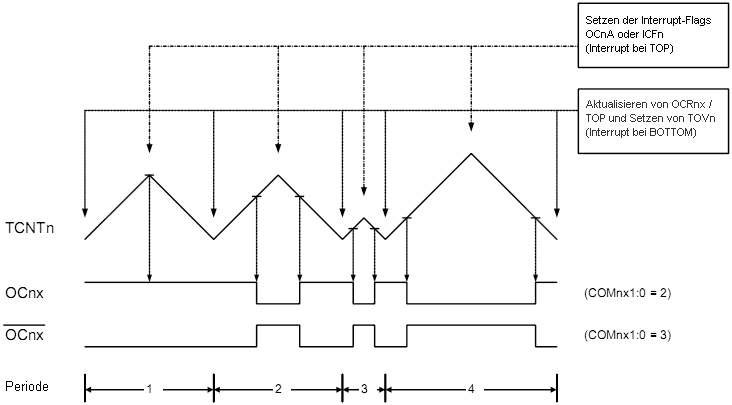

Das Zeitdiagramm des Phase and Frequency Correct PWM Modus ist im nachfolgenden Bild zu sehen.

Es zeigt den Fall, in dem ICR1 bzw.

OCR1A den TOP Wert vorgeben.

Der Wert des TCNT1 ist als Histogramm um die zweifache Impulsflanke darzustellen.

Auch der invertierende und der nicht invertierende Ausgang sind dargestellt.

Die kleinen horizontalen Linien an der TCNT1 Flanke kennzeichnen die Vergleichsübereinstimmung zwischen OCR1x und TCNT1.

Das OC1x Interrupt Flag wird gesetzt, wenn eine Vergleichsübereinstimmung auftritt.

Bild 16-9: Zeitverlauf bei phasen- und frequenzrichtiger PWM

Das Timer/Counter Overflow Flag (TOV1) wird jedes Mal gesetzt,

wenn das OCR1x Register mit dem Wert aus dem Buffer aktualisiert wird (beim BOTTOM Wert).

Wenn das OCR1A oder das ICR1 Register den TOP Wert bestimmen werden dementsprechend auch das OCF1A bzw.

das ICF1 Flag gesetzt wenn TCNT1 den TOP Wert erreicht hat.

Die Interrupt Flags können genutzt werden, um einen Interrupt

bei jedem Erreichen des TOP oder BOTTOM Wertes durch den Zähler auszulösen.

Wenn der TOP Wert geändert wird, muss das Programm sicherstellen,

dass der neue TOP Wert größer oder gleich dem Wert aller Vergleichsregister ist.

Ist der neue TOP Wert kleiner, so kann niemals eine Vergleichsübereinstimmung zwischen TCNT1 und OCR1x auftreten.

Die Abbildung zeigt, dass der Ausgang im Gegensatz zum phasenCorrecten PWM Modus in allen Perioden symmetrisch ist.

Weil das OCR1x Register aktualisiert wird, wenn BOTTOM erreicht ist,

ist die Länge der fallenden und der steigenden Impulsflanke immer gleich.

Daraus ergibt sich eine symmetrische Ausgangswelle, die immer frequenzkorrekt ist.

Das ICR1 Register für das Definieren des TOP Wertes zu verwenden ist ähnlich sinnvoll wie das Arbeiten mit den festen Werten.

Wenn das ICR1 Register für den TOP Wert verwendet wird, steht das OCR1A Register zur Verfügung,

um den PWM Ausgang an OC1A zu generieren.

Wann immer die Basisfrequenz des PWM Signals während des laufenden Betriebes verändert werden soll,

so ist es besser das OCR1A Register als TOP Wert zu verwenden, da es zweifach gebuffert ist.

Im Phase and Frequency correct PWM Modus erlauben die Vergleichseinheiten das Erzeugen von PWM Signalen an den OC1x Pins.

Durch Setzen der COM1x1 und COM1x0 Bits auf 2 wird ein nicht invertiertes PWM-Signal erzeugt.

Ein invertiertes PWM-Signal kann erzeugt werden, indem COM1x1 und COM1x0 auf 3 gesetzt werden.

Um das PWM Signal am Port Pin sichtbar zu machen muss dieser als Ausgang konfiguriert werden (DDR_OC1X = 1).

Das PWM Signal wird erzeugt indem das OC1x Register gesetzt (gelöscht) wird,

wenn beim Hochzählen eine Vergleichsübereinstimmung zwischen OCR1x und TCNT1 besteht

und das OC1x Register gelöscht (gesetzt) wird, wenn beim Runterzählen eine Vergleichsübereinstimmung

zwischen OCR1x und TCNT1 besteht.

Die Frequenz des Ausgangssignals kann mit folgender Formel berechnet werden:

Die Variable N steht für den Faktor des Vorteilers (1, 8, 64, 256 oder 1024).

Extreme Werte der OCR1x Register stellen spezielle Fälle bei der Erzeugung des PWM Signals im Phase and frequency correct PWM Modus dar.

Wenn ein OCR1x Register auf den gleichen Wert wie BOTTOM eingestellt wird, bleibt der Ausgang permanent auf Low-Pegel Das Setzen des OCR1x Registers auf den TOP Wert wird zu einem konstanten High-Pegel am Ausgang führen (beim invertierenden Modus ist es dann genau anders herum).

Wenn das OCR1A verwendet wird, um den TOP Wert festzulegen (WGM13 bis WGM10 = 9) und COM1A1 und COM1A0 auf 1 sind, dann wechselt der OC1A Ausgang mit einem Tastverhältnis von 50%.

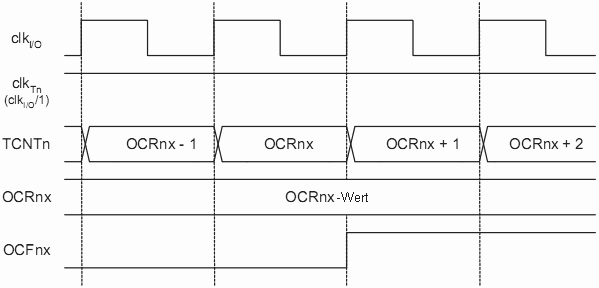

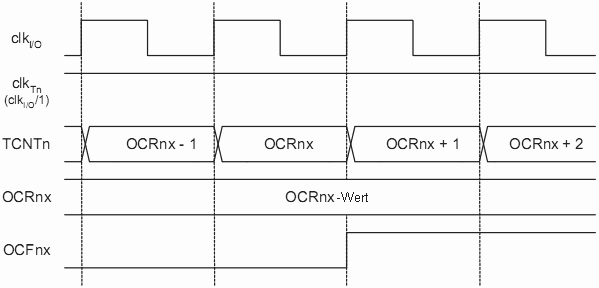

16.10 Zeitdiagramme

Der Zähler/Zeitgeber ist synchron aufgebaut,

daher ist das Taktsignal clkT1 in den folgenden Abbildungen

als ein den Takt freigebendes Signal dargestellt.

Die Abbildungen zeigen auch, wann die Interrupt Flags gesetzt werden

und die OCR1x Register mir den Werten aus dem Buffer Register

aktualisiert werden (nur in Modi, die die zweifache Bufferung verwenden).

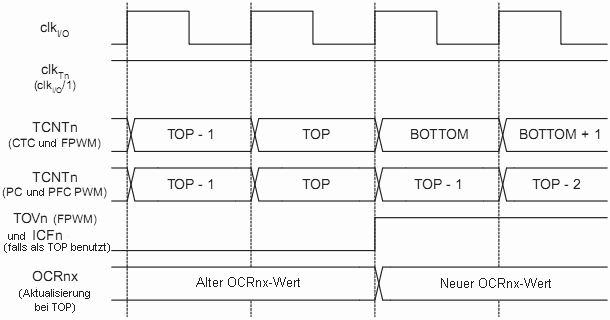

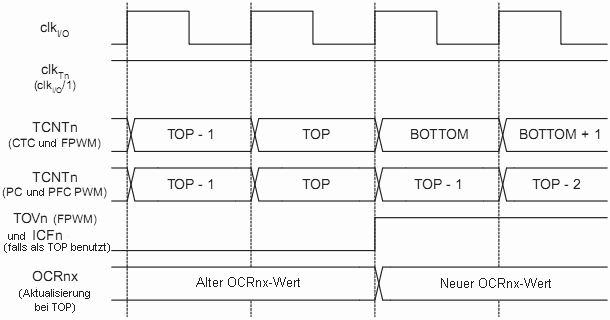

Die nachfolgende Abbildung zeigt das Setzen des OCF1x

Bild 16-10: Zeitverlauf, Setzen vom OCF1x, ohne Vorteiler

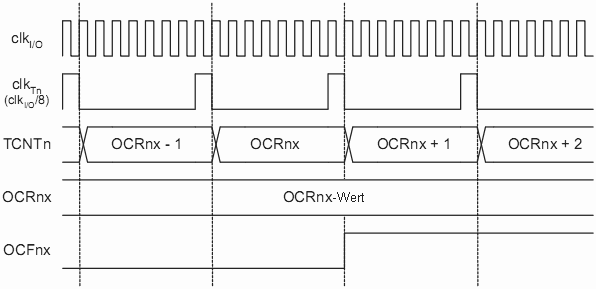

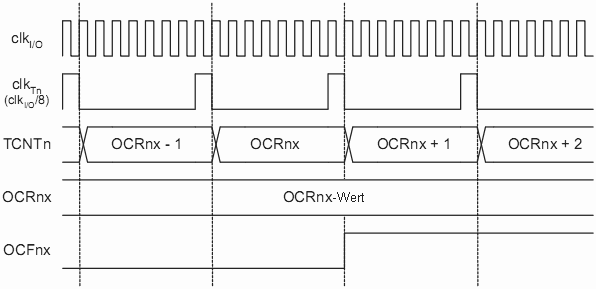

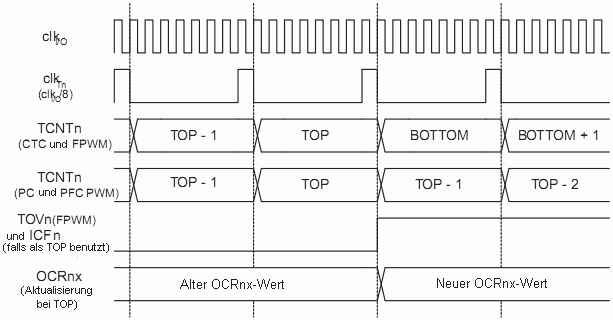

Die nachfolgende Abbildung zeigt den gleichen Vorgang, jedoch mit Vorteiler

Bild 16-11: Zeitverlauf, Setzen vom OCF1x, mit Vorteiler (fclk_I/O/8)

Die nachfolgende Abbildung zeigt eine Zählsequenz bis zum TOP Wert in verschiedenen Modi.

Wenn der phasen und frequenzkorrekte PWM Modus genutzt wird,

wird das OCR1x Register bei BOTTOM aktualisiert.

Das Zeitdiagramm ist das gleiche, allerdings muss TOP durch BOTTOM ersetzt,

TOP-1 durch BOTTOM+1 usw.

Das Umbenennen trifft auch auf die Modi zu, die das TOV1 Flag bei BOTTOM setzen.

Bild 16-12: Zeitdiagramm beim Zählerüberlauf, ohne Vorteiler

Die nachfolgende Abbildung zeigt den gleichen Vorgang, jedoch mit Vorteiler

Bild 16-13: Zeitdiagramm beim Zählerüberlauf, mit Vorteiler (fclk_I/O/8)

16.11 Register-Beschreibung

16.11.1 TCCR1A — Kontrollregister A

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x80) | COM1A1 | COM1A0 | COM1B1 | COM1B0 | - | - | WGM11 | WGM10 | TCCR1A

|

|---|

| Zugriff | R/W | R/W | R/W | R/W | R | R | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

- Bit 7 und 6 – COM1A1 und COM1A0: Compare Output Mode für Kanal A

- Bit 5 und 4 – COM1B1 und COM1B0: Compare Output Mode für Kanal B

Die beiden Bits COM1A1/COM1A0 sowie COM1B1/COM1B0 kontrollieren das Verhalten der beiden Output Compare Pins OC1A und OC1B.

Wenn eines der beiden Bits gesetzt ist, überlagert das OC1x-Signal die normale I/O-Funktion des Pins.

Im Data Direction Register (DDR) müssen die entsprechenden Bits für OC1A bzw.

OC1B so gesetzt sein, dass die Pins als Ausgang konfiguriert sind.

Wenn OC1A oder OC1B als Ausgangsfunktion verwendet werden,

ist deren Funktion von den Einstellungen der WGM-Bits abhängig.

Nachfolgende Tabelle zeigt die Funktionen der COM1nx-Bits,

wenn die WGM-Bits auf den normalen oder den CTC-Modus eingestellt sind.

Tabelle 16-1: Aktion bei Output Compare in Nicht-PWM-Betriebsarten

| COM1A1/COM1B1 | COM1A0/COM1B0 | Funktion

|

|---|

| 0 | 0 | Normale Portfunktion, OC1A/OC1B abgeschaltet

|

| 0 | 1 | Wechsel an OC1A/OC1B bei Compare Match

|

| 1 | 0 | Löschen von OC1A/OC1B bei Compare Match (Low-Pegel)

|

| 1 | 1 | Setzen von OC1A/OC1B bei Compare Match (High-Pegel)

|

Tabelle 16-2: Aktion bei Output Compare bei schneller PWM(1)

| COM1A1/COM1B1 | COM1A0/COM1B0 | Funktion

|

|---|

| 0 | 0 | Normale Portfunktion, OC1A/OC1B abgeschaltet

|

| 0 | 1 | WGM = 15: Wechsel an OC1A bei Compare Match, OC1B abgeschaltet (Normale Portfunktion)

|

| 1 | 0 | Löschen von OC1A/OC1B bei Compare Match, Setzen von OC1A/OC1B bei TOP

|

| 1 | 1 | Setzen von OC1A/OC1B bei Compare Match, Löschen von OC1A/OC1B bei TOP

|

- Hinweis:

- Ein Sonderfall tritt ein wenn OCR1A/OCR1B gleich TOP und COM1A1/COM1B1 gesetzt.

In diesem Fall wird das Compare-Match-Ereignis ignoriert, jedoch das Löschen oder Setzen auf BOTTOM vollzogen.

Siehe oben für Details.

Tabelle 16-3: Aktion bei Output Compare bei phasen- und/oder frequenzrichtiger PWM(1)

| COM1A1/COM1B1 | COM1A0/COM1B0 | Funktion

|

|---|

| 0 | 0 | Normale Portfunktion, OC1A/OC1B abgeschaltet

|

| 0 | 1 | WGM = 9 oder 14: Wechsel an OC1A bei Compare Match, OC1B abgeschaltet (Normale Portfunktion)

|

| 1 | 0 | Löschen von OC1A/OC1B bei Compare Match beim Hochzählen, Setzen von OC1A/OC1B bei Compare Match beim Runterzählen

|

| 1 | 1 | Setzen von OC1A/OC1B bei Compare Match beim Hochzählen, Löschen von OC1A/OC1B bei Compare Match beim Runterzählen

|

- Hinweis:

- Ein Sonderfall tritt ein wenn OCR1A/OCR1B gleich TOP und COM1A1/COM1B1 gesetzt.

Siehe oben für Details.

- Bit 1 und 0 – WGM11 und WGM10: Waveform Generation Mode

Diese Bits sind in Kombination mit den WGM-Bits, die im TCCR1B-Register zu finden sind, zu verwenden.

Die WGM-Bits kontrollieren die Zählsequenz des Zählers, die Quelle für den Maximalwert (TOP)

des Zählers und die Art der generierten Ausgangswelle.

Die vom Zähler/Zeitgeber 1 unterstützend Arbeitsmodi sind: Normal,

Verkürzter Zählumfang (CTC) und drei verschiedene PWM-Modi.

Tabelle 16-4: Bit-Beschreibung zur Art der Schwingungserzeugung(1)

| Modus | WGM13 | WGM12 | WGM11

(CTC1)

(PWM11) | WGM10

(PWM10) | PWM-Betriebsart | TOP | Wann Aktualisierung von OCR1x? | Wann TOV-Flag gesetzt?

|

|---|

| 0 | 0 | 0 | 0 | 0 | Normal | 0xFF | sofort | MAX

|

| 1 | 0 | 0 | 0 | 1 | Phasenrichtige PWM 8 Bit | 0x00FF | TOP | BOTTOM

|

| 2 | 0 | 0 | 1 | 0 | Phasenrichtige PWM 9 Bit | 0x01FF

|

| 3 | 0 | 0 | 1 | 1 | Phasenrichtige PWM 10 Bit | 0x03FF

|

| 4 | 0 | 1 | 0 | 0 | Verkürzter Zählumfang | OCR1A | sofort | MAX

|

| 5 | 0 | 1 | 0 | 1 | Schnelle PWM 8 Bit | 0x00FF | BOTTOM | TOP

|

| 6 | 0 | 1 | 1 | 0 | Schnelle PWM 9 Bit | 0x01FF

|

| 7 | 0 | 1 | 1 | 1 | Schnelle PWM 10 Bit | 0x03FF

|

| 8 | 1 | 0 | 0 | 0 | Phasen- und frequenzrichtige PWM | ICR1 | BOTTOM | BOTTOM

|

| 9 | 1 | 0 | 0 | 1 | OCR1A

|

| 10 | 1 | 0 | 1 | 0 | Phasenrichtige PWM | ICR1 | TOP | BOTTOM

|

| 11 | 1 | 0 | 1 | 1 | OCR1A

|

| 12 | 1 | 1 | 0 | 0 | Verkürzter Zählumfang | ICR1 | sofort | MAX

|

| 13 | 1 | 1 | 0 | 1 | reserviert | - | - | -

|

| 14 | 1 | 1 | 1 | 0 | Schnelle PWM | ICR1 | BOTTOM | TOP

|

| 15 | 1 | 1 | 1 | 1 | OCR1A

|

- Hinweis:

- Die Bitnamen CTC1 und PWM[1:0] sind obsolet

und zum Erhalt der Kompatibilität zu älterem Quellkode.

In neuer Software sollten die neuen Bitnamen WGM1[3:0] benutzt werden.

16.11.2 TCCR1B — Kontrollregister B

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x81) | ICIC1 | ICES1 | - | WGM13 | WGM12 | CS12 | CS11 | CS10 | TCCR1B

|

|---|

| Zugriff | R/W | R/W | R | R/W | R/W | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

- Bit 7 – ICNC1: Störunterdrückung für Input-Capture

Wenn dieses Bit gesetzt ist, ist die Störunterdrückung aktiviert.

Wenn die Störunterdrückung aktiviert ist, wird der Eingang des Input-Capture-Pins gefiltert.

Die Filterfunktion erfordert vier erfolgreiche gleiche Wertabtastungen des ICP1-Pins, um seinen Ausgang zu ändern.

Der Input-Capture ist daher um vier Takte verzögert, wenn der Störunterdrückung freigegeben ist.

- Bit 6 – ICES1: Flankenauswahl für Input-Capture

Dieses Bit bestimmt, welche Flanke am Input-Capture-Pin ICP1 notwendig ist, um ein Capture Ereignis zu triggern.

Wenn das ICES1 Bit auf 0 gesetzt wird, wird eine negative/fallende Flanke als Trigger verwendet,

wenn das ICES1 Bit auf 1 gesetzt ist, wird eine positive/steigende Flanke als Trigger verwendet.

Wenn ein Trigger entsprechend der Einstellung des Bits erfolgt,

wird der Wert des Zählers in das Input-Capture-Register ICR1 kopiert.

Das Ereignis setzt ebenfalls das Input-Capture-Flag ICF1, das verwendet werden kann,

um einen Interrupt auszulösen, wenn dieser freigegeben ist.

Wenn das ICR1-Register als TOP-Wert (siehe WGM-Bits) verwendet wird,

ist der ICP1-Pin abgeschaltet und somit die Input-Capture-Funktion gesperrt.

- Bit 5 – Res: Reserviertes Bit

Dieses Bit ist reserviert und wird immer als 0 gelesen.

Um die Kompatibilität mit zukünftigen Bausteinen sicherzustellen,

sollte das Bit immer mit 0 beschrieben werden, wenn das TCCR1B Register beschrieben wird.

- Bit 4:3 – WGM1[3:2]: Betriebsart der Schwingungserzeugung

Siehe Beschreibung des Registers TCCR1A.

- Bit 2:0 – CS1[2:0]: Taktauswahl

Diese Bits bestimmen die Vorteilerquelle für Zähler/Zeitgeber 1,

siehe Bild 16-10 und Bild 16-11.

Tabelle 16-5: Taktauswahl-Bitbeschreibung

| CS12 | CS11 | CS10 | Beschreibung

|

|---|

| 0 | 0 | 0 | Zähler/Zeitgeber 1 ist gestoppt

|

| 0 | 0 | 1 | clkI/O/1 (kein Vorteiler)

|

| 0 | 1 | 0 | clkI/O/8 (mit Vorteiler)

|

| 0 | 1 | 1 | clkI/O/64 (mit Vorteiler)

|

| 1 | 0 | 0 | clkI/O/256 (mit Vorteiler)

|

| 1 | 0 | 1 | clkI/O/1024 (mit Vorteiler)

|

| 1 | 1 | 0 | Externe Quelle am T1 Pin, fallende Flanke

|

| 1 | 1 | 1 | Externe Quelle am T1 Pin, steigende Flanke

|

Wenn eine externe Quelle zum Takten des Zähler/Zeitgeber 1 verwendet wird, so funktioniert die Taktung auch,

wenn der Pin als Ausgang konfiguriert ist.

Damit ist es möglich die Zählfunktion per Software zu steuern.

16.11.3 TCCR1C — Kontrollregister C

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x82) | FOC1A | FOC1B | - | - | - | - | - | - | TCCR1C

|

|---|

| Zugriff | R/W | R/W | R | R | R | R | R | R

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

- Bit 7 – FOC1A: Erzwinge Output-Compare für OC1A

- Bit 6 – FOC1B: Erzwinge Output-Compare für OC1B

Die beiden Bits FOC1A und FOC1B sind nur aktiv, wenn die WGM-Bits einen Nicht-PWM-Modus auswählen.

Um die Kompatibilität mit zukünftigen Bausteinen sicherzustellen,

müssen diese Bits auf 0 gesetzt werden, wenn der Zähler in einem PWM-Modus betrieben wird.

Wenn eine logische 1 in die FOC1A- bzw. FOC1B-Bits geschrieben wird, wird unmittelbar ein Compare-Match erzwungen.

Die OC1A- bzw. OC1B-Ausgänge ändern sich dann den Einstellungen der COM-Bits entsprechend.

Zu beachten ist, dass die FOC-Bits im Sinne von Freigabebits implementiert sind,

so dass das Verhalten beim erzwungenen Compare-Match durch die COM-Bits bestimmt wird.

Ein erzwungener Compare-Match generiert keine Interrupts und löscht den Timer nicht.

Die FOC-Bits werden immer als 0 gelesen.

16.11.4 TCNT1 — Zählregister

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x85) | TCNT1[15:8] | TCNT1H

|

|---|

| (0x84) | TCNT1[7:0] | TCNT1L

|

|---|

| Zugriff | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

Die beiden I/O-Register TCNT1H und TCNT1L,

die zusammen den Zähler/Zeitgeber 1 TCNT1 darstellen,

geben einen direkten Zugriff auf den 16-bit-Zähler bei Lese- und Schreiboparationen.

Um sicherzustellen, dass das Low- und High-Byte zeitgleich gelesen und geschrieben werden,

wenn die CPU darauf zugreift, wird für das High-Byte ein Schattenregister (TEMP) verwendet.

Dieses Schattenregister wird auch von den anderen 16-bit-Registern verwendet.

Ein Verändern des Zählers (TCNT1) während der Zähler läuft, führt zu dem Risiko,

dass ein Compare-Match zwischen TCNT1 und den OCR1x-Registern ausgelassen wird.

Beim Schreiben in das TCNT1-Register werden die Compare-Match im nächsten Takt bei allen Vergleichseinheiten blockiert.

16.11.5 OCR1A — Vergleichsregister A

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x89) | OCR1A[15:8] | OCR1AH

|

|---|

| (0x88) | OCR1A[7:0] | OCR1AL

|

|---|

| Zugriff | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

Der Wert in OCR1A wird ständig mit dem Zählregister TCNT1 verglichen.

Bei Gleichheit kann ein Compare-Match-Interrupt ausgelöst

und/oder ein Signalverlauf am OC1A-Pin generiert werden.

16.11.6 OCR1B — Vergleichsregister B

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x8B) | OCR1B[15:8] | OCR1BH

|

|---|

| (0x8A) | OCR1B[7:0] | OCR1BL

|

|---|

| Zugriff | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

Die Output Compare Register enthalten einen 16-bit Wert, der permanent mit dem Wert des Zählers (TCNT1) verglichen wird.

Eine Übereinstimmung kann dazu genutzt werden, einen Interrupt auszulösen oder eine Ausgangswelle am OC1x Pin zu erzeugen.

Die Output Compare Register sind 16-bit breit.

Um sicherzustellen, dass das Low- und High-Byte zeitgleich gelesen und geschrieben werden, wenn die CPU darauf zugreift,

wird für das High-Byte ein Schattenregister (TEMP) verwendet.

Dieses Schattenregister wird auch von den anderen 16-bit Registern verwendet.

16.11.7 ICR1 — Input-Capture-Register

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x87) | ICR1[15:8] | ICR1H

|

|---|

| (0x86) | ICR1[7:0] | ICR1L

|

|---|

| Zugriff | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

Das Input Capture Register wird immer dann mit dem Wert des Zählers aktualisiert,

wenn ein Ereignis am ICP1 Pin oder am Ausgang des Analogvergleichers auftritt.

Das Input Capture Register kann auch verwendet werden, um den TOP Wert für den Zähler festzulegen.

Das Input Capture Register ist 16-bit breit.

Um sicherzustellen, dass das Low- und High-Byte zeitgleich gelesen und geschrieben werden,

wenn die CPU darauf zugreift, wird für das High-Byte ein Schattenregister (TEMP) verwendet.

Dieses Schattenregister wird auch von den anderen 16-bit Registern verwendet.

Siehe 16-Bit-Registerzugriff.

16.11.8 TIMSK1 — Interrupt-Maske

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x6F) | - | - | ICIE1 | - | - | OCIE1B | OCIE1A | TOIE1 | TIMSK1

|

|---|

| Zugriff | R | R | R/W | R | R | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

Diese Bits sind reserviert und werden immer als 0 gelesen.

- Bit 5 – TICIE1: Zähler/Zeitgeber 1 Interruptfreigabe für Input-Capture

Wenn das TICIE1-Bit gesetzt ist und das I-Bit in Status-Register (SREG) ebenfalls gesetzt ist,

ist der Zähler/Zeitgeber 1 Input Capture Interrupt freigegeben.

Die dazugehörige Interrupt-Routine wird ausgeführt, wenn das ICF1-Bit im TIFR1-Register gesetzt wird.

- Bit 2 – OCIE1B: Zähler/Zeitgeber 1 Interruptfreigabe für Output-Compare B

Wenn das OCIE1B-Bit gesetzt ist und das I-Bit in Status-Register (SREG) ebenfalls gesetzt ist,

ist der Zähler/Zeitgeber 1 Output Compare B Match Interrupt freigegeben.

Die dazugehörige Interrupt-Routine wird ausgeführt, wenn das OCF1B-Bit im TIFR1-Register gesetzt wird.

- Bit 1 – OCIE1A: Zähler/Zeitgeber 1 Interruptfreigabe für Output-Compare A

Wenn das OCIE1A-Bit gesetzt ist und das I-Bit in Status-Register (SREG) ebenfalls gesetzt ist,

ist der Zähler/Zeitgeber 1 Output Compare A Match Interrupt freigegeben.

Die dazugehörige Interrupt-Routine wird ausgeführt, wenn das OCF1A-Bit im TIFR1-Register gesetzt wird.

- Bit 0 – TOIE1: Zähler/Zeitgeber 1 Interruptfreigabe für Zählerüberlauf

Wenn das TOIE1-Bit gesetzt ist und das I-Bit in Status-Register (SREG) ebenfalls gesetzt ist,

ist der Zähler/Zeitgeber 1 Overflow Interrupt freigegeben.

Die dazugehörige Interrupt-Routine wird ausgeführt, wenn ein Überlauf im Zähler/Zeitgeber 1 aufgetreten ist

und somit das TOV1-Bit im TIFR1-Register gesetzt wird.

16.11.9 TIFR1 — Interrupt-Flags

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x36) | - | - | ICF1 | - | - | OCF1B | OCF1A | TOV1 | TIFR1

|

|---|

| Zugriff | R | R | R/W | R | R | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

Diese Bits sind reserviert und werden immer als 0 gelesen.

- Bit 5 – ICF1: Zähler/Zeitgeber 1 Flagge für Input-Capture

Das ICF1-Bit wird gesetzt, wenn ein Capture-Ereignis am ICP1-Pin auftritt.

Wenn das ICR1-Register für den TOP-Wert des Zählers verwendet wird, wird das ICF1-Flag immer dann gesetzt,

wenn der Zähler den TOP-Wert erreicht.

Das Bit wird automatisch gelöscht, wenn die dazugehörige Interrupt-Routine ausgeführt wird.

Alternativ kann das Flag gelöscht werden, in dem man eine logische „1“ in das Flag schreibt.

- Bit 2 – OCF1B: Zähler/Zeitgeber 1 Flagge für Output-Compare B

Das OCF1B-Bit wird in dem Taktzyklus gesetzt, nachdem der Zähler TCNT1 den Wert des

Output-Compare-Register B (OCR1B) erreicht hat.

Ein erzwungener Output-Compare (FOC1B) setzt das OCF1B-Flag hingegen nicht.

Das Bit wird automatisch gelöscht, wenn die dazugehörige Interrupt-Routine ausgeführt wird.

Alternativ kann das Flag gelöscht werden, in dem man eine logische „1“ in das Flag schreibt.

- Bit 1 – OCF1A: Zähler/Zeitgeber 1 Flagge für Output-Compare A

Das OCF1A-Bit wird in dem Taktzyklus gesetzt, nachdem der Zähler TCNT1 den Wert des

Output-Compare-Register A (OCR1A) erreicht hat.

Ein erzwungener Output-Compare (FOC1A) setzt das OCF1A-Flag hingegen nicht.

Das Bit wird automatisch gelöscht, wenn die dazugehörige Interrupt-Routine ausgeführt wird.

Alternativ kann das Flag gelöscht werden, in dem man eine logische „1“ in das Flag schreibt.

- Bit 0 – TOV1: Zähler/Zeitgeber 1 Flagge für Überlauf

Das Setzen dieses Flags ist abhängig von den Einstellungen der WGM-Bits.

Im normalen und im verkürzten Zählumfang wird das TOV1-Bit gesetzt,

wenn ein Überlauf in Zähler/Zeitgeber 1 auftritt;

im Fall des verkürzten Zählumfangs bei Überlauf jenseits des Vergleichswertes.

Siehe Tabellen auf den Seiten zuvor für das Verhalten des Flags in den anderen Fällen.

Das Bit wird automatisch gelöscht, wenn die dazugehörige Interrupt-Routine ausgeführt wird.

Alternativ kann das Flag gelöscht werden, in dem man eine logische „1“ in das Flag schreibt.