15. 8-bit Zähler/Zeitgeber 0 mit PWM

15.1 Features

- Zwei unabhängige Output-Compare-Einheiten

- Doppelt gepuffertes Output-Compare-Register

- Verkürzter Zählzyklus bei Vergleichstreffer (CTC-Modus)

- Glitchfreier phasenkorrekter Pulsweitenmodulator (PWM)

- Einstellbare PWM-Periodendauer

- Frequenzgenerator

- Drei unabhängige Interruptquellen (TOV0, OCF0A und OCF0B)

15.2 Übersicht

Der Zähler/Zeitgeber0 ist ein allgemeines, 8-bit-Zähler/Zeitgeber-Modul mit zwei Output-Compare-Einheiten und PWM-Unterstützung.

Das erlaubt genaues Messen von Programmlaufzeiten (zum Ereignismanagement) und Schwingungserzeugung.

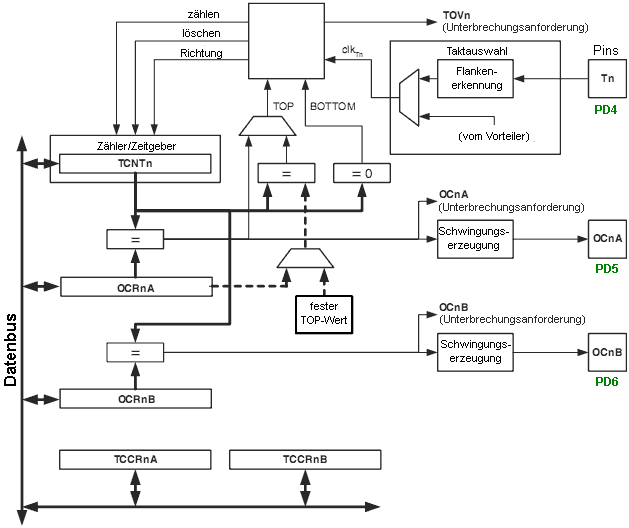

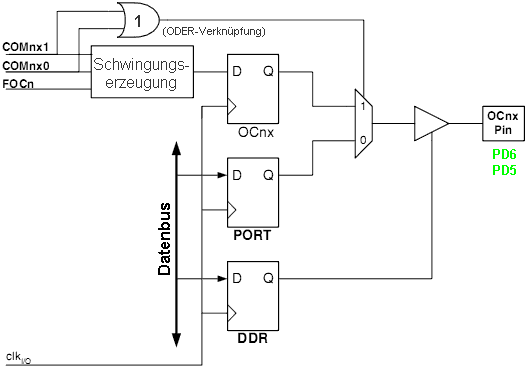

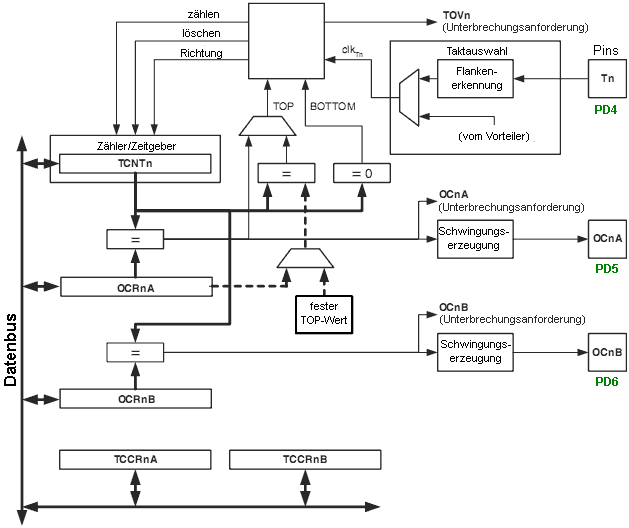

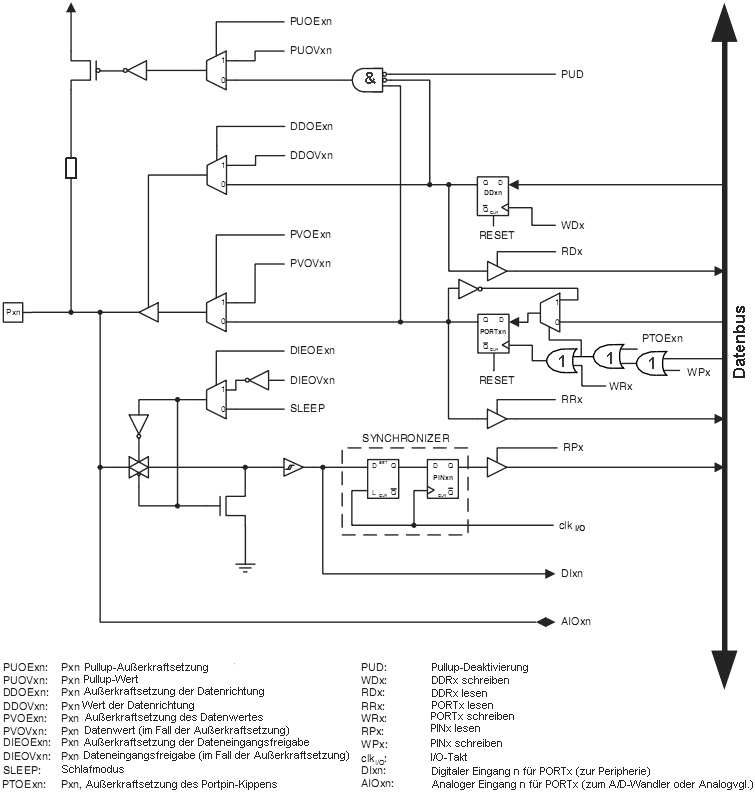

Ein einfaches Blockschaltbild des 8-bit-Zähler/Zeitgeber ist nachfolgend dargestellt.

Die Platzierung der Anschlüsse muss im Bild 1-1 nachgesehen werden.

Register, die durch die CPU erreichbar sind, sind fett dargestellt.

Die chipspezifischen I/O-Register sind unter Register-Beschreibung aufgeführt.

Das PRTIM0-Bit im Register zur Leistungsreduktion muss Null sein,

damit der Zähler/Zeitgeber 0 freigegeben ist.

Bild 15-1: Blockschaltbild 8 Bit Timer

15.2.1 Definitionen

Viele Register und Bits in diesem Dokument werden allgemein beschrieben.

Der Index n steht für die Nummer des Zähler/Zeitgeber, in diesem Fall also für eine 0.

Ein kleines x steht für eine Output-Compare-Einheit, hier demnach A oder B.

In einem Programm müssen immer die präzisen Bezeichnungen angegeben werden,

also z.B.

TCNT0 um auf den Wert des Zähler/Zeitgeber 0 zuzugreifen.

Definitionen für Zählendwerte sind in der folgenden Tabelle dargestellt:

Tabelle 15-1: Definitionen

| BOTTOM

| Der Zähler erreicht BOTTOM, wenn er 0x00 wird.

|

| MAX

| Der Zähler erreicht sein MAXimum, wenn er 0xFF (255 dezimal) wird.

|

| TOP

| Der Zähler erreicht TOP, wenn er den höchsten Wert der Zählsequenz erreicht.

Er kann fest 0xFF (= MAX) oder einstellbar im Register OCR0A sein.

Die Zuweisung hängt von der Betriebsart ab.

|

15.2.2 Register

Das Zählregister TCNT0 und die Output-Compare-Register OCR0A und OCR0B sind 8 Bit breit.

Das Signal zur Interruptanforderung wird im Zeitgeber-Interrupt-Flagregister TFIR sichtbar.

Alle Interrupts können individuell im Zeitgeber-Interrupt-Maskenregister TIMSK ausgeblendet werden.

Die Register TIFR0 und TIMSK0 sind in obigen Abbild nicht eingezeichnet.

Der Zähler/Zeitgeber0 kann intern, über einen Vorteiler oder durch eine externe Taktquelle am T0-Pin getaktet werden.

Die Taktauswahl-Logik gibt vor, durch welchen Takt und mit welcher Flanke der Timer seinen Wert

inkrementiert (oder dekrementiert).

Der Zähler/Zeitgeber ist inaktiv, wenn keine Taktquelle ausgewählt wurde.

Der Ausgang der Taktauswahl-Logik wird als Zähltakt clkT0 bezeichnet.

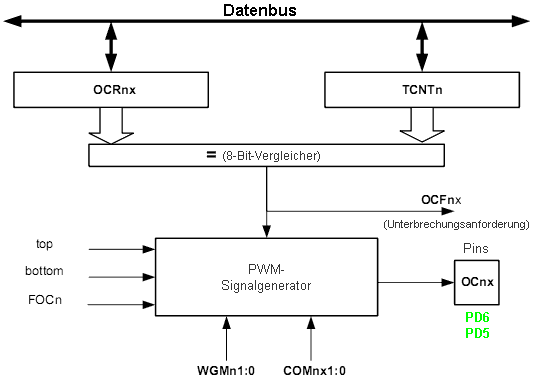

Die zweifach gepufferten Output-Compare-Register OCR0A und OCR0B werden ständig

mit dem Zählregister TCNT0 (auf Gleichheit) verglichen.

Das Vergleichsergebnis kann den Schwingungsgeneratoren zur Frequenz- und/oder Pulsbreitenfestlegung

zugeführt werden, was an den Ausgängen OC0A und OC0B erscheint.

Siehe „Die Output-Compare-Einheit verwenden“ für Details.

Das Ereignis der Gleichheit setzt außerdem die Compare-Flags OCF0A bzw. OCF0B,

was wiederum zur Erzeugung einer Output-Compare-Interruptanforderung verwendet werden kann.

15.3 Taktquellen

Der Zähler/Zeitgeber kann durch eine interne oder durch eine externe Quelle getaktet werden.

Die Taktquelle wird mit den Taktauswahl-Bits CS02 bis CS00 im Zähler/Zeitgeber-Steuerregister TCCR0 festgelegt.

Details zu den Taktquellen und dem Vorteiler finden sich im Kapitel

Vorteiler für Zähler/Zeitgeber 0 und 1.

15.4 Zählereinheit

Den Hauptbestandteil des 8-bit-Zähler/Zeitgeber 0 bildet die programmierbare Zählereinheit.

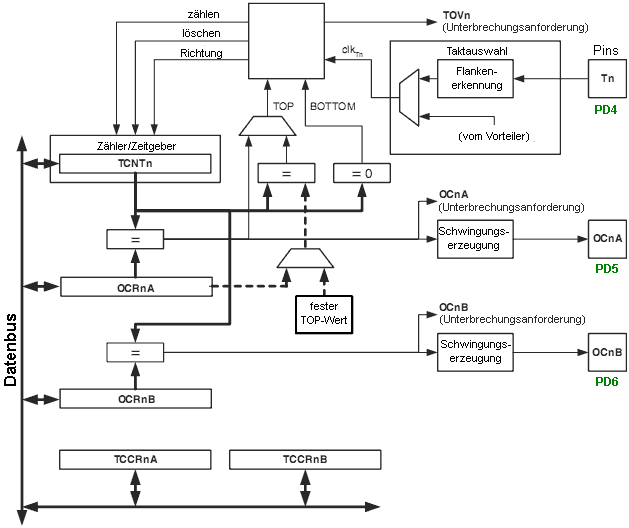

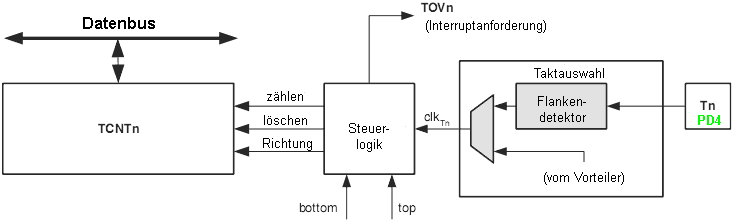

Die nachfolgende Abbildung zeigt deren Blockdiagramm und Umgebung.

Bild 15-2: Blockschaltbild der Zählereinheit

Beschreibung der internen Signale:

| count

| Inkrementiert TCNT0 um 1

|

| clkTn

| Takt für den Zähler/Zeitgeber, nachfolgend clkT0

|

| max

| Signalisiert, dass TCNT0 seinen maximalen Wert erreicht hat

|

Der Zähler wird bei jedem Takt von clkT0 um 1 erhöht.

Der Takt clkT0 kann durch eine interne oder externe Quelle erzeugt werden, die mit den Bits CS02 bis CS00 ausgewählt wird.

Wenn keine Taktquelle ausgewählt ist (CS02 bis CS00 = 0), wird der Zähler/Zeitgeber angehalten.

Unabhängig davon, ob der Takt läuft oder nicht, kann die CPU zu jeder Zeit auf den Wert des TCNT0-Registers zugreifen.

Ein Schreiben der CPU in das TCNT0-Register hat Vorrang vor allen Lösch- und Zähl-Operationen.

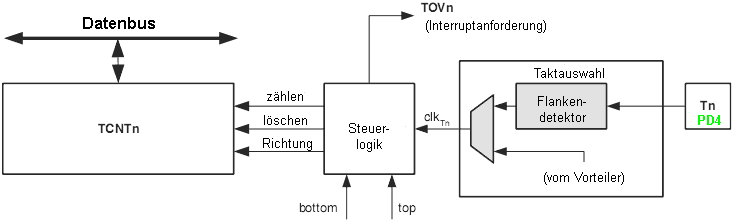

15.5 Output Compare

Bild 15-3: Blockschaltbild der Output-Compare-Einheit

15.5.1 Output Compare erzwingen

In Nicht-PWM-Modi kann der Übereinstimmungsausgang des Vergleiches auch erzwungen werden,

indem man eine 1 in das Force Output Compare (FOC0x) Bit schreibt.

Bei der erzwungenen Vergleichsübereinstimmung wird weder das OCF0x-Flag gesetzt

noch der Timer gelöscht oder neu geladen.

Allerdings wird der OCP0x-Pin aktualisiert,

so als sei eine echte Vergleichsübereinstimmung aufgetreten.

Ob der OCP0x Pin gelöscht, gesetzt oder gewechselt wird,

wird durch die Einstellungen der COM0x1- bis COM0x0-Bits festgelegt.

15.5.2 Blockade von Output-Compare beim Schreiben auf TCNT0

Alle Schreibversuche der CPU in das TCNT0-Register blockieren eine Vergleichsübereinstimmung,

die im nächsten Taktzyklus auftritt, auch wenn der Timer gestoppt ist.

Dadurch ist des möglich, die OCR0x-Register mit den gleichen Werten wie das TCNT0-Register zu beschreiben,

ohne dass dadurch ein Interrupt ausgelöst wird.

15.5.3 Nutzung der Output-Compare-Einheit

Da das Beschreiben des TCNT0-Registers in jedem Modus die Vergleichsübereinstimmung für einen Timertakt blockiert,

entstehen gewisse Risiken beim Verändern von TCNT0, wenn einer der Output-Compare-Kanäle verwendet wird,

unabhängig davon, ob der Timer läuft oder nicht.

Wenn ein Wert in das TCNT0 geschrieben wird, der dem Wert eines OCR0x entspricht,

wird die Vergleichsübereinstimmung ausbleiben, wodurch eine unkorrekte Ausgangsform erzeugt wird.

Das TCNT0 sollte daher in PWM-Modi mit variablen TOP-Werten nicht mit dem TOP-Wert beschrieben werden.

Die Vergleichsübereinstimmung beim TOP-Wert würde ignoriert und der Zähler bis zum Maximalwert FFFF weiterzählen.

Umgekehrt gilt, dass TCNT0 nicht mit dem BOTTOM-Wert beschrieben werden sollte, wenn der Zähler rückwärts läuft.

Das Einstellen der OC0x Register sollte vorgenommen werden,

bevor der entsprechende Portpin als Ausgang konfiguriert wird.

Der einfachste Weg, den OC0x-Wert zu setzen, ist die Verwendung

des Force-Output-Compare-Bits (FOC0x) im normalen Modus.

Die OCR0x-Register behalten ihren Wert auch dann,

wenn zwischen den Kurvenform-Erzeugungsmodi umgeschaltet wird.

Zu beachten ist, dass die COM0x1 bis COM0x0 Bits nicht zweifach gepuffert sind.

Daher wirken sich Veränderungen dieser Bits unmittelbar aus.

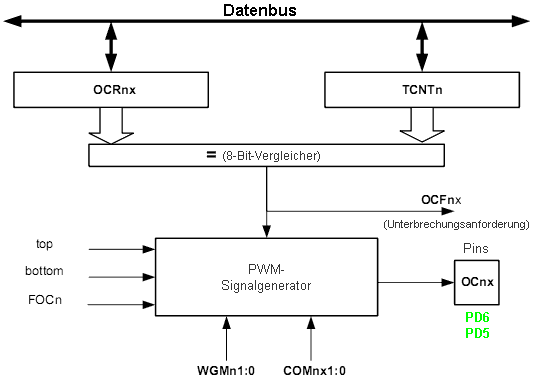

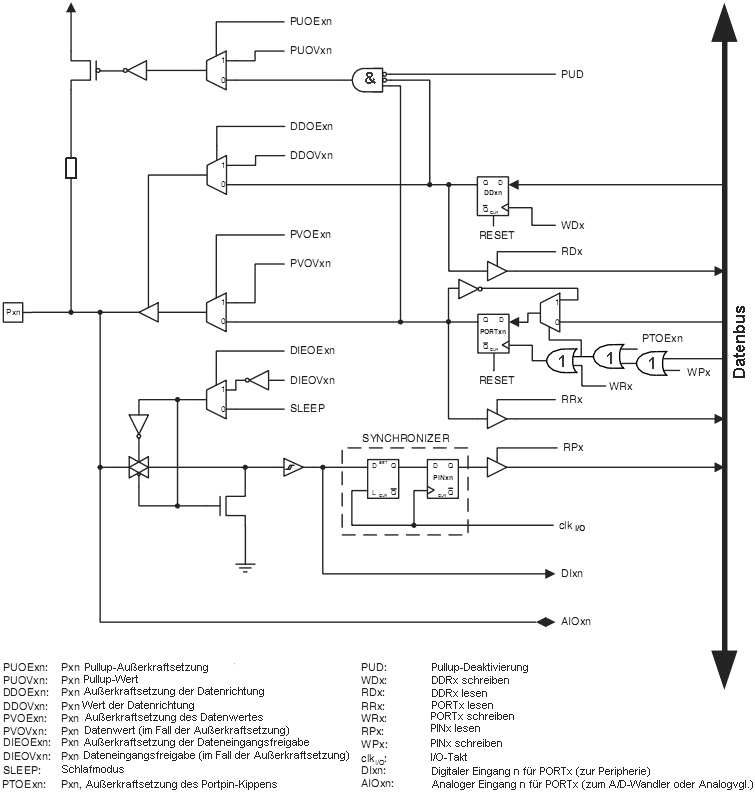

15.6 Compare-Match

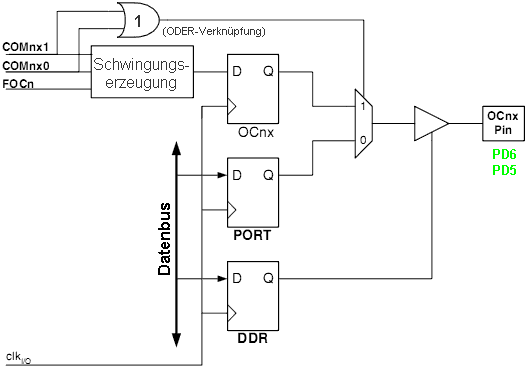

Die Compare-Output-Modusbits COM0x1 und COM0x0 haben zwei Funktionen.

Zum einen verwendet der Waveform-Generator die beiden Bits,

um den Zustand des OCR0x-Registers bei der nächsten Vergleichsübereinstimmung festzulegen.

Und zweitens kontrollieren die Bits die Ausgangsquelle des OC0x-Pins.

Das nachfolgende Bild zeigt das einfache Blockschaltbild der Logik,

die durch die COM0x1- und COM0x0-Bits beeinflusst wird.

Die I/O-Register, die I/O-Bits und die I/O-Pins sind fett dargestellt,

wobei von den Portkontrollregistern DDR und PORT nur der durch die Bits beeinflusste Teil dargestellt ist.

Wenn auf den Zustand des OCR0x verwiesen wird,

so ist damit das interne Register OCR0x gemeint und nicht das OC0x-Pin.

Bei einem Systemreset wird das OCR0x-Register auf 0 gesetzt.

Bild 15-4: Schaltbild der Compare-Match-Einheit

Die allgemeine I/O Portfunktion wird durch den Output-Compare (OC0x) überschrieben,

wenn eines der beiden Bits COM0x1 oder COM0x0 gesetzt ist.

Allerdings wird die Richtung des OC0x-Pins (Eingang oder Ausgang)

nach wie vor durch durch das Datenrichtungsregister (DDR) bestimmt.

Das Richtungsbit für die OC0x-Pins (DDR_OC0x) muss als Ausgang gesetzt werden,

bevor der Wert von OC0x am Ausgang sichtbar wird.

Die überschreibende Funktion ist grundsätzlich unabhängig

von dem ausgewählten Waveform-Generator-Modus.

Allerdings gibt es einige Ausnahmen,

die in den nachfolgenden Tabellen ersichtlich sind.

Das Design der Output-Compare-Pinlogik erlaubt das Initialisieren

des OC0x-Zustandes, bevor der Ausgang freigegeben wird.

Einige COM0x1/COM0x0-Kombinationen sind für spätere Funktionen reserviert

(siehe Beschreibung der Register).

15.6.1 Compare Output und Kurvenform-Erzeugung

15.7 Betriebsmodi

Die Zählrichtung ist immer aufwärts (inkrementieren), ein Löschen des Zählers ist nicht möglich.

Der Zähler läuft über, wenn er seinen maximalen Wert (FFh) überschreitet und er beginnt dann erneut von seinem niedrigsten Wert (00h) zu zählen.

Im normalen Fall wird das Zähler/Zeitgeber Overflow Flag (TOV0) in dem Moment gesetzt, in dem das TCNT0-Register Null wird.

Man kann in diesem Fall das Überlaufbit TOV0 als neuntes Bit des Zählers betrachten, dass allerdings durch den Zähler nur gesetzt, aber nicht gelöscht wird.

In Verbindung mit dem Timer-Überlauf Interrupt, der das TOV0 Bit automatisch löscht, kann die Auflösung des Timers durch die Software erweitert werden.

Der Zähler kann zu jeder Zeit mit einem neuen Wert beschrieben werden.

15.7.1 Normalmodus

15.7.2 Verkürzter Zählzyklus

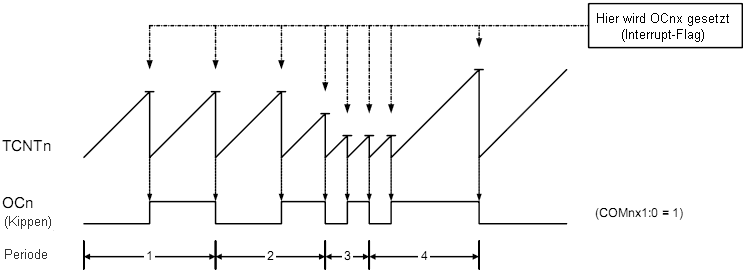

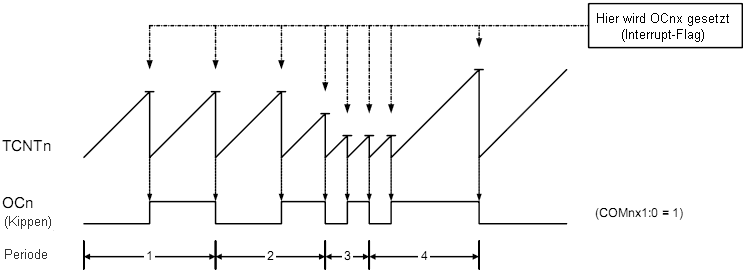

Bild 15-5: Zeitverlauf beim Verkürzten Zählzyklus

15.7.3 Schnelle PWM

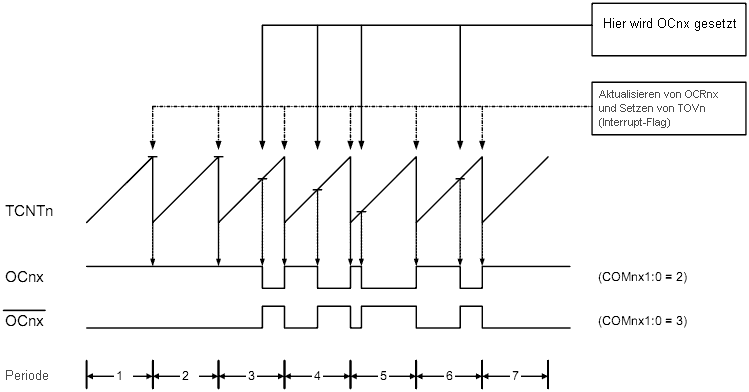

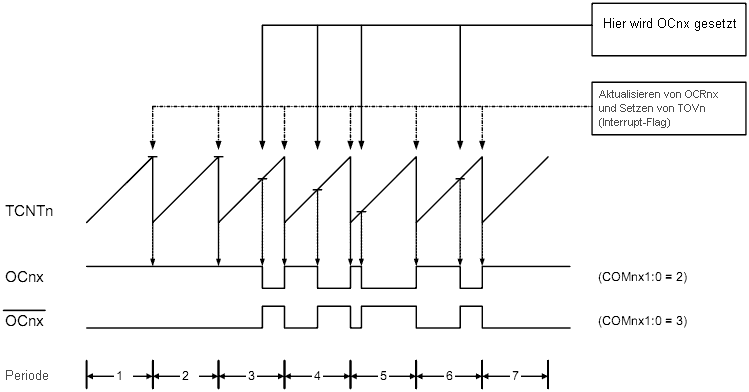

Bild 15-6: Zeitverlauf bei schneller PWM

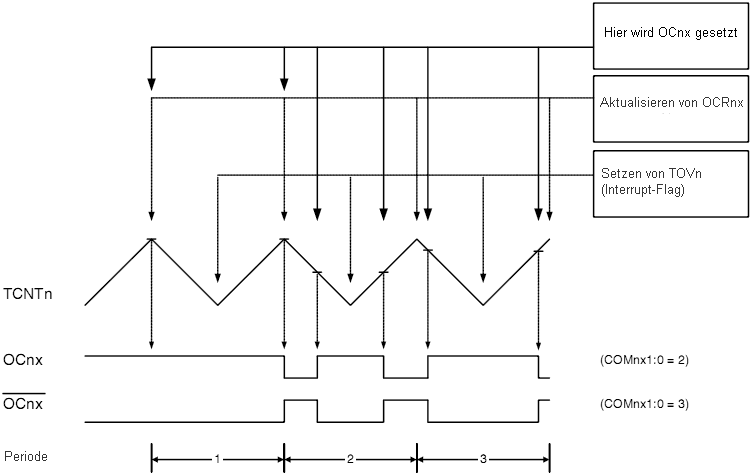

15.7.4 Phasenrichtige PWM

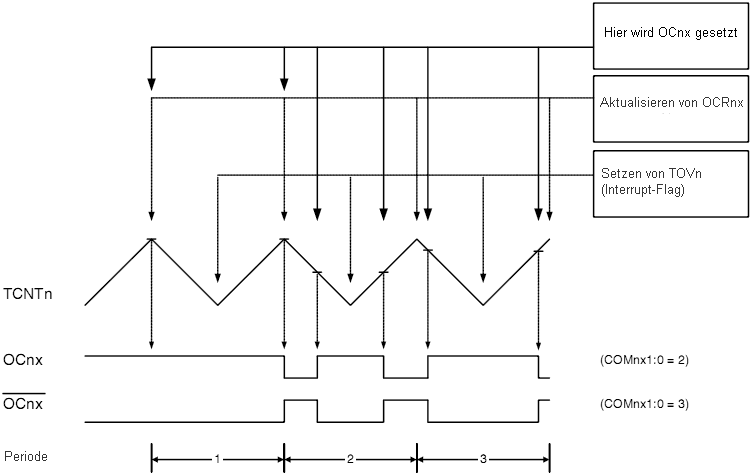

Bild 15-7: Zeitverlauf bei phasenrichtiger PWM

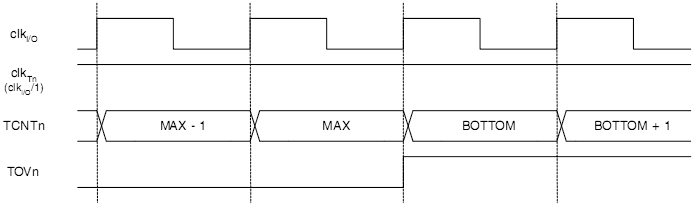

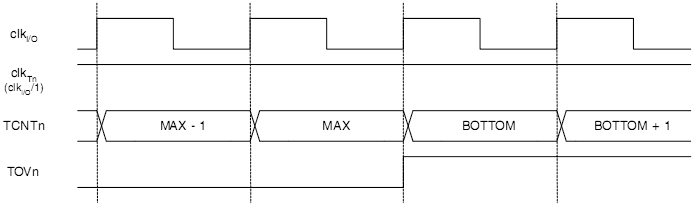

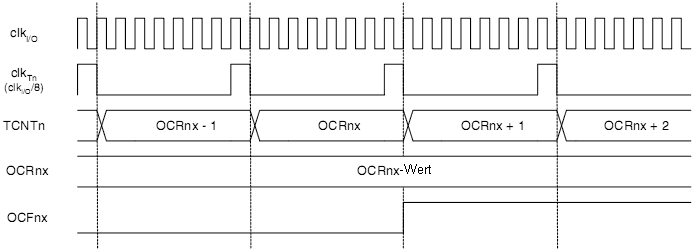

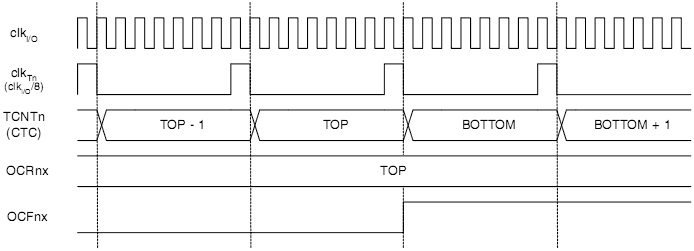

15.8 Zeitdiagramme

Der Zähler/Zeitgeber ist synchron ausgelegt, daher ist der Timer-Takt clkT0 nachfolgend als Takt-Freigabe Signal dargestellt.

Die Abbildungen zeigen auch, zu welchem Zeitpunkt das Interrupt-Flag gesetzt wird.

Die erste Abbildung zeigt die grundlegende Zähler/Zeitgeber Funktion in dem Augenblick, in dem der Zähler seinen Maximalwert überschreitet.

Bild 15-8: Zeitdiagramm ohne Vorteiler

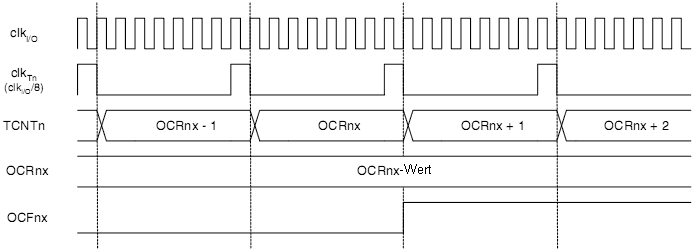

Nachfolgende Abbildung zeigt das Zeitdiagramm mit einem Vorteiler, der den I/O-Takt durch 8 teilt.

Bild 15-9: Zeitdiagramm mit Vorteiler

Folgende Abbildung zeigt das Setzen von OCF0A in allen Zählmodi außer dem verkürzten Zählumfang, wobei OCR0A = TOP ist.

Bild 15-10: Zeitdiagramm, Setzen von OCF0x, mit Vorteiler (fckl_I/O/8)

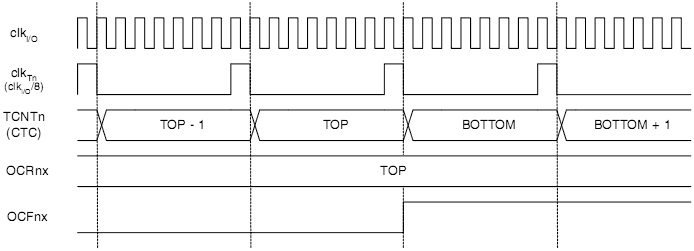

Bild 15-11 zeigt das Setzen von OCF0A und das Löschen von TCNT0 bei verkürztem Zählumfang, wobei OCR0A = TOP ist.

Bild 15-11: Zeitdiagramm bei verkürztem Zählumfang, mit Vorteiler (fckl_I/O/8)

15.9 Register-Beschreibung

15.9.1 TCCR0A — Kontrollregister A

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x44) | COM0A1 | COM0A0 | COM0B1 | COM0B0 | - | - | WGM01 | WGM00 | TCCR0A

|

|---|

| Zugriff | R/W | R/W | R/W | R/W | R | R | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

- Bit 7:6 — COM0A[1:0]: Compare Match Output A Modus

These bits control the Output Compare pin (OC0A) behavior.

If one or both of the COM0A1:0 bits are set, the

OC0A output overrides the normal port functionality of the I/O pin it is connected to.

However, note that the Data

Direction Register (DDR) bit corresponding to the OC0A pin must be set in order to enable the output driver.

When OC0A is connected to the pin, the function of the COM0A1:0 bits depends on the WGM02:0 bit setting.

Table 15-2 shows the COM0A1:0 bit functionality

when the WGM02:0 bits are set to a normal or CTC mode (non-PWM).

Tabelle 15-2: Compare-Output-Modi im Nicht-PWM-Betrieb

| COM0A1 | COM0A0 | Beschreibung

|

|---|

| 0 | 0 | Normale Portfunktion, OC0A abgetrennt

|

| 0 | 1 | Pegelwechsel an OC0A bei Compare-Match

|

| 1 | 0 | Löschen von OC0A bei Compare-Match

|

| 1 | 1 | Setzen von OC0A bei Compare-Match

|

Table 15-3 shows the COM0A1:0 bit functionality

when the WGM01:0 bits are set to fast PWM mode.

Tabelle 15-3: Compare-Output-Modi im schnellen PWM-Betrieb (1)

| COM0A1 | COM0A0 | Beschreibung

|

|---|

| 0 | 0 | Normale Portfunktion, OC0A abgetrennt

|

| 0 | 1 | WGM02 = 0: Normale Portfunktion, OC0A abgetrennt

WGM02 = 1: Pegelwechsel an OC0A bei Compare-Match

|

| 1 | 0 | Löschen von OC0A bei Compare-Match

Setzen von OCR0A bei BOTTOM (= nichtinvertierter Modus)

|

| 1 | 1 | Setzen von OC0A bei Compare-Match

Löschen von OCR0A bei BOTTOM (= invertierter Modus)

|

- Hinweis

- A special case occurs when OCR0A equals TOP and COM0A1 is set.

In this case, the Compare Match is ignored, but the set or clear is done at BOTTOM.

See ”Fast PWM Mode” for more details.

Table 15-4 shows the COM0A1:0 bit functionality

when the WGM02:0 bits are set to phase correct PWM mode.

Tabelle 15-4: Compare-Output-Modi im phasenrichtigen PWM-Betrieb (1)

| COM0A1 | COM0A0 | Beschreibung

|

|---|

| 0 | 0 | Normale Portfunktion, OC0A abgetrennt

|

| 0 | 1 | WGM02 = 0: Normale Portfunktion, OC0A abgetrennt

WGM02 = 1: Pegelwechsel an OC0A bei Compare-Match

|

| 1 | 0 | Löschen von OC0A bei Compare-Match und Hochzählen

Setzen von OCR0A bei Compare-Match und Runterzählen

|

| 1 | 1 | Setzen von OC0A bei Compare-Match

Löschen von OCR0A bei Compare-Match und Runterzählen

|

- Hinweis

- A special case occurs when OCR0A equals TOP and COM0A1 is set.

In this case, the Compare Match is ignored, but the set or clear is done at TOP.

See ”Phase Correct PWM Mode” for more details.

- Bit 5:4 — COM0B[1:0]: Compare Match Output B Modus

Wie oben

Diese Bits sind reserviert und werden immer als 0 gelesen.

- Bit 1:0 — WGM0[1:0]: PWM-Betriebsart

Tabelle 15-8: Bit-Beschreibung zur Art der Schwingungserzeugung

- Hinweise

- MAX = 0xFF

- BOTTOM = 0x00

15.9.2 TCCR0B — Kontrollregister B

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x45) | FOC0A | FOC0B | - | - | WGM02 | CS02 | CS01 | CS00 | TCCR0B

|

|---|

| Zugriff | W | W | R | R | R/W | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

- Bit 7 — FOC0A: Output-Compare A erzwingen

- Bit 6 — FOC0B: Output-Compare B erzwingen

Diese Bits sind reserviert und werden immer als 0 gelesen.

- Bit 3 — WGM02: PWM-Betriebsart

Siehe TCCR0A und Tabelle oben.

- Bit 2:0 — CS0[2:0]: Taktauswahl

Diese Bits wählen die Taktquelle für den Zähler/Zeitgeber 0 aus.

Tabelle 15-9: Bits zur Taktauswahl

| CS02 | CS01 | CS00 | Beschreibung

|

|---|

| 0 | 0 | 0 | Stop, der Zähler/Zeitgeber0 wird angehalten

|

| 0 | 0 | 1 | clkI/O (kein Vorteiler)

|

| 0 | 1 | 0 | clkI/O/8

|

| 0 | 1 | 1 | clkI/O/64

|

| 1 | 0 | 0 | clkI/O/256

|

| 1 | 0 | 1 | clkI/O/1024

|

| 1 | 1 | 0 | Speisung von Pin T0, fallende Flanke

|

| 1 | 1 | 1 | Speisung von Pin T0, steigende Flanke

|

Wenn die externen Pin Modi genutzt werden, um den Zähler/Zeitgeber zu takten,

dann wird ein Übergang am T0 Pin auch dann zum zählen des Zähler/Zeitgeber0 führen,

wenn der Pin als Output konfiguriert ist.

Damit ist des möglich, das Zählen über die Software zu steuern.

15.9.3 TCNT0 — Zählregister

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x46) | TCNT0[7:0] | TCNT0

|

|---|

| Zugriff | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

Das Register gibt sowohl beim Lesen

als auch beim Schreiben einen direkten Zugriff auf das 8-bit Zählregister.

15.9.4 OCR0A — Vergleichsregister A

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x47) | OCR0A[7:0] | OCR0A

|

|---|

| Zugriff | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

15.9.5 OCR0B — Vergleichsregister B

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x48) | OCR0B[7:0] | OCR0B

|

|---|

| Zugriff | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

15.9.6 TIMSK0 — Interrupt-Maske

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x6E) | - | - | - | - | - | OCIE0B | OCIE0A | TOIE0 | TIMSK0

|

|---|

| Zugriff | R | R | R | R | R | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

Diese Bits sind reserviert und werden immer als 0 gelesen.

- Bit 2 — OCIE0B: Zähler/Zeitgeber 0 Interrupt-Freigabe für Output-Compare-Match B

- Bit 1 — OCIE0A: Zähler/Zeitgeber 0 Interrupt-Freigabe für Output-Compare-Match A

- Bit 0 — TOIE0: Zähler/Zeitgeber 0 Überlauf-Interrupt-Freigabe

Wenn das TOIE0-Bit gesetzt ist und das I-Bit in Status-Register (SREG) ebenfalls gesetzt ist, dann ist der Zähler/Zeitgeber0 Overflow Interrupt freigegeben.

Die dazugehörige Interrupt-Routine wird ausgeführt, wenn ein Überlauf im Zähler/Zeitgeber0 aufgetreten ist und somit das TOV0-Bit im TIFR-Register gesetzt wurde.

15.9.7 TIFR0 — Interrupt-Flags

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x35) | - | - | - | - | - | OCF0B | OCF0A | TOV0 | TIFR0

|

|---|

| Zugriff | R | R | R | R | R | R/W! | R/W! | R/W!

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

Diese Bits sind reserviert und werden immer als 0 gelesen.

- Bit 2 — OCIE0B: Zähler/Zeitgeber 0 Interrupt anhängig für Output-Compare-Match B

- Bit 1 — OCIE0A: Zähler/Zeitgeber 0 Interrupt anhängig für Output-Compare-Match A

- Bit 0 — TOIE0: Zähler/Zeitgeber 0 Überlauf-Interrupt anhängig

Das TOV0-Bit wird gesetzt, wenn ein Überlauf in Zähler/Zeitgeber0 auftritt.

Das Bit wird automatisch gelöscht, wenn die dazugehörige Interrupt-Routine ausgeführt wird.

Alternativ kann das Flag gelöscht werden, in dem man eine logische „1“ in das Flag schreibt.

Der Interrupt wird ausgeführt, wenn das I-Bit in SREG und das TOIE0-Bit im TIMSK gesetzt sind und das TOV0-Flag durch den Überlauf gesetzt wird.