17. Vorteiler für Zähler/Zeitgeber 0 und 1

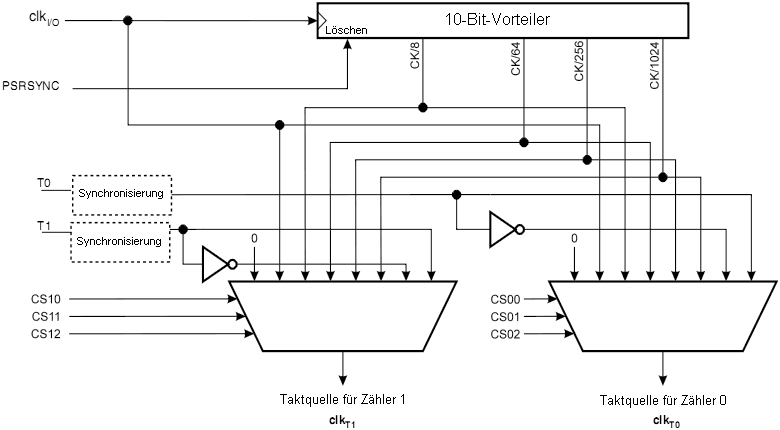

Die Zähler/Zeitgeber 0 und 1 verwenden das gleiche Vorteilermodul, können aber unterschiedliche Vorteilereinstellungen haben.

Die Nachfolgende Beschreibung gilt für beide Zähler/Zeitgeber.

17.1 Interne Taktquelle

Die Zähler/Zeitgeber können direkt durch den Systemtakt getaktet werden (CSn2 bis CSn0 = 001).

Dies ist die schnellste Arbeitsweise mit der maximalen Taktfrequenz für den Zähler/Zeitgeber, die der Frequenz des Systemtaktes fCLK_I/O entspricht.

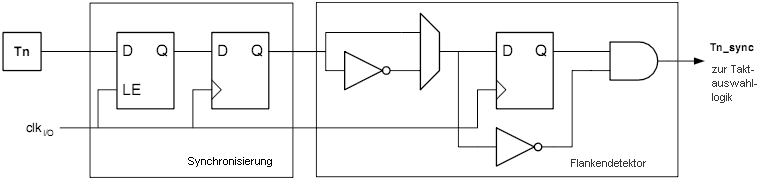

Alternativ können vier Stufen des Vorteilers als Taktquelle verwendet werden.

Der Vorteiler liefert Frequenzen von fCLK_I/O/8, fCLK_I/O/64, fCLK_I/O/256 und fCLK_I/O/1024.

17.2 Vorteiler-Reset

Der Vorteiler ist freilaufend, d.h.

er arbeitet unabhängig von der Taktauswahllogik des Zähler/Zeitgebers und wird von Zähler/Zeitgeber0 und Zähler/Zeitgeber1 gemeinsam genutzt.

Da der Vorteiler nicht durch die Taktauswahllogik beeinflusst wird, kann der Vorteiler in einem beliebigen Zustand sein, wenn er als Taktquelle für einen Zähler/Zeitgeber ausgewählt wird.

D.h. im Moment des Einschaltens als Taktquelle kann der Vorteiler einen beliebigen Zählerstand zwischen 1 und N+1 (mit N = 8, 64, 256 oder1024) haben.

Es ist also wichtig, den Vorteiler zu reseten, um ihn mit der Programmausführung zu synchronisieren.

Auf jeden Fall muss mit der notwendigen Vorsicht bedacht werden, dass beide Zähler/Zeitgeber den Vorteiler gemeinsam nutzten.

Ein Reset des Vorteilers wirkt sich auf alle Zähler/Zeitgeber aus, die mit ihm verbunden sind.

17.3 Externe Taktquelle

Eine externe Taktquelle an den Pins T0 und T1 kann verwendet werden, um als Takt clkT0 und clkT1 für die Zähler/Zeitgeber zu dienen.

Die T0/T1 Pins werden einmal während jedes Systemtaktes durch die Synchronisationslogik abgetastet.

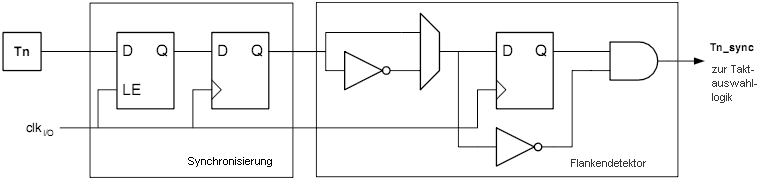

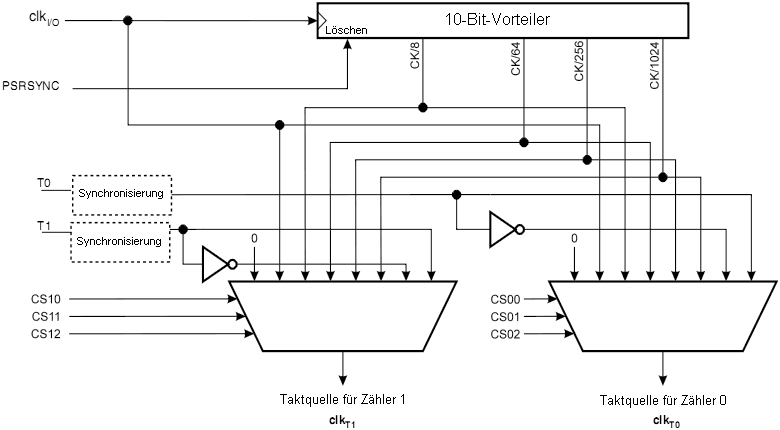

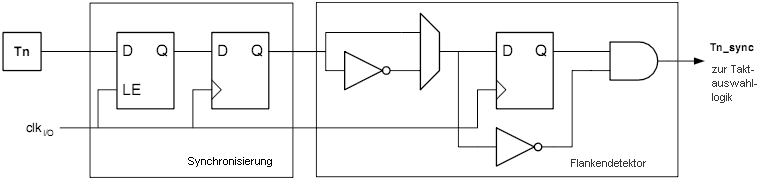

Das synchronisierte (abgetastete) Signal wird dann an einen Flankenerkenner weitergeleitet.

Das nachfolgende Abbild zeigt das Blockdiagramm der Synchronisation und Flankenerkennung.

Die Register werden durch die positive Flanke des internen Systemtaktes clkI/O.

Das Latch ist während der positiven Periode des internen Systemtaktes transparent.

Der Flankenerkenner generiert einen Puls der clkT1/clkT0 Takte bei jeder positiven (CSn2 bis CSn0 = 111) bzw.

negativen (CSn2 bis CSn0 = 110) Flanke, die er erkennt.

Bild 17-1: Pin Sampling T1/T0

Die Synchronisation und die Flankenerkennung erzeugen eine Verzögerung von 2,5 bis 3,5 Systemtakten zwischen dem Auftreten der Flanke am T9/T1 Pin und dem Inkrementieren des Zählers.

Das Freigeben und Sperren des Takteinganges muss ausgeführt werden, solange T1/T0 für mindestens einen Systematakt stabil sind, da andernfalls ein ungewollter Taktimpuls für den Zähler/Zeitgeber erzeugt werden kann.

Jede Hälfte des externen Taktsignals muss länger sein, als ein Zyklus des internen Taktsignals um ein korrektes Abtasten des Signals sicherzustellen.

Die Frequenz des externen Signals darf maximal halb so groß sein wie die Frequenz des internen Systemtaktes, wenn das Puls-Pausenverhältnis 1:1 beträgt (Abtasttheorem).

Da es immer Toleranzen beim Systemtakt selbst wie auch bei dem externen Takt geben kann, sollte die Frequenz des externen Signals kleiner als fclk_I/O/2,5 sein.

Ein externes Signal kann nicht vorgeteilt werden.

Bild 17-2: Vorteiler Timer0/Timer1

17.4 Registerberschreibung

17.4.1 GTCCR — Allgemeines Zähler/Zeitgeber-Kontrollregister

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x43) | TSM | - | - | - | - | - | PSRASY | PSRSYNC | GTCCR

|

|---|

| Zugriff | R/W | R | R | R | R | R | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

- Bit 7 — TSM: Synchronisationsmodus

Eine Eins aktiviert den Synchronisationsmodus für die Zeitgeber 0 und 1.

In diesem Fall werden die Bits PSRASY und PSRSYNC gehalten und damit

ein gegebenes Rücksetzsignal gehalten.

Damit werden die Zeitgeber angehalten und können ohne die Gefahr eintreffender Zählimpulse konfiguriert werden.

Wird TSM gelöscht, werden in Folge die Bits PSRASY und PSRSYNC gelöscht,

und die beiden Zeitgeber starten exakt gleichzeitig.

In der Zählerbetriebsart ist der Vorteiler ohne Effekt.

- Bit 0 — PSRSYNC: Vorteiler rücksetzen

Wenn dieses Bit mit einer 1 beschrieben wird, wird der Vorteiler für Zähler/Zeitgeber 0 und 1 zuückgesetzt.

Das Bit wird durch die Hardware automatisch wieder gelöscht, wenn der Reset ausgeführt wurde.

Dies geschieht sofort, außer wenn das TSM-Bit gesetzt ist.

Man beachte, dass die Zähler/Zeitgeber 0 und 1 den Vorteiler gemeinsam verwenden,

und ein Rücksetzen betrifft beide Zähleinheiten.