13. Externe Interrupts

Externe Interrupts können über die Eingänge INT0 und INT1

sowie einen Pegelwechsel an PCINT0 bis PCINT23 getriggert werden.

Die Triggerung erfolgt auch dann, wenn die Pins als Ausgang konfiguriert sind.

Dadurch können diese Interrupts auch per Software ausgelöst werden.

Der Pegelwechsel-Interrupt 2 wird ausgelöst, wenn ein Pin aus PCINT[23:16] kippt.

Der Pegelwechsel-Interrupt 1 wird ausgelöst, wenn ein Pin aus PCINT[14:8] kippt.

Der Pegelwechsel-Interrupt 0 wird ausgelöst, wenn ein Pin aus PCINT[7:0] kippt.

Die Maskierungsregister PCMSK2, PCMSK1 und PCMSK0 steuern schließlich,

welche Pins zum Interrupt führen.

Pegelwechsel-Interrupts an PCINT[23:0] sind asynchron

und können dazu verwendet werden, den Chip aus einem Schlafmodus „tiefer“ als Idle zu wecken.

Die (althergebrachten) externen Interrupts INT0 und INT1

können durch eine fallende oder steigende Flanke

oder durch einen Low-Pegel ausgelöst werden.

Die entsprechende Einstellung erfolgt im Register EICRA.

Wenn ein externer Interrupt freigegeben und als Low-Pegel-aktiv konfiguriert ist,

dann wird der Interrupt so lange gehalten, wie der Low-Pegel am Pin anliegt.

Das Erkennen von Interrupts mit fallender oder steigender Flanke setzt voraus, dass der I/O-Takt aktiv ist.

Low-Pegel-Interrupts an INT0 und INT1 werden hingegen auch asynchron erkannt.

Das bedeutet, dass diese Interrupts verwendet werden können,

um den Chip aus allen Schlafmodi „tiefer“ als Idle aufzuwecken.

Der I/O-Takt wird in allen Schlafmodi angehalten, außer bei Idle.

- Hinweis

-

Zu beachten ist, dass, wenn ein Pegel-Interrupt dazu verwendet wird,

den Chip aus dem Schlafmodus Leistung-weg aufzuwecken, der Pegel so lange gehalten werden muss,

dass der Controller komplett aufwachen kann, um einen Interrupt auszulösen.

Wenn der Pegel verschwindet, bevor die Hochlaufzeit abgelaufen ist,

dann wird der Controller trotzdem aufwachen, aber keinen Interrupt generieren.

Die Hochlaufzeit wird durch die SUT- und CKSEL-Fuses

wie unter „Taktsystem“ beschrieben festgelegt.

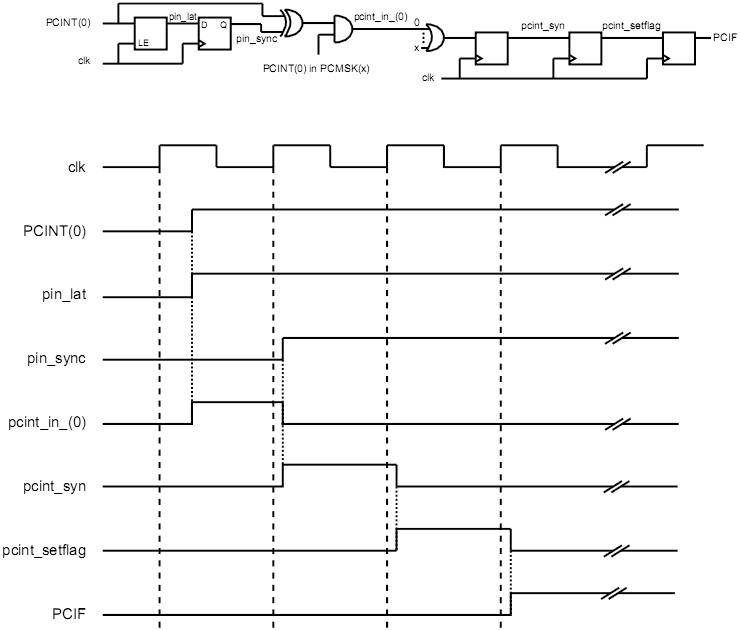

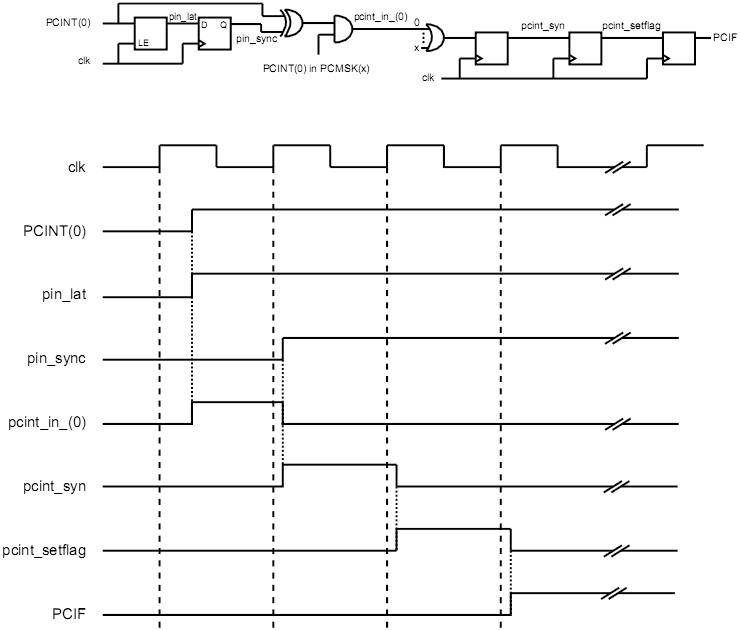

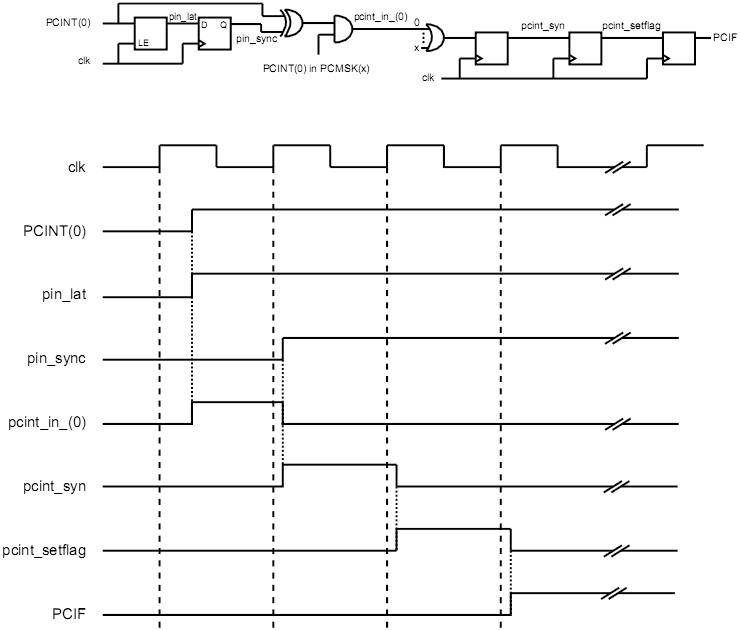

13.1 Pegelwechsel-Zeiten

Bild 13-1: Zeitverlauf beim Pegelwechsel-Interrupt

13.2 Register-Beschreibung

13.2.1 EICRA — Kontrollregister A

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x69) | - | - | - | - | ISC11 | ISC10 | ISC01 | ISC00 | EICRA

|

|---|

| Zugriff | R | R | R | R | R/W | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

- Bit 3, 2 — ISC1[1:0]: INT1-Auslöser Bit 1 und 0

Der externe Interrup1 wird über den Pin INT1 aktiviert,

wenn das I-Bit im Statusregister und das dazugehörige Interrupt-Masken-Bit

im GICR-Register gesetzt sind.

Die Pegel und Flanken, die am INT1 Pin einen Interrupt auslösen,

sind in nachfolgender Tabelle beschrieben.

Der Wert des INT1 Pins wird abgetastet, bevor eine Flanke erkannt wird.

Wenn Flanken oder wechselnde Pegel als den Interrupt auslösendes Ereignis ausgewählt werden,

so müssen diese länger als eine Taktperiode andauern, damit sie einen Interrupt erzeugen.

Kürzere Impulse führen nicht garantiert zum Auslösen eines Interrupts.

Wenn Low-Pegel als auslösendes Ereignis ausgewählt wurde,

so muss dieser mindestens so lange anliegen,

bis der gerade ausgeführt Befehl komplett abgearbeitet ist.

Tabelle 13-1: Auslöser-Einstellungen für INT1

| ISC11 | ISC10 | Modus

|

|---|

| 0 | 0 | Low-Pegel am INT1-Pin löst Interrupt aus

|

| 0 | 1 | Jeder logische Wechsel am INT1-Pin löst Interrupt aus

|

| 1 | 0 | Eine fallende Flanke am INT1-Pin löst Interrupt aus

|

| 1 | 1 | Eine steigende Flanke am INT1-Pin löst Interrupt aus

|

- Bit 1, 0 — ISC0[1:0]: INT0-Auslöser Bit 1 und 0

Der externe Interrupt0 wird über den Pin INT0 aktiviert,

wenn das I-Bit im Statusregister und das dazugehörige

Interrupt-Masken-Bit im GICR Register gesetzt sind.

Die Pegel und Flanken, die am INT0 Pin einen Interrupt auslösen,

sind in nachfolgender Tabelle beschrieben.

Der Wert des INT0 Pins wird abgetastet, bevor eine Flanke erkannt wird.

Wenn Flanken oder wechselnde Pegel als den Interrupt auslösendes Ereignis ausgewählt werden,

so müssen diese länger als eine Taktperiode andauern, damit sie einen Interrupt erzeugen.

Kürzere Impulse führen nicht garantiert zum Auslösen eines Interrupts.

Wenn Low-Pegel als auslösendes Ereignis ausgewählt wurde,

so muss dieser mindestens so lange anliegen,

bis der gerade ausgeführt Befehl komplett abgearbeitet ist.

Tabelle 13-2: Auslöser-Einstellungen für INT0

| ISC01 | ISC00 | Modus

|

|---|

| 0 | 0 | Low-Pegel am INT0-Pin löst Interrupt aus

|

| 0 | 1 | Jeder logische Wechsel am INT0-Pin löst Interrupt aus

|

| 1 | 0 | Eine fallende Flanke am INT0-Pin löst Interrupt aus

|

| 1 | 1 | Eine steigende Flanke am INT0-Pin löst Interrupt aus

|

13.2.2 EIMSK — Interrupt-Maske

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x3D) | - | - | – | – | – | – | INT1 | INT0 | EIMSK

|

|---|

| Zugriff | R | R | R | R | R | R | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|

Diese Bits sind ungenutzt und werden immer als 0 gelesen.

- Bit 1 — INT1: Externer Interrupt 1 Freigabe

Wenn das INT1-Bit gesetzt ist und das I-Bit in Status-Register (SREG) ebenfalls gesetzt ist,

dann ist der externe Interrupt1 freigegeben.

Mit den Interrupt Sense Control1 Bits 1 und 0 (ISC11 und ISC10) im General Control Register (MCUCR) wird festgelegt,

bei welcher Bedingung ein externer Interrupt erkannt wird.

Möglich sind: Steigende oder fallende Flanke, bei Pin-Wechsel oder bei Low-Pegel am INT1-Pin.

Die Bedingungen am Pin INT1 werden auch dann eine Interruptanforderung veranlassen,

wenn INT1 als Output konfiguriert ist.

Die Interruptadresse für den Interrupt ist der Interrupt Vektor INT1.

- Bit 0 — INT0: Externer Interrupt 0 Freigabe

Wenn das INT0-Bit gesetzt ist und das I-Bit in Status-Register (SREG) ebenfalls gesetzt ist,

dann ist der externe Interrupt0 freigegeben.

Mit den Interrupt Sense Control0 Bits 1 und 0 (ISC01 und ISC00) im General Control Register (MCUCR) wird festgelegt,

bei welcher Bedingung ein externer Interrupt erkannt wird.

Möglich sind: Steigende oder fallende Flanke, bei Pin-Wechsel oder bei Low-Pegel am INT0-Pin.

Die Bedingungen am Pin INT0 werden auch dann eine Interruptanforderung veranlassen, wenn INT0 als Output konfiguriert ist.

Die Interruptadresse für den Interrupt ist der Interrupt Vektor INT0.

13.2.3 EIFR — Interrupt-Flags

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x3C) | - | - | – | – | – | – | INTF1 | INTF0 | EIFR

|

|---|

| Zugriff | R | R | R | R | R | R | R/W! | R/W!

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|

Diese Bits sind ungenutzt und werden immer als 0 gelesen.

- Bit 1 — INTF1: Externer Interrupt Flag1

Eine Flanke oder ein logischer Wechsel am INT1-Pin triggert eine Interruptanforderung und das INTF1-Bit wird gesetzt.

Wenn das I-Bit im SREG und das INT1-Bit im GICR Register gesetzt sind, wird der Controller zum Interruptvektor INT1 springen.

Das Flag wird gelöscht, wenn die Interrupt-Routine ausgeführt wurde.

Alternativ kann das Flag gelöscht werden, indem man eine logische 1 in das Flag schreibt.

Das Flag ist immer gelöscht, wenn INT1 als Pegel-Interrupt (Low-Pegel) eingestellt ist.

- Bit 0 — INTF0: Externer Interrupt Flag0

Eine Flanke oder ein logischer Wechsel am INT0-Pin triggert eine Interruptanforderung und das INTF0-Bit wird gesetzt.

Wenn das I-Bit im SREG und das INT0-Bit im GICR Register gesetzt sind, wird der Controller zum Interruptvektor INT0 springen.

Das Flag wird gelöscht, wenn die Interrupt-Routine ausgeführt wurde.

Alternativ kann das Flag gelöscht werden, indem man eine logische 1 in das Flag schreibt.

Das Flag ist immer gelöscht, wenn INT0 als Pegel-Interrupt (Low-Pegel) eingestellt ist.

13.2.4 PCICR — Pegelwechselinterrupt-Kontrolle

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x68) | - | - | – | – | – | PCIE2 | PCIE1 | PCIE0 | PCICR

|

|---|

| Zugriff | R | R | R | R | R | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|

Diese Bits sind ungenutzt und werden immer als 0 gelesen.

- Bit 2: PCIE2: Pegelwechsel-Interruptfreigabe 2

Wenn dieses Bit gesetzt ist und das I-Bit im Statusregister SREG gesetzt ist,

löst ein Pegelwechsel an einem freigegebenen PCINT[23:16] einen Interrupt aus.

Die Programmausführung verzweigt dann zum Interruptvektor PCI2.

Jedes einzelne Pin kann im Register PCMSK2 freigegeben werden.

- Bit 1: PCIE2: Pegelwechsel-Interruptfreigabe 1

Wenn dieses Bit gesetzt ist und das I-Bit im Statusregister SREG gesetzt ist,

löst ein Pegelwechsel an einem freigegebenen PCINT[14:8] einen Interrupt aus.

Die Programmausführung verzweigt dann zum Interruptvektor PCI1.

Jedes einzelne Pin kann im Register PCMSK1 freigegeben werden.

- Bit 0: PCIE2: Pegelwechsel-Interruptfreigabe 0

Wenn dieses Bit gesetzt ist und das I-Bit im Statusregister SREG gesetzt ist,

löst ein Pegelwechsel an einem freigegebenen PCINT[7:0] einen Interrupt aus.

Die Programmausführung verzweigt dann zum Interruptvektor PCI0.

Jedes einzelne Pin kann im Register PCMSK0 freigegeben werden.

13.2.5 PCIFR — Pegelwechselinterrupt-Flags

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x3B) | - | - | – | – | – | PCIF2 | PCIF1 | PCIF0 | PCIFR

|

|---|

| Zugriff | R | R | R | R | R | R/W! | R/W! | R/W!

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|

Diese Bits sind ungenutzt und werden immer als 0 gelesen.

- Bit 2: PCIF2: Pegelwechsel-Interrupt 2 anhängig

Ein Pegelwechsel an einem freigegebenen PCINT[23:16] löst eine Interruptanforderung aus,

indem das zugehörige Bit aud Eins gesetzt wird.

Wenn das Maskenbit PCIE2 und das I-Bit im Statusregister SREG gesetzt ist,

verzweigt die Programmausführung zum Interruptvektor PCI2.

Bei Ansprung der Interruptbehandlungsroutine wird das Bit automatisch gelöscht.

Alternativ kann das Bit durch Schreiben einer Eins gelöscht werden.

- Bit 1: PCIF2: Pegelwechsel-Interrupt 1 anhängig

Ein Pegelwechsel an einem freigegebenen PCINT[14:8] löst eine Interruptanforderung aus,

indem das zugehörige Bit aud Eins gesetzt wird.

Wenn das Maskenbit PCIE1 und das I-Bit im Statusregister SREG gesetzt ist,

verzweigt die Programmausführung zum Interruptvektor PCI1.

Bei Ansprung der Interruptbehandlungsroutine wird das Bit automatisch gelöscht.

Alternativ kann das Bit durch Schreiben einer Eins gelöscht werden.

- Bit 0: PCIF2: Pegelwechsel-Interrupt 0 anhängig

Ein Pegelwechsel an einem freigegebenen PCINT[7:0] löst eine Interruptanforderung aus,

indem das zugehörige Bit aud Eins gesetzt wird.

Wenn das Maskenbit PCIE0 und das I-Bit im Statusregister SREG gesetzt ist,

verzweigt die Programmausführung zum Interruptvektor PCI0.

Bei Ansprung der Interruptbehandlungsroutine wird das Bit automatisch gelöscht.

Alternativ kann das Bit durch Schreiben einer Eins gelöscht werden.

13.2.6 PCMSK2 — Pegelwechsel-Maske 2

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x6D) | PCINT23 | PCINT22 | PCINT21 | PCINT20 | PCINT19 | PCINT18 | PCINT17 | PCINT16 | PCMSK2

|

|---|

| Zugriff | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|

- Bit 7:0 — PCINT[23:16]: Pinweise Freigabe der Pegelwechsel-Erkennung

Jedes der Bits gibt die Logik zur Erkennung von Pegelwechseln frei (wenn Eins) oder sperrt diese (wenn Null).

Ein erkannter Pegelwechsel führt zum Setzen der Interruptanforderung PCIE2 in PCICR

und schließlich zum Interrupt, wenn freigegeben.

13.2.7 PCMSK1 — Pegelwechsel-Maske 1

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x6C) | - | PCINT14 | PCINT13 | PCINT12 | PCINT11 | PCINT10 | PCINT9 | PCINT8 | PCMSK1

|

|---|

| Zugriff | R | R/W | R/W | R/W | R/W | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|

Dieses Bit ist ungenutzt und wird immer als 0 gelesen.

- Bit 6:0 — PCINT[14:8]: Pinweise Freigabe der Pegelwechsel-Erkennung

Jedes der Bits gibt die Logik zur Erkennung von Pegelwechseln frei (wenn Eins) oder sperrt diese (wenn Null).

Ein erkannter Pegelwechsel führt zum Setzen der Interruptanforderung PCIE1 in PCICR

und schließlich zum Interrupt, wenn freigegeben.

13.2.8 PCMSK0 — Pegelwechsel-Maske 0

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x6B) | PCINT7 | PCINT6 | PCINT5 | PCINT4 | PCINT3 | PCINT2 | PCINT1 | PCINT0 | PCMSK0

|

|---|

| Zugriff | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|

- Bit 7:0 — PCINT[7:0]: Pinweise Freigabe der Pegelwechsel-Erkennung

Jedes der Bits gibt die Logik zur Erkennung von Pegelwechseln frei (wenn Eins) oder sperrt diese (wenn Null).

Ein erkannter Pegelwechsel führt zum Setzen der Interruptanforderung PCIE0 in PCICR

und schließlich zum Interrupt, wenn freigegeben.