24. Der Analog-Digital Wandler

24.1 Features

- 10-bit Auflösung (8-bit Genauigkeit bei ADC 4 und ADC5)

- +- 2 LSB absolute Genauigkeit

- 0,5 LSB integrale Nichtlinearität

- optionale Streichung der Offsetspannung

- 65 260 µs Wandlungszeit

- bis zu 15.000 Wandlungen pro Sekunde

- 6 gemultiplexte Einzeleingänge

- 2 weitere gemultiplexte Eingänge im TQFP und MLF Gehäuse

- Auswählbare 2,56 V ADC Referenzspannung

- 0 VCC Eingangsspannung an den Einzeleingängen

- Optionale linksbündiges Aufbereiten für das Auslesen der Wandlungsergebnisse

- Kontinuierliche oder Einzelwandlung

- Interrupt bei Ende der Wandlung

- Sleep-Modus Noise Canceler

24.2 Übersicht

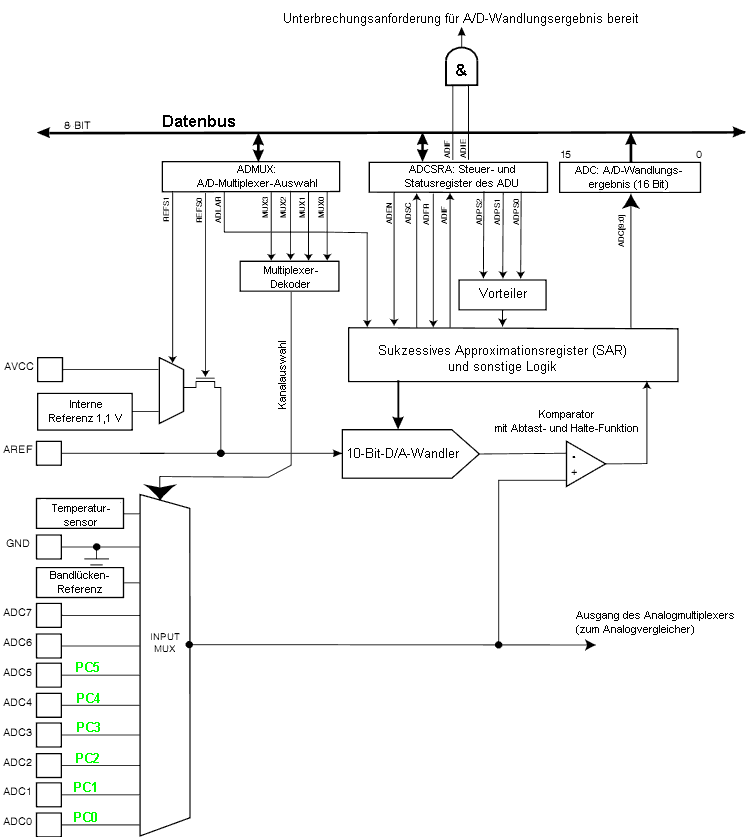

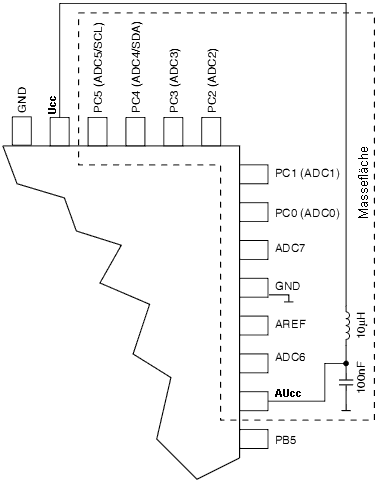

Der ATmega8 bietet einen 10-bit Analog-Digital-Wandler, der nach dem Prinzip der succsessiven Approximation arbeitet.

Der Analog-Digital-Wandler ist mit einem analogen Multiplexer verbunden, der die Auswahl zwischen acht Einzeleingängen an Port C erlaubt.

Diese Eingänge referenzieren gegen 0V (GND).

Man beachte, dass die Eingänge ADC4 und ADC5 auf 8-bit Genauigkeit limitiert sind, die Eingänge ADC 3 bis 0 und ADC 7 bis 6 haben 10-bit Genauigkeit.

Der ADC enthält einen Sample and Hold Verstärker, der sicherstellt, dass die Eingangsspannung für den Wandler während des Wandlungsvorganges konstant bleibt.

Der ADC hat einen separaten Pin für die Versorgungsspannung (AVCC).

AVCC darf nicht mehr als +- 0,3 V von VCC abweichen.

Siehe Kapitel ADC Störungsunterdrückung.

Die interne Referenzspannung von nominell 2,56V wird auf dem Chip erzeugt.

Die Referenzspannung sollte durch einen externen Kondensator am Pin AREF gestützt werden, um eine Störsicherheit zu erreichen.

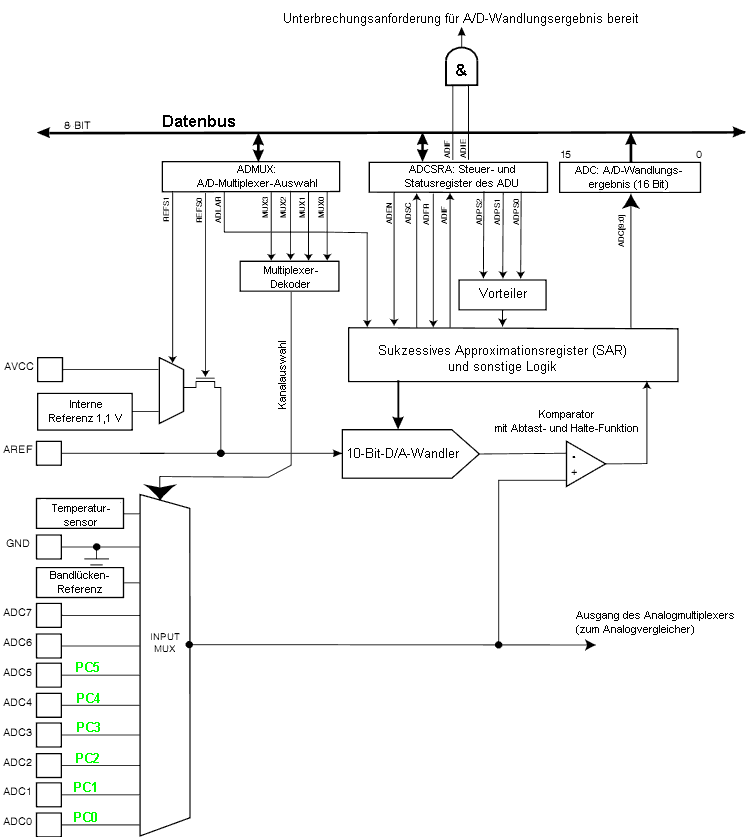

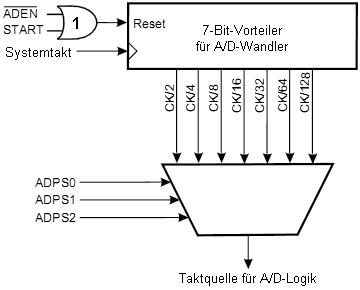

Blockschaltbild des Analog-Digital-Wandlers

Bild 24-1: Blockschaltbild des Analog-Digital-Wandlers

Der Analog-Digital-Wandler wandelt eine analoge Eingangsspannung durch succsessive Approximation in einen 10-bit Digitalwert.

Der kleinste Wert enstpricht GND, der maximale Wert entspricht der ausgewählten Referenzspannung minus ein LSB.

Die Referenzspannung für den Analog-Digital-Wandler kann durch die Bits REFS1 und REFS0 im ADMUX-Register ausgewählt werden, die Referenzspannung liegt dann auch am AVCC Pin an.

Möglich sind VCC oder die interne Referenzspannung von 2,56V.

Die Spannung an AVCC kann durch einen externen Kondensator am AREF-Pin zur besseren Rauschunterdrückung gestützt werden.

Die analogen Eingänge werden mit den Bits MUX2 bis MUX0 im ASMUX-Register ausgewählt.

Jeder der Eingänge sowie GND oder die feste Bandgap Referenzspannung können als Einzeleingang für den Analog-Digital-Wandler ausgewählt werden.

Der Analog-Digital-Wandler kann in zwei Arten betrieben werden, der kontinuierlichen oder der einzelnen Wandlung.

Bei der Einzelwandlung wird jede Wandlung durch das Programm einzeln gestartet.

Bei der kontinuierlichen Wandlung werden die Eingänge ständig ausgewertet und die Daten im ADC Data Register aktualisiert.

Das ADFR-Bit im ADCSR-Register wählt zwischen diesen beiden Möglichkeiten aus.

Der Analog-Digital-Wandler wird freigegeben, indem das ADEN-Bit im ADCSR-Register gesetzt wird.

Änderungen an der Referenzspannung und den Input Kanälen werden erst wirksam, wenn das ADEN-Bit gesetzt ist.

Wenn das ADEN-Bit gelöscht ist, verbraucht der Analog-Digital-Wandler kein Strom.

Es ist also sinnvoll, das Bit zu löschen, bevor in den Stromsparmodus umgeschaltet wird.

Der Analog-Digital-Wandler erzeugt ein 10-bit Ergebnis, das in den ADC Data Registern ADCH und ADCL abgelegt wird.

Normalerweise wird das Ergebnis rechtsbündig in den beiden Registern abgelegt, optional kann das Ergebnis aber auch linksbündig in ADCH und ADCL geschrieben werden.

Die Einstellung erfolgt mit dem ADLAR-Bit im ADMUX-Register.

Wenn das Ergebnis linksbündig geschrieben wird, und keine größere Auflösung als 8 Bit benötigt wird, so kann das komplette (8-Bit) Ergebnis direkt aus ADCH gelesen werden.

Andernfalls muss erst ADCL und dann ADCH gelesen werden, um sicherzustellen, dass beide Daten zu dem selben Wandlungsergebnis gehören.

Sobald ADCL gelesen wird, kann der Analog-Digital-Wandler keine Zugriffe auf die Datenbytes ausführen.

Das bedeutet, dass wenn ADCL gelesen wurde und eine weitere Wandlung abgeschlossen wurde, bevor ADCH ausgelesen ist, werden beide Register nicht mit den neuen Werten beschrieben und das neue Wandlungsergebnis geht verloren.

Wenn ADCH gelesen wird, wird der Zugriff auf die Register ADCL und ADCH wieder freigegeben.

Der ADC hat einen eigenen Interrupt, der getriggert werden kann, wenn eine Wandlung abgeschlossen wurde.

Wenn der Zugriff des ADC auf die Datenregister zwischen dem Lesen von ADCH und ADCL gesperrt ist, wird der Interrput trotzdem getriggert, auch wenn das Ergebnis verloren geht.

24.3 Starten einer Wandlung

Eine Wandlung wird gestartet, indem eine 1 in das ADC Start Conversion (ADSC) Bit geschrieben wird.

Das Bit bleibt während der Wandlung gesetzt und wird nach Beendigung der Wandlung automatisch durch die Hardware wieder gelöscht.

Wenn während eine Wandlung noch läuft ein anderer Input-Kanal ausgewählt wird, wird die laufende Wandlung erst bis zum Ende durchgeführt, bevor auf den anderen Kanal umgeschaltet wird.

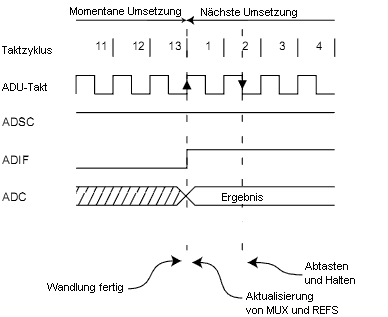

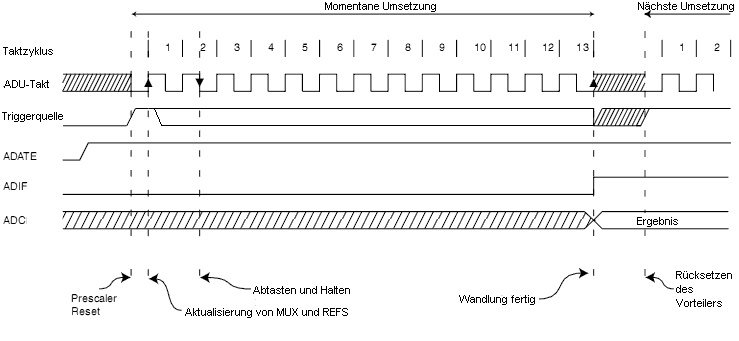

Im Freilaufenden Modus tastet der ADC kontinuierlich ab und aktualisiert die Datenregister.

Der Freilaufende Modus wird ausgewählt, indem das ADFR Bit im ADCSRA Register auf 1 gesetzt wird.

Die erste Wandlung muss dann gestartet werden indem eine logische 1 in das ADSC Bit im ADCSRA Register geschrieben wird.

In diesem Modus führt der ADC kontinuierlich Wandlungen durch, unabhängig davon, ob das ADC Interrupt Flag ADIF gelöscht ist oder nicht.

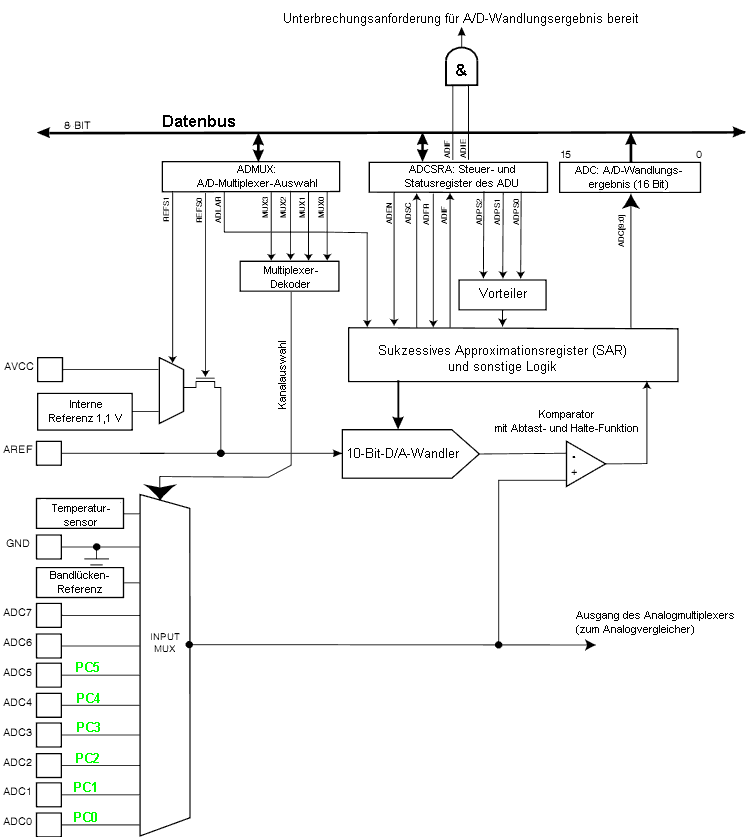

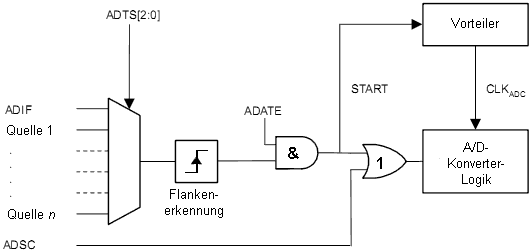

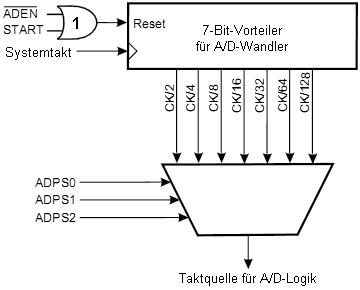

Bild 24-2: Auto-Trigger-Logik

24.4 Vorteiler und Wandlungszeit

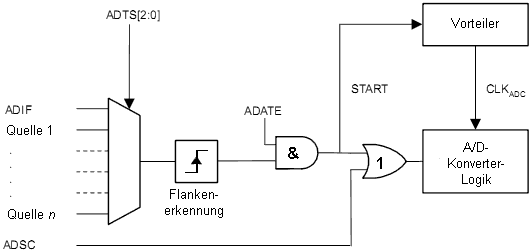

Bild 24-3: ADU-Vorteiler

Die Schaltung für die succsessive Approximation benötigt einen Takt mit einer Frequenz zwischen 50kHz und 200kHz, um die maximale Aulösung zu erreichen.

Wenn kleinere Auflösungen als 10 bit ausreichen, kann die Taktfrequenz des ADC auch höher als 200 kHz sein, um dadurch eine höhere Abtastrate zu erreichen.

Das ADC-Modul enthält daher einen Vorteiler, der einen brauchbaren ADC-Takt aus CPU Taktfrequenzen über 100 kHz erzeugt.

Der Vorteiler wird durch die ADPS Bits im ADCSRA Register eingestellt.

Der Vorteiler startet in dem Moment, in dem der Analog-Digital-Wandler durch Setzen des ADEN-Bits im ADCSR-Register eingeschaltet wird.

Der Vorteiler arbeitet so lange, wie ADEN gesetzt ist und wird kontinuierlich zurückgesetzt, wenn ADEN auf Low steht.

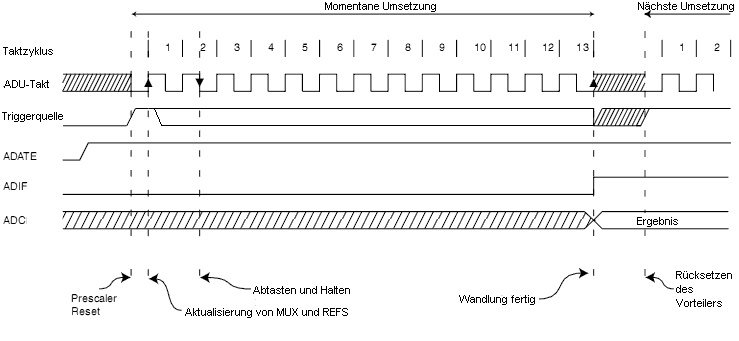

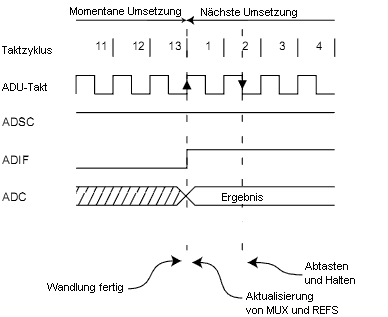

Wenn eine Wandlung durch Setzen des ADSC-Bits im ADCSRA-Register gestartet wird, beginnt die Wandlung mit der nächsten steigenden Flanke des ADC-Taktes.

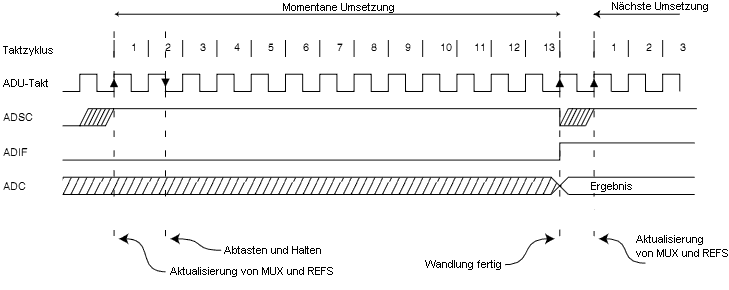

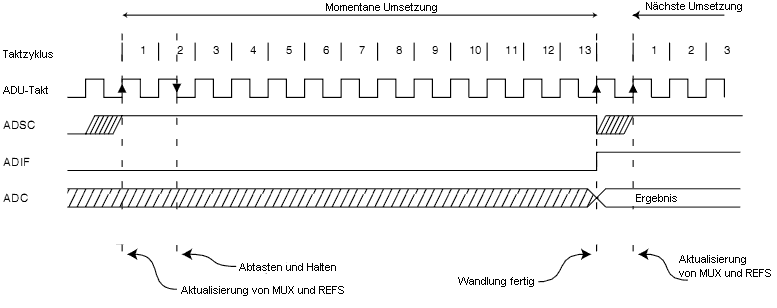

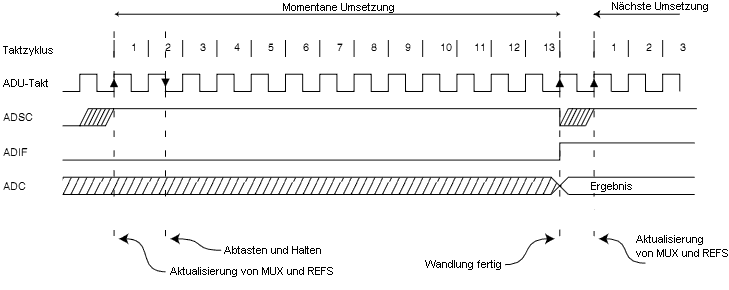

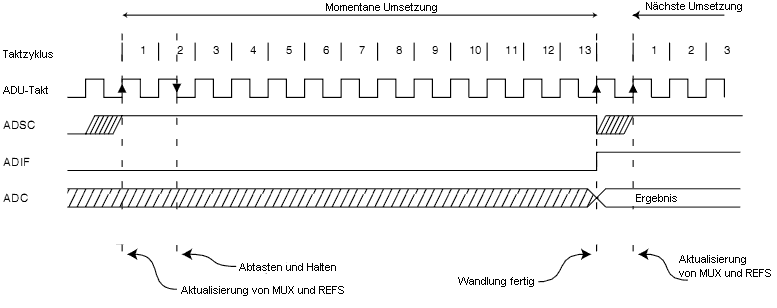

Eine normale Wandlung dauert 13 ADC-Takte lang.

Die erste Wandlung, die nach dem Einschalten des ADC durchgeführt wird, dauert allerdings 25 Takte, da der analoge Schaltkreis erst initialisiert werden muss.

Der aktuelle sample and hold Vorgang beginnt 1,5 ADC-Takte nach dem Start einer normalen Wandlung und 13,5 ADC-Takte nach dem Start einer längern Wandlung.

Nachdem eine Wandlung abgeschlossen wurde, wird das Ergebnis in die ADC-Daten-Register geschrieben und das ADIF-Flag wird gesetzt.

Im Modus der Einzelwandlung wird gleichzeitig auch das ADSC-Bit gelöscht.

Die Software kann das ADSC-Bit dann wieder setzen und eine neue Wandlung wird mit der steigenden Flanke des ADC-Taktes eingeleitet.

Im Modus der fortlaufenden Wandlung wird eine neue Wandlung sofort wieder angestoßen, sofern ADSC weiterhin auf high bleibt.

Die nachfolgende Tabelle fasst die Wandlungszeiten noch einmal zusammen.

Bild 24-4: Zeitdiagramm erste Wandlung

Bild 24-5: Zeitdiagramm Einzelwandlung

Bild 24-6: Zeitdiagramm automatisch getriggerte Wandlung

Bild 24-7: Zeitdiagramm fortlaufende Wandlung

Tabelle 24-1: A/D-Wandlungszeiten

| Bedingung | Sample&Hold (Anzahl Takte nach Start der Wandlung) | Anzahl der Takte für Wandlung

|

|---|

| Erste Wandlung | 13,5 | 25

|

| Normale Wandlung | 1,5 | 13

|

| Automatisch getriggerte Wandlung | 2 | 13,5

|

24.5 Wechsel der Kanäle und Referenzspannung

Die MUXn und REFS1 und 0 Bits im ADMUX Register sind durch ein temporäres Register, auf das die CPU zugreifen kann, einfach gebuffert.

Dadurch ist sichergestellt, dass die Kanal- und Referenzauswahl während einer Wandlung nicht verändert werden kann.

Die Kanal- und Referenzauswahl wird kontinuierlich aktualisiert, bis eine Wandlung gestartet wird.

Mit dem Start einer Wandlung wird die Kanal- und Referenzauswahl übernommen, um eine ausreichende Abtastzeit für den ADC sicherzustellen.

Das kontinuierliche Aktualisieren wird im letzten Takt, bevor die Wandlung abgeschlossen ist (ADIF im ADCSRA wird gesetzt), fortgesetzt.

Man beachte, dass eine Wandlung mit der ersten fallenden Flanke des ADC Taktes gestartet wird, die nach dem Setzen des ADSC auftritt.

Der Anwender muss also darauf bedacht sein, keinen neuen Kanal- oder Referenzwert in das ADMUX zu schreiben, bis ein ADC Taktzyklus nach dem Schreiben des ADSC vorüber ist.

Wenn sowohl ADFR als auch ADEN mit 1 beschrieben sind, kann jederzeit ein Interrupt auftreten.

Wenn das ADMUX Register in dieser Zeit verändert wird, kann der User nicht feststellen, ob das nächste Wandlungsergebnis zu den alten oder den neuen Einstellungen gehört.

ADMUX kann sicher aktualisiert werden auf folgende Weisen:

- Wenn ADFR oder ADEN gelöscht sind

- Während einer Wandlung, mindestens einen ADC Takt nach dem Wandlungsstart

- Nach einer Wandlung, bevor das Interrupt Flag als Triggerquelle gelöscht wird

Wenn das ADMUX unter einer der Bedingungen verändert wird, gelten die neuen Einstellungen für die nächste Wandlung.

24.5.1 ADU-Eingangskanäle

Wenn die Eingangskanäle gewechselt werden, sollte der User folgende Richtlinien beachten, um sicherzustellen, dass der richtige Kanal ausgewählt ist.

Im Einzelwandlungs Modus sollte der Kanal ausgewählt werden, bevor die Wandlung startet.

Die Auswahl des Kanals kann einen ADC Taktzyklus nachdem das ADSC Bit gesetzt wurde, wieder verändert werden.

Die einfachste Methode ist aber, das Ende einer Wandlung abzuwarten bevor ein anderer Kanal eingestellt wird.

Im Freilaufenden Modus wird der Kanal ausgewählt, bevor die erste Wandlung gestartet wird.

Die Auswahl des Kanals kann einen ADC Taktzyklus nachdem das ADSC Bit gesetzt wurde, wieder verändert werden.

Die einfachste Methode ist aber, das Ende der ersten Wandlung abzuwarten bevor ein anderer Kanal eingestellt wird.

Da die nächste Wandlung dann bereits automatisch begonnen hat, gehört das nächste Wandlungsergebnis noch zu den alten Kanal.

Die nachfolgenden Wandlungen gehören dann zu dem neuen Kanal.

24.5.2 ADU-Spannungsreferenz

Die Referenzspannung für den ADC (UREF) bestimmt die Wandlungsbandbreite des ADC.

Die Einzeleingänge, die VREF erreichen, führen zu einem Ergebniscode von 3Fh.

Als VREF können entweder AVCC, die interne 2,56 V Referenz oder der externe AREF Pin ausgewählt werden.

AVCC ist mit dem ADC durch einen passiven Schalter verbunden.

Die interne 2,56V Referenz wird durch einen internen Verstärker aus der internen Bandbreiten Referenz (VBG) abgeleitet.

In allen Fällen ist der externe AREF Pin direkt mit dem ADC verbunden und kann durch einen externen Kondensator zwischen dem AREF Pin und GND gestützt werden.

Mit einem hochohmigen Voltmeter kann VREF am AREF Pin gemessen werden.

Man beachte dabei, dass VREF eine Quelle mit hoher Impedanz ist und nur eine Kapazitive Last angeschlossen werden kann.

Wenn der User eine Festspannungsquelle an den AREF Pin angeschlossen hat, darf er die anderen Referenzspannungen in der Applikation nicht verwenden, da sie sonst mit der externen Spannungsquelle kurzgeschlossen werden.

Wenn keine externe Referenzspannung angeschlossen wird, kann der User zwischen AVCC und 2,56V als Referenzspannung auswählen.

Die erste Wandlung nach dem Umschalten der Referenzspannung kann ungenau sein, weshalb dieses Ergebnis vom User besser nicht verwendet werden sollte.

24.6 ADC Störungsunterdrückung

Der ADC bietet einen Rauschunterdrücker, der es erlaubt, Wandlungen auch dann durchzuführen, während der Noise Reduction Mode (siehe Sleep-Modes) einschaltet ist.

In diesem Modus werden Störungen, die von der CPU oder anderer I/O-Peripherie erzeugt werden verringert.

Die Störungsunterdrückung kann im ADC Noise Reduction Modus und im Idle Modus verwendet werden.

Um diese Möglichkeit zu nutzen, muss folgender Ablauf eingehalten werden:

- Sicherstellen, dass der ADC freigegeben ist und nicht mit einer Wandlung beschäftigt ist.

Der Einzelwandlungsmodus muss ausgewählt sein und der ADC-Complete Interrupt muss freigegeben sein.

- Einschalten des ADC Noise Reduction Mode (oder Idle Mode).

Der ADC wird eine Wandlung durchführen, während die CPU angehalten ist.

- Wenn kein anderer Interrupt auftrat, bevor der ADC mit der Wandlung fertig ist, wird der ADC-Interrupt die CPU wieder aufwecken und die ADC-Interrupt Routine wird ausgeführt.

Wenn ein anderer Interrupt die CPU aufweckt, bevor die ADC Wandlung abgeschlossen ist, wird dieser Interrupt ausgeführt und der ADC Wandlung Fertig Interrupt wird erzeugt, wenn die Wandlung abgeschlossen ist.

Die CPU verbleibt aber im aktiven Zustand bis ein neuer Sleep Befehl ausgeführt wird.

Man beachte, dass der ADC nicht automatisch ausgeschaltet wird, wenn andere Sleep Modi als der Idle oder ADC Noise Reduction Mode ausgewählt werden.

Der User ist also angehalten, das ADEN Bit zu löschen bevor einer dieser Sleep Modi eingeschaltet wird, um den unnötigen Stromverbrauch zu vermeiden.

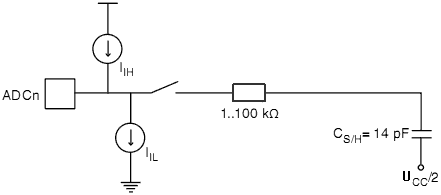

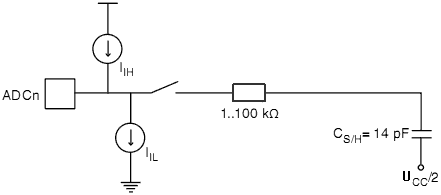

24.6.1 Analoge Eingangsbeschaltung

Bild 24-8: Analoge Eingangsbeschaltung

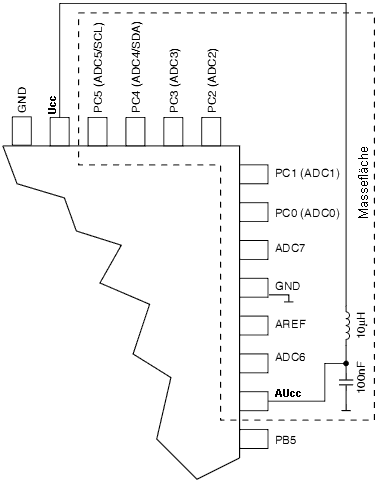

24.6.2 Techniken zur Störunterdrückung

Bild 24-9: Speisespannungs- und Masseführung

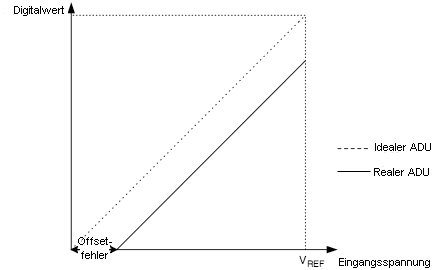

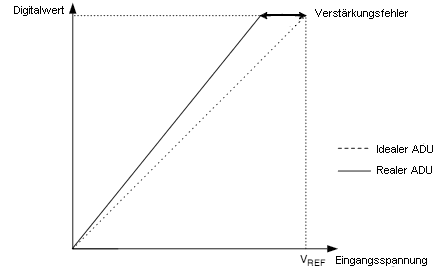

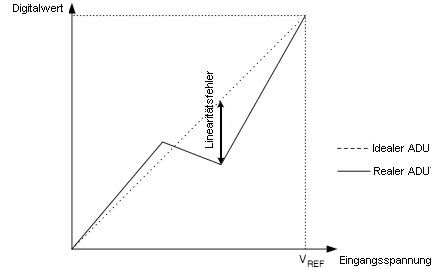

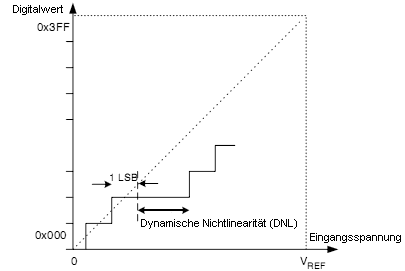

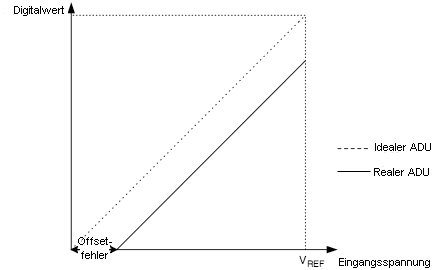

24.6.3 Definitionen zur ADU-Genauigkeit

Bild 24-10: Offsetfehler

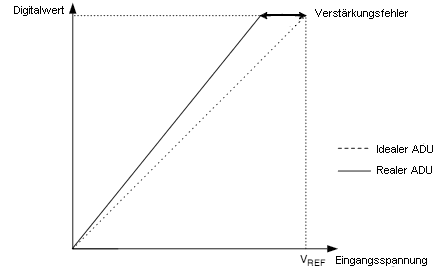

Bild 24-11: Verstärkungsfehler

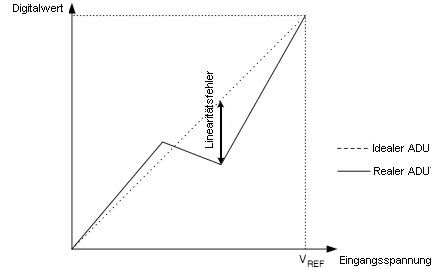

Bild 24-12: Gesamt-Linearitätsabweichung

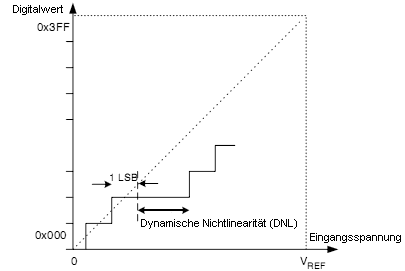

Bild 24-13: Differenzielle Linearitätsabweichung

24.7 ADU-Ergebnis

Nachdem eine Wandlung abgeschlossen ist (ADIF ist Eins),

kann das Ergebnis der Wandlung im Ergebnisregister ADC abgeholt werden.

Für eine einzelne Wandlung ist das Ergebnis

wobei UIN die Spannung am ausgewählten Eingang

und UREF die Spannung der ausgewählten Referenzspannung ist.

0x000 repräsentiert Analogmasse und 0x3FF entspricht der ausgewählten Referenzspannung minus 1 LSB.

24.8 Temperaturmessung

Die Temperaturmessung basiert auf einen Temperatursensor auf dem Chip,

der an den Eingangskanal ADC8 gebunden ist.

Die Auswahl von ADC8 durch Setzen der MUX[3:0]-Bits auf “1000”

aktiviert den Temperatursensor.

Die interne 1,1-V-Spannungsreferenz muss dazu als Spannungsreferenz

für den A/D-Wandler ausgewählt sein.

Ist der Temperatursensor ausgewählt, kann der A/D-Wandler im Einzelbetrieb

die Spannung über den Sensor messen.

Die gemessene Spannung hat einen linearen Zusammenhang zur Chiptemperatur

mit den in Tabelle 24-2 angegebenen Stützstellen.

Die Empfindlichkeit liegt bei 1 mV/K und die Genauigkeit bei ±10 °C.

Tabelle 24-2: Spannungsreferenz-Auswahl für den ADU

| Temperatur | -45 °C | +25 °C | +85 °C

|

|---|

| Spannung | 242 mV | 314 mV | 380 mV

|

| ADC-Wert (rechtsbündig) | 225 | 292 | 353

|

Die Spannungen in Tabelle 24-2 sind typische Werte.

Die Ausgangsspannung variiert von Chip zu Chip.

Um präzisere Temperaturwerte zu erhalten, kann die Temperaturausgabe

kalibriert werden.

Die Software-Kalibrierung erfordert, dass ein Kalibrierwert

(als Nullpunkt) im EEPROM für jeden Chip

beim Produktionstest gespeichert werden.

Die Kalibrierung kann folgende Formel verwenden:

T = (ADC – TOS) · k

wobei ADC das 16-bit-ADU-Datenregister, k ein fester Koeffizient

und TOS den Kalibrierwert darstellt, der im EEPROM als Teil

der Produktions-Endkontrolle abgespeichert wurde.

24.9 Register-Beschreibung

24.9.1 ADMUX — A/D-Multiplexer

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x7C) | REFS1 | REFS0 | ADLAR | - | MUX3 | MUX2 | MUX1 | MUX0 | ADMUX

|

|---|

| Zugriff | R/W | R/W | R/W | R | R/W | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

- Bit 7:6 — REFS[1:0]: Referenzauswahl

Mit diesen Bits wird die Spannungsreferenz für den ADU ausgewählt.

Wenn diese Bits während einer laufenden Wandlung gewechselt werden,

wird der Wechsel nicht während der laufenden Wandlung wirksam

sondern erst dann, wenn ADIF im ADCSRA gesetzt wird.

Die interne Referenzspannungsoptionen können nicht verwendet werden,

wenn eine externe Referenzspannung am AREF-Pin angeschlossen ist.

Tabelle 24-3: Spannungsreferenz-Auswahl für den ADU

| REFS1 | REFS0 | Auswahl der Referenzspannung

|

|---|

| 0 | 0 | AREF, interne UREF ist abgeschaltet

|

| 0 | 1 | AUCC mit externem Kondensator am AREF-Pin

|

| 1 | 0 | reserviert

|

| 1 | 1 | Interne Referenzspannung 1,1 V mit externem Kondensator an AREF-Pin

|

- Bit 5 — ADLAR: Linksausrichtung des Wandlungsergebnisses

Mit diesen Bit wird eingestellt, wie das Wandlungsergebnis in den beiden ADC-Datenbytes abgelegt wird.

Wenn das Bit gesetzt ist, wird das Ergebnis linksbündig abgelegt,

andernfalls wird es rechtsbündig abgelegt.

Das Ändern des Bits wirkt sich sofort auf die ADC-Data-Register aus,

unabhängig davon, ob gerade noch eine Wandlung läuft.

Siehe Beschreibung von ADCH und ADCL.

Dieses Bit ist ungenutzt und wird immer als 0 gelesen.

- Bit 3:0 — MUX[3:0]: Auswahl des Analogeingangs

Dieses Bit legen fest, welcher analoge Eingang mit dem ADU verbunden ist.

Siehe folgende Tabelle.

Werden diese Bits verändert, während eine Wandlung noch läuft,

so wirken sich die Änderungen erst nach Abschluss der laufenden Wandlung aus

(wenn ADIF im ADCSRA gesetzt wird).

Tabelle 24-4: Eingangskanal-Auswahl

| MUX[3:0] | Unsymmetrischer Eingang

|

|---|

| 0000 | ADC0

|

| 0001 | ADC1

|

| 0010 | ADC2

|

| 0011 | ADC3

|

| 0100 | ADC4

|

| 0101 | ADC5

|

| 0110 | ADC6

|

| 0111 | ADC7

|

| 1000 | ADC8(1)

| 1001 | reserviert

| | 1010 | reserviert

| | 1011 | reserviert

| | 1100 | reserviert

| | 1101 | reserviert

| | 1110 | 1,1 V (UBG)

| | 1111 | 0 V (Masse)

| |

- Hinweis:

- Für den Temperatursensor

24.9.2 ADCSRA — Kontroll- und Statusregister A

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x7A) | ADEN | ADSC | ADATE | ADIF | ADIE | ADPS2 | ADPS1 | ADPS0 | ADCSRA

|

|---|

| Zugriff | R/W | R/W | R/W | R/W! | R/W | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

- Bit 7 — ADEN: ADU-Freigabe

Mit einer 1 in diesem Bit wird der ADU freigegeben.

Durch Löschen des Bits wird der ADU gesperrt.

Wird das Bit während einer laufenden Wandlung gelöscht,

wird diese Wandlung abgebrochen.

- Bit 6 — ADSC: Wandlung starten

Im Betriebsart Einzelwandlung muss dieses Bit zum Starten jeder einzelnen Wandlung gesetzt werden.

Wenn die Wandlung abgeschlossen ist, wird das Bit automatisch wieder gelöscht.

Im Betriebsart fortlaufende Wandlung startet das Setzen des Bits die erste Wandlung.

Die erste Wandlung nach dem Beschreiben des ADSC,

nachdem der ADC freigegeben wurde,

oder wenn das ADSC gleichzeitig mit der Freigabe des ADC beschrieben wird,

benötigt 25 ADU-Takte, ansosnten 13 Takte.

Das ADSC-Bit wird so lange als 1 gelesen, wie eine Wandlung andauert.

Nach dem Abschluss einer Wandlung wird das Bit automatisch wieder auf Null gesetzt.

Das Schreiben einer Null in dieses Bit hat keine Auswirkungen.

- Bit 5 — ADFR: Automatische Triggerung

Wenn dieses Bit gesetzt ist, arbeitet der ADU mit automatischer Triggerung.

Eine Wandlung startet bei positiver Flanke des Triggersignals.

Die Triggerquelle wird mit den ADTS-Bits im ADCSRB ausgewählt.

In der Standardeinstellung von ADCSRB wird die

kontinuierliche Betriebsart des ADU aktiviert, wie bei vorhergehenden

AVR-Controllern ohne Triggerauswahl.

Das Löschen des Bits stoppt die weitere Wandlung.

- Bit 4 — ADIF: ADU-Interrupt anhängig

Dieses Bit wird gesetzt, wenn eine Wandlung abgeschlossen und die Daten-Register aktualisiert wurden.

Der ADU-Wandlung-komplett-Interrupt wird ausgeführt,

wenn das ADIE-Bit und das globale Interrupt-Bit (I-Bit im SREG) gesetzt sind.

ADIF wird durch die Hardware gelöscht, wenn die Interrupt-Routine ausgeführt wird.

Alternativ kann das ADIF-Bit auch gelöscht werden,

indem man eine logische 1 in das Flag schreibt.

Dies ist besonders zu beachten, wenn man eine Lese-Ändern-Schreiben-Befehlsfolge

mit dem ADCSR durchführt, da dadurch ein anhängiger Interrupt gelöscht werden kann.

Das kann auch geschehen, wenn die Befehle SBI und CBI verwendet werden.

Hierbei würde man eine 1 im ADIF zurücklesen,

irgendein anderes Bit ändern und das ganze Byte zurückschreiben.

Die 1 im ADIF führt dann zum Löschen des Interruptflags

und damit zur unbeabsichtigten Quittierung der Interruptanforderung.

- Bit 3 — ADIE: ADU-Interruptfreigabe

Wenn dieses Bit gesetzt wird und auch das I-Bit im SREG die Interrupts global freigibt, dann ist der ADC Conversion Complete Interrupt freigegeben.

- Bit 2:0 — ADPS[2:0]: ADU-Taktvorteilerauswahl

Diese Bits legen den Teilungsfaktor des Vorteilers fest,

der aus der Systemtaktfrequenz den ADU-Takt ableitet.

Tabelle 24-5: Vorteiler-Auswahl

| ADPS2 | ADPS1 | ADPS0 | Teilungsfaktor

|

|---|

| 0 | 0 | 0 | 2

|

| 0 | 0 | 1 | 2

|

| 0 | 1 | 0 | 4

|

| 0 | 1 | 1 | 8

|

| 1 | 0 | 0 | 16

|

| 1 | 0 | 1 | 32

|

| 1 | 1 | 0 | 64

|

| 1 | 1 | 1 | 128

|

24.9.3 ADC (ADCL+ADCH) — Ergebnisregister

24.9.3.1 Bei ADLAR = 0

| Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8

|

| (0x79) | - | - | - | - | - | - | ADC9 | ADC8 | ADCH

|

|---|

| (0x78) | ADC7 | ADC6 | ADC5 | ADC4 | ADC3 | ADC2 | ADC1 | ADC0 | ADCL

|

|---|

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| Zugriff | R | R | R | R | R | R | R | R

|

| R | R | R | R | R | R | R | R

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

24.9.3.2 Bei ADLAR = 1

| Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8

|

| (0x79) | ADC9 | ADC8 | ADC7 | ADC6 | ADC5 | ADC4 | ADC3 | ADC2 | ADCH

|

|---|

| (0x78) | ADC1 | ADC0 | - | - | - | - | - | - | ADCL

|

|---|

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| Zugriff | R | R | R | R | R | R | R | R

|

| R | R | R | R | R | R | R | R

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

Wenn eine ADC-Wandlung abgeschlossen wurde,

wird das Ergebnis in den beiden Registern ADCL und ADCH abgelegt.

Wenn das ADCL-Register gelesen wurde, werden beide Register so lange nicht

mit Werten neuerer Wandlungen aktualisiert, bis auch das ADCH gelesen wurde.

Wenn das Ergebnis linksbündig eingetragen ist und eine Auflösung von 8 Bit ausreichend ist,

dann ist es sinnvoll, nur ADCH auszulesen.

Andernfalls muss ADCL als erstes gelesen werden und anschließend ADCH.

Mit gesetztem ADLAR-Bit im ADMUX Register wird Linksbündigkeit eingestellt.

Ist es gelöscht (= Vorgabe), ist das Ergebnis rechtsbündig.

Beim Zugriff auf die volatile 16-Bit-Variable ADC im C-Programm

stellt der Compiler die richtige Zugriffsreihenfolge sicher.

- Bits ADC[9:0]: ADU-Wandlungsergebnis

Diese Bits repräsentieren das Ergebnis der Analog-Digital-Wandlung,

siehe oben.

24.9.4 ADCSRB — Kontroll- und Statusregister B

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x7B) | - | ACME | - | - | - | ADTS2 | ADTS1 | ADTS0 | ADCSRB

|

|---|

| Zugriff | R | R/W | R | R | R | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

Diese Bits sind für künftige Verwendung reserviert und sollten stets mit Null beschrieben werden.

- Bit 2:0 — ADTS[2:0]: Automatische Triggerquelle für den ADU

Wenn ADATE im ADCSRA auf Eins gesetzt wurde, wählen diese Bits die Triggerquelle für den A/D-Umsetzung aus.

Ist ADATE gelöscht, sind diese Bits ohne Wirkung.

Eine Wandlung wird durch eine steigende Flanke der ausgewählten Interruptanforderung ausgelöst.

Das Umschalten von einer gelöschten zu einer gesetzten Triggerquelle

bildet ebenfalls eine steigende Flanke des Triggersignals.

Ist ADEN in ADCSRA gesetzt, startet dies eine A/D-Wandlung.

Die Umschaltung zum kontinuierlichen Betrieb löst kein Triggerereignis aus,

selbst wenn die ADU-Interruptanforderung gesetzt ist.

Tabelle 24-6: Triggerquellen-Auswahl

| ADTS2 | ADTS1 | ADTS0 | Triggerquelle

|

|---|

| 0 | 0 | 0 | Kontinuierlicher Betrieb

|

| 0 | 0 | 1 | Analogvergleicher

|

| 0 | 1 | 0 | Externer Interrupt 0

|

| 0 | 1 | 1 | Zähler/Zeitgeber 0 Compare Match A

|

| 1 | 0 | 0 | Zähler/Zeitgeber 0 Überlauf

|

| 1 | 0 | 1 | Zähler/Zeitgeber 1 Compare Match B

|

| 1 | 1 | 0 | Zähler/Zeitgeber 1 Überlauf

|

| 1 | 1 | 1 | Zähler/Zeitgeber 1 Capture-Ereignis

|

24.9.5 DIDR0 — Abschalten digitaler Eingänge

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0

|

| (0x7E) | - | - | ADC5D | ADC4D | ADC3D | ADC2D | ADC1D | ADC0D | DIDR0

|

|---|

| Zugriff | R | R | R/W | R/W | R/W | R/W | R/W | R/W

|

| Startwert | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0

|

Diese Bits sind für künftige Verwendung reserviert und sollten stets mit Null beschrieben werden.

- Bit 5:0 — ADC[5:0]D: Abschalten des zugehörigen digitalen Eingangs

Wenn das Bit logisch Eins ist, wird der digitale Eingangspuffer des zugehörigen Anschlusspins abgeschaltet.

In Folge liest das PIN-Register stets ein Null-Bit.

Wird ein analoges Eingangssignal an ADC5:0 angeschlossen

und die digitale Eingangsfunktion nicht benötigt,

sollte dieses Bit auf logisch Eins gesetzt werden,

um die Stromaufnahme des digitalen Eingangspuffers zu reduzieren.

Die Eingänge ADC7 und ADC6 haben keine digitalen Eingangsfunktionen.

Daher benötigen diese keine Digital-Eingangs-Abschalt-Bits.