Hier gibt's nichts zu basteln!

Sondern um den Betrieb des Conitec-Programmiergerätes:

Eagle-Schaltplan GALEP-III. Hieraus wird ersichtlich, warum die Chips so komisch in die Fassung müssen: Die Verteilung der Pins mit den Fähigkeiten Masse (L), Speisespannung (H) und Programmierspannung (P) ist wild verteilt. Wobei (H) und (P) die Rollen tauschen können. Es ist — ohne gesonderte Selektionsleitungen — eine Trickschaltung, dass bei anliegender Programmierspannung über 5 V an einem der Pins der kleine Xilinx-FPGA vom Typ XC3142A mit dem Chip über die vielen MOSFETs vom Typ BSS138 bidirektional kommunizieren kann, ohne Schaden zu nehmen. Die Schieberegister IC2..IC5 sind ausgefallene Spezialtypen mit Hochspannungs-Ausgängen, gemeint sind mehr als 5 V, hier mindestens 25 V. Die Zuschaltung von Speise- und Programmierspannung erfolgt über Transfergates (svw. Analogsignalschalter) bestehend aus diskreten BSS138. Bei den Pins 11..14, die sowohl Programmier- als auch Speisespannung haben können, sind die Transfergates aus jeweils 2 Source an Source geschalteten BSS138 realisiert; ebenfalls eine Trickschaltung. Die Platinen sind vierlagig, mit einer dritten Signalebene und einer Masseebene im Innern. Aus dem Schaltplan erschließen sich Lösungsmöglichkeiten für einen künftigen USB-Adapter, der auch noch schnell ist.

Der FPGA wird beim Detektieren und Programmieren mit Slave-Serial synchron-seriell via Parallelport mit dem Bitstrom „betankt“ (30784 Bits). Deshalb geht es mit meinem USB2LPT so unerträglich langsam.

Funktionell und zertifiziert (150514): glpntdrv.zip. Läuft prima!

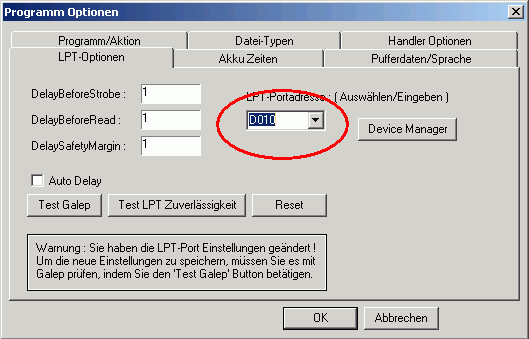

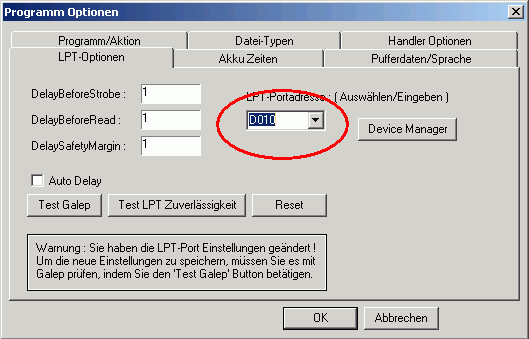

Der Treiber ist exakt wie in der Readme-Datei einzurichten. Beachten Sie unbedingt, dass Sie ein 64-Bit-Programm zum Kopieren verwenden!! Dies kann man ersehen:

Auf manchen Rechnern wird der Treiber mit der Meldung abgelehnt, dass das Zertifikat ungültig ist. Auf dem Rechner müssen die entsprechenden Kreuzzertifikate installiert sein. Bei Windows 7 ist dies das Update KB3033929. In derartigen Fällen hilft es nur, den PC über mehrere Tage online am Internet laufen zu lassen. Windows findet so immer wieder Updates, bis schließlich das o.g. Update gezogen wird.

(Information von Comodo.com sowie J. Strunk.)

Unter Windows 10 scheint es eine kleine Änderung gegeben zu haben: Zum Starten des Treibers („sc start glpntdrv“) sind Administrator-Rechte erforderlich. Entweder man startet galep32.exe als Administrator, oder führt „sc start glpntdrv“ manuell als Administrator aus.

Man kann auch im User Mode bleiben, um aufs Parallelport zuzugreifen. Das ist der Schlüssel für die Lauffähigkeit unter Linux (Wine) sowie mit USB-Adaptern.

Zu tun.

Die beim Programm galep32.exe vorhandene DLL namens glpwow.dll (steht für Galep-Windows-on-Win32) ist ein einfacher Wrapper für die glpntdrv.sys. Diese stellt für die verschiedenen zeitkritischen Funktionen, die im Kernel-Treiber realisiert sind, normale DLL-Einsprungpunkte mit Namen zur Verfügung. Da die Funktion des Kernel-Treibers bekannt ist, kann man die zeitkritischen Routinen auch in einem einfachen USB-Mikrocontroller ablaufen lassen. Dazu ist nur dieser Wrapper zu ändern, für Linux mit Kode, der aus Wine heraus zum USB-Gerät durchgreift.

Der erste Versuch, diesen Wrapper zu verstehen und neu zu schreiben, benutzt inpout32.dll, um aufs Parallelport zuzugreifen. Bis jetzt funktioniert die GALEP-Erkennung, aber noch nicht das Chip-Programmieren. Seltsamerweise ist diese Lösung immer noch recht langsam gegenüber dem USB2LPT. Zu tun ist noch (wenn Zeit):